# STATE VARIABLE HARMONIC BALANCE ANALYSIS OF NONLINEAR CIRCUITS BASED ON WAVES

by

Ryan Gregory Bruce Plater

A Thesis

Presented to Lakehead University

in Partial Fulfilment of the Requirements for the

Degree of Master of Science

in

Electrical and Computer Engineering

Thunder Bay, Ontario, Canada September 17, 2010

## **Abstract**

Circuit simulation involving nonlinear elements can be a challenging task. From these challenges rises a demand for finding better and more efficient ways of solving such problems. This work provides a novel approach for performing harmonic balance (HB) analysis using the fREEDA circuit simulator. The proposed method is an extension of the method of multiple reflections for multiple ports. In addition the method is formulated in terms of power waves and state variables at the nonlinear devices. The HB problem is then solved using a procedure which resembles the signal propagation within the actual circuit. This method could be efficiently parallelized since it does not require a large matrix decompositions at each iteration.

Several approaches to improve convergence properties are investigated. The first involves adding capacitors in parallel with the nonlinear device ports, this allows the fixed-point iterations to always be convergent. These capacitors are only active in a separate time dimension and do not affect the steady-state solution. The harmonic balance solution is found when the transient response in this time dimension is extinguished. Another strategy to improve convergence is the combination of fixed-point iterations with the gradient descent method. The effect of a vector extrapolation method to accelerate convergence is also investigated. Simulation results for various strongly nonlinear circuits is presented.

This thesis covers the background of harmonic balance analysis, literature review, derivation of the proposed method, improvements, preliminary results, as well as future work.

Acknowledgements

I would like thank my supervisor Dr. Carlos E. Christoffersen for the tremendous support

and guidance throughout my graduate studies at Lakehead University. It is my privilege studying

with him and being a part of his research group.

I would also like to express my sincere thank you to the remaining faculty and staff of the

faculty of engineering for their support and teaching over the course of my studies. Another

thank you to my peers, colleagues, friends and family for their encouragement and support

throughout this process. Finally a special thank you to Muhammad Kabir for his help during my

research work.

Ryan Gregory Bruce Plater

rplater@lakeheadu.ca

iv

# **Table of Contents**

| Chapter 1                                                          | 1  |

|--------------------------------------------------------------------|----|

| Introduction                                                       |    |

| 1.1 Motivation and Objectives of This Study                        | 1  |

| 1.2 Thesis Overview                                                |    |

| Chapter 2                                                          | 4  |

| Literature Review                                                  | 4  |

| 2.1 Introduction                                                   | 4  |

| 2.2 Numerical Techniques.                                          | 5  |

| 2.2.1 Newton's Method.                                             | 5  |

| 2.2.2 Minimum Polynomial Extrapolation                             | 7  |

| 2.2.3 Gradient Descent                                             | 9  |

| 2.3 Basics of Waves                                                | 10 |

| 2.3.1 Voltage Wave                                                 | 11 |

| 2.3.2 Power Wave                                                   | 12 |

| 2.4 Harmonic Balance Formulation.                                  | 12 |

| 2.4.1 Conventional Harmonic Balance Equations                      | 13 |

| 2.4.2 Existing Harmonic Balance Techniques                         | 17 |

| 2.4.3 Optimization.                                                | 18 |

| 2.4.4 Relaxation Techniques                                        | 18 |

| 2.4.5 Newton Based Methods for Harmonic Balance                    | 22 |

| 2.4.6 Krylov-Subspace Methods.                                     | 23 |

| 2.4.7 Preconditioning.                                             |    |

| 2.5 The fREEDA Circuit Simulator.                                  |    |

| 2.5.1 fREEDA State Variable Formulation.                           | 25 |

| 2.5.2 fREEDA Architecture and Addition of New Simulation Technique | 27 |

| Chapter 3                                                          |    |

| Wave Based Harmonic Balance                                        |    |

| 3.1 Introduction.                                                  |    |

| 3.2 fREEDA Programing and Implementation.                          |    |

| 3.2.1 fREEDA Equation Formulation (Linear)                         |    |

| 3.2.2 fREEDA Equation Formulation (Nonlinear)                      |    |

| 3.2.3 Solution Methodology                                         | 37 |

| 3.2.4 Implementation in fREEDA                                     | 39 |

| 3.3 Convergence Analysis                                           | 44 |

| 3.3.1 Power Bound.                                                 |    |

| 3.4 Convergence Improvements.                                      |    |

| 3.4.1 Addition of Parallel Capacitors                              |    |

| 3.4.2 Extrapolation Techniques                                     |    |

| 3.4.3 Gradient Descent Method                                      |    |

| 3.4.4 Tolerance Stepping.                                          |    |

| 3.5 Wave HB as Preconditioner                                      |    |

| 3.6 Problems and Solutions.                                        | 55 |

| Chapter 4                                                         | 57  |

|-------------------------------------------------------------------|-----|

| Results                                                           |     |

| 4.1 Simulation Setup.                                             | 57  |

| 4.2 Simple Diode Circuit                                          | 58  |

| 4.2.1 Diode Simulation Setup and Results                          |     |

| 4.2.2 Diode Simulation Summary                                    |     |

| 4.3 Full Wave Rectifier                                           | 66  |

| 4.3.1 Full Wave Rectifier Simulation Setup and Results            | 66  |

| 4.3.2 Full Wave Rectifier Simulation Summary                      | 70  |

| 4.4 Charge Pump                                                   |     |

| 4.4.1 Charge Pump Simulation Setup and Results                    | 71  |

| 4.4.2 Charge Pump Simulation Summary                              | 75  |

| 4.5 MESFET Amplifier                                              | 75  |

| 4.5.1 MESFET Amplifier Simulation Setup and Results               | 76  |

| 4.5.2 MESFET Amplifier Simulation Summary                         | 79  |

| 4.6 Soliton Line                                                  | 80  |

| 4.6.1 Soliton Line Simulation Setup and Results                   | 81  |

| 4.6.2 Soliton Line Simulation Summary                             | 85  |

| 4.7 Wave HB as a Preconditioner                                   | 86  |

| 4.7.1 Soliton Line with Wave HB as a Preconditioner               | 86  |

| 4.7.2 Multiple Soliton Line with Wave HB as a Preconditioner      |     |

| 4.7.3 Wave HB as a Preconditioner Summary                         | 89  |

| 4.8 Performance Comparisons.                                      | 90  |

| Chapter 5                                                         | 92  |

| Conclusion                                                        | 92  |

| 5.1 Conclusion                                                    |     |

| 5.2 Future Research.                                              | 93  |

| Appendices                                                        |     |

| Appendix A                                                        |     |

| Appendix A.1 Simple Diode Circuit Netlist                         |     |

| Appendix A.2 Full Wave Rectifier Circuit Netlist                  |     |

| Appendix A.3 Charge Pump Circuit Netlist                          |     |

| Appendix A.4 MESFET Amplifier Circuit Netlist                     |     |

| Appendix A.5 Soliton Line Circuit Netlist                         |     |

| Appendix A.5 Multiple Soliton Line Circuit Netlist                |     |

| Appendix B                                                        |     |

| Appendix B.1 Extrapolation Results of Simple Diode Circuit        |     |

| Appendix B.2 Extrapolation Results of Full Wave Rectifier Circuit |     |

| Appendix B.3 Extrapolation Results of Charge Pump Circuit         |     |

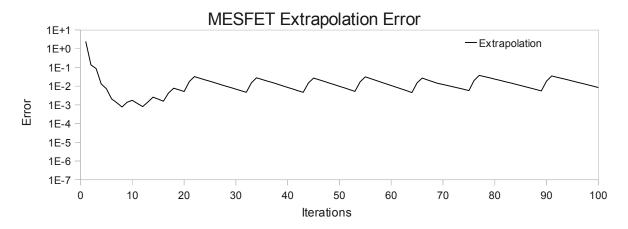

| Appendix B.4 Extrapolation Results of MESFET Amplifier Circuit    |     |

| References                                                        | 110 |

# **List of Figures**

| Fig. 2.1 Lossless Transmission Line                                                          | 10 |

|----------------------------------------------------------------------------------------------|----|

| Fig. 2.2 Harmonic Balance General Partitioning                                               | 13 |

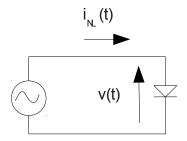

| Fig. 2.3 Simple Diode Circuit.                                                               |    |

| Fig. 2.4 Linear Sub-Circuit (ILIN)                                                           | 16 |

| Fig. 2.5 Nonlinear Sub-Circuit (INL)                                                         |    |

| Fig. 2.6 Kerr's Circuit Partitioning.                                                        | 19 |

| Fig. 2.7 Hicks and Khan Circuit Partitioning.                                                | 19 |

| Fig. 2.8 Identity Networks (a) Voltage Update Method (b) Current Update Method               | 21 |

| Fig. 2.9 fREEDA Circuit Partition.                                                           | 28 |

| Fig. 2.10 Circuit Partition Used in This Thesis                                              | 29 |

| Fig. 2.11 Example Netlist.                                                                   |    |

| Fig. 3.1 Partition with Fictitious Transmission Lines and Power Waves                        | 33 |

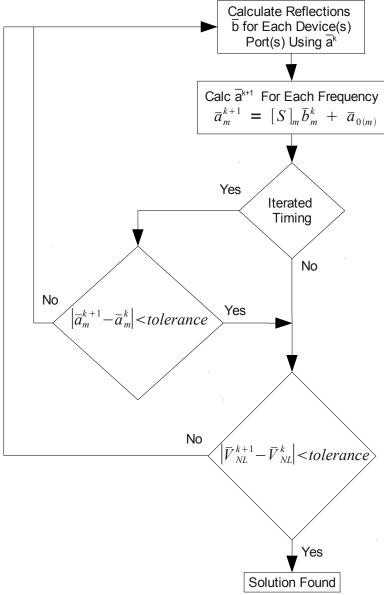

| Fig. 3.2 Solution Iteration Process                                                          | 39 |

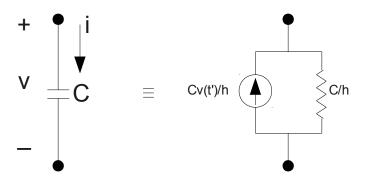

| Fig. 3.3 Addition of Parallel Port Capacitors                                                | 46 |

| Fig. 3.4 Capacitor Transformed into Equivalent Circuit                                       | 47 |

| Fig. 3.5 Pseudo Transient Flow Solution Flow Diagram                                         | 50 |

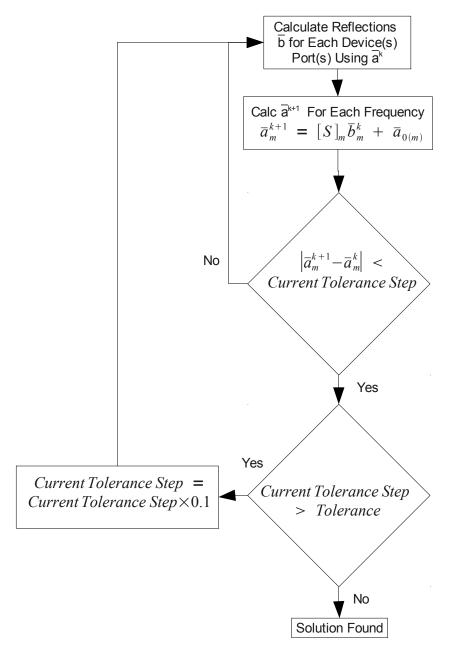

| Fig. 3.6 Tolerance Stepping Flow Diagram                                                     | 54 |

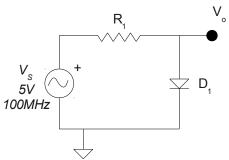

| Fig. 4.1 Resistor Diode Circuit.                                                             | 59 |

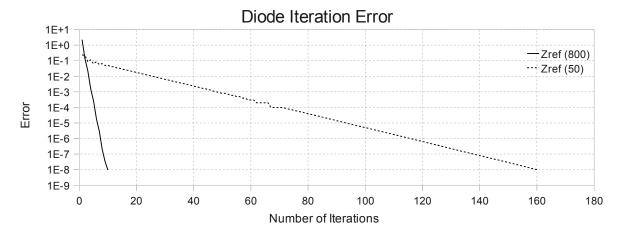

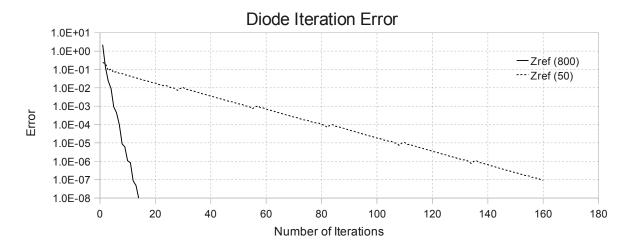

| Fig. 4.2 Comparison of Different Characteristic Impedances Effect on Iterations for Resistor |    |

| Diode Circuit                                                                                | 60 |

| Fig. 4.3 Comparison of Different Characteristic Impedances using Tolerance Stepping          | 61 |

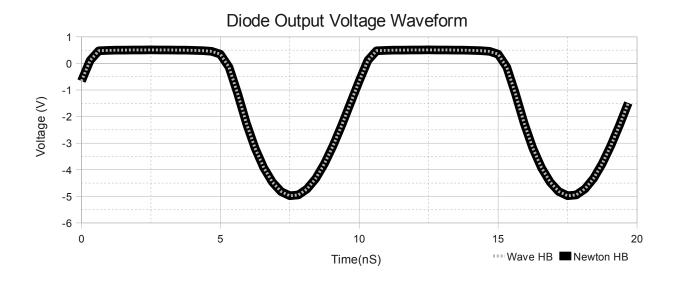

| Fig. 4.4 Simulated Voltage Waveform Across Diode                                             | 62 |

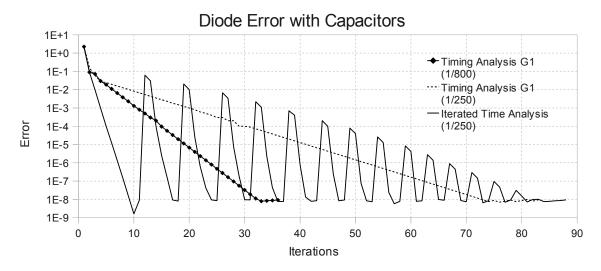

| Fig. 4.5 Iteration Error Function of Resistor Diode Circuit using Capacitors                 | 62 |

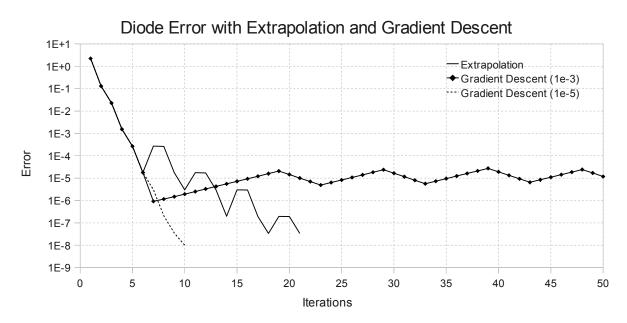

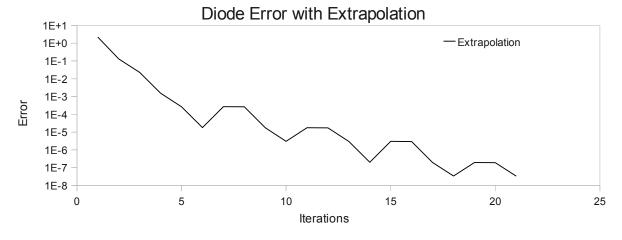

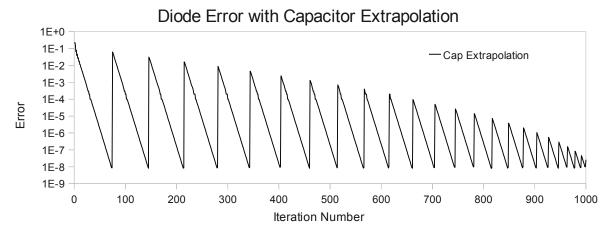

| Fig. 4.6 Gradient Descent and Extrapolation Error.                                           | 64 |

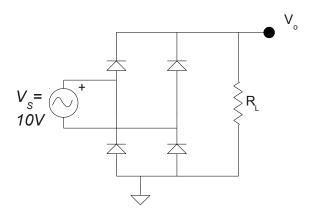

| Fig. 4.7 Rectifier Schematic.                                                                |    |

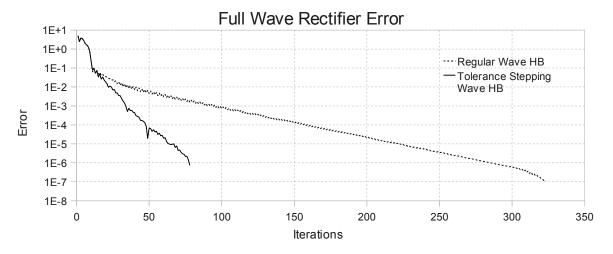

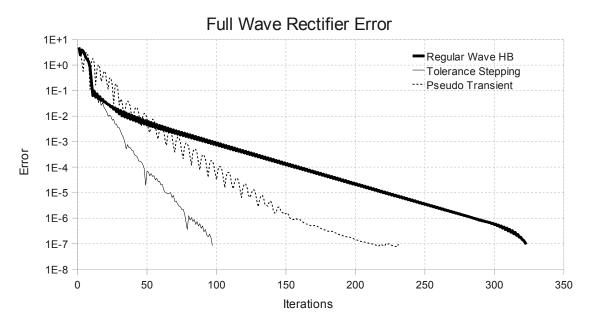

| Fig. 4.8 Wave HB Error as Function of Iterations                                             | 67 |

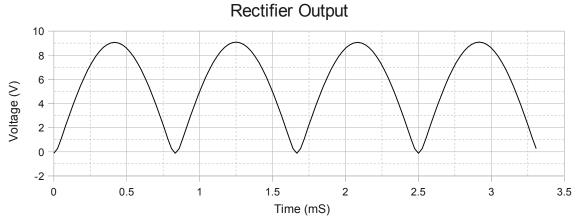

| Fig. 4.9 Simulated Voltage Output Waveform (Wave HB)                                         | 68 |

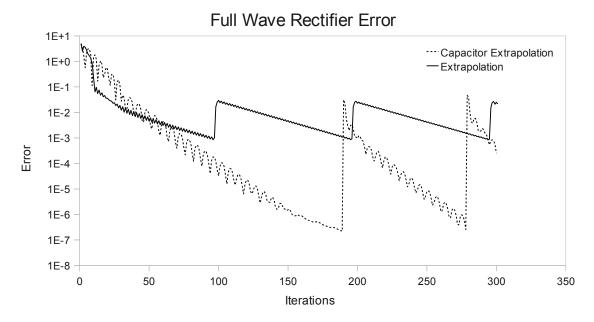

| Fig. 4.10 Pseudo Transient Compared with Wave and Newton-based HB                            | 69 |

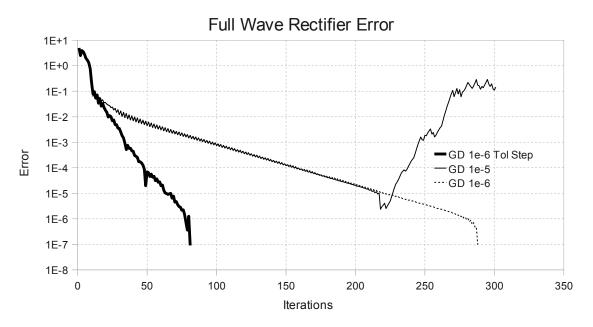

| Fig. 4.11 Gradient Descent Error                                                             | 70 |

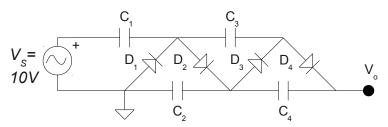

| Fig. 4.12 Charge Pump Schematic                                                              | 71 |

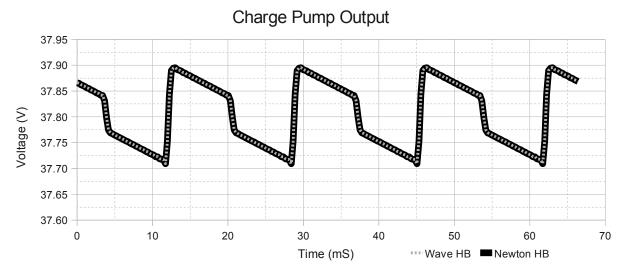

| Fig. 4.13 Charge Pump Voltage Output Waveform                                                |    |

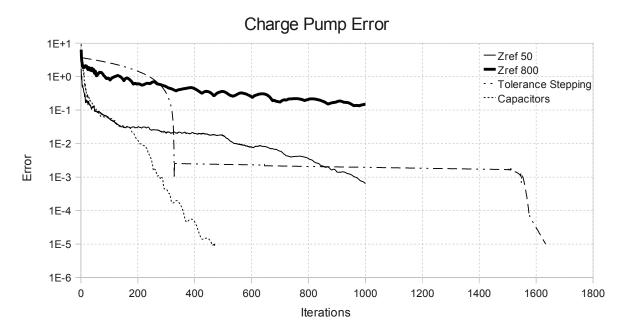

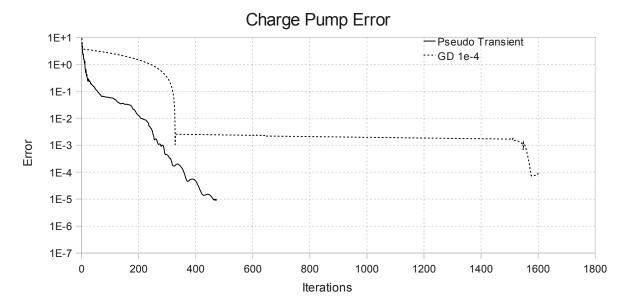

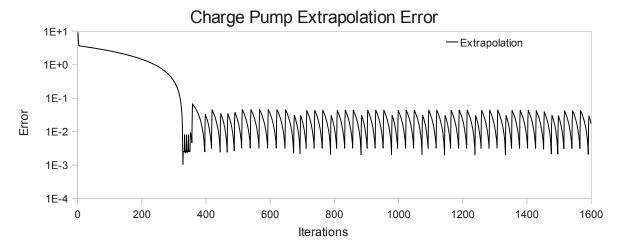

| Fig. 4.14 Wave HB, Tolerance Stepping and Pseudo Transient Iteration Error Results           | 73 |

| Fig. 4.15 Extrapolation and Gradient Descent Error Compared to Pseudo Transient              | 74 |

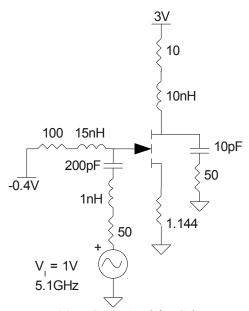

| Fig. 4.16 MESFET Amplifier Schematic                                                         | 75 |

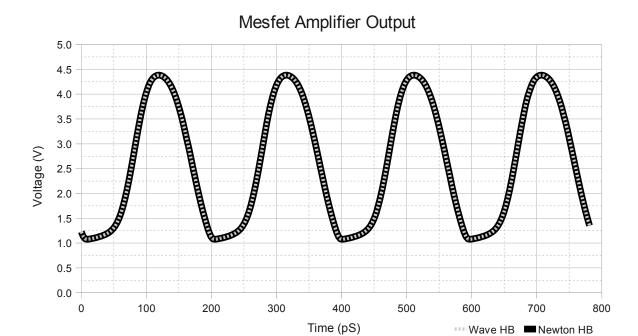

| Fig. 4.17 Simulated Solution Waveform                                                        |    |

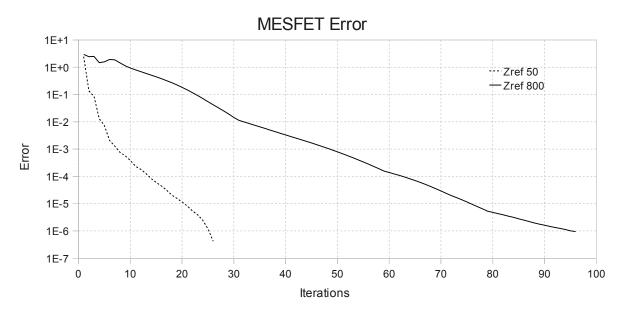

| Fig. 4.18 Characteristic Impedance Effect on Convergence                                     | 77 |

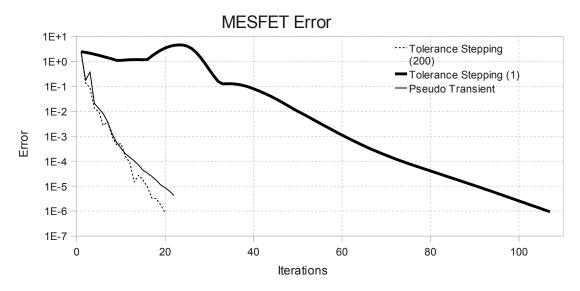

| Fig. 4.19 Simulation Iteration Error                                                         |    |

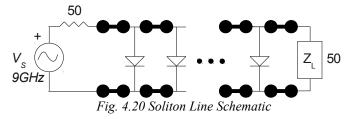

| Fig. 4.20 Soliton Line Schematic                                                             | 80 |

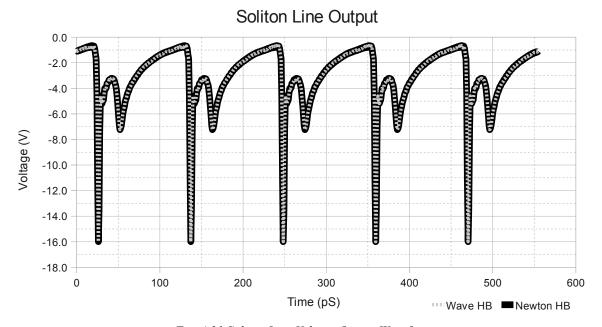

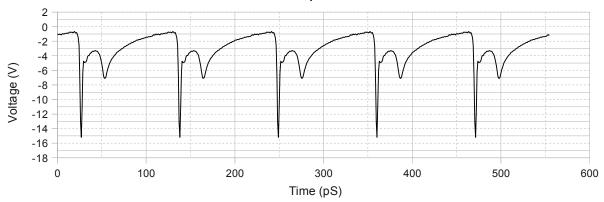

| Fig. 4.21 Soliton Line Voltage Output Waveform                                               |    |

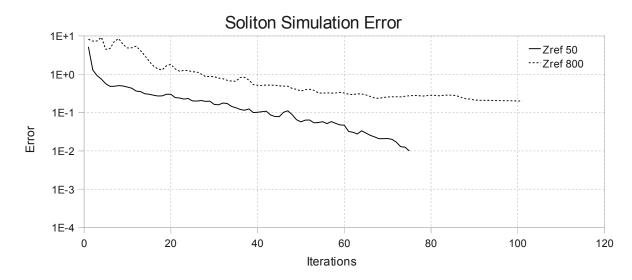

| Fig. 4.22 Characteristic Impedances Effect on Convergence                                    |    |

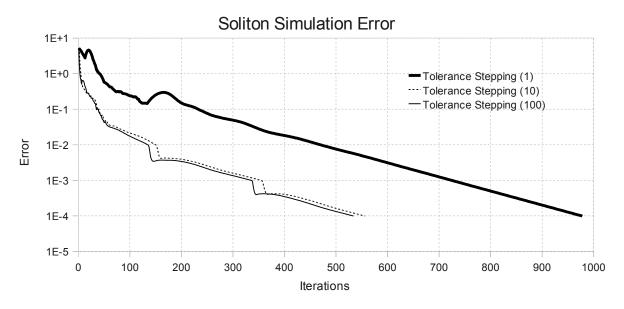

| Fig. 4.23 Comparison of Tolerance Stepping and Max Port Iteration Setting                    |    |

| Fig. 4.24 Soliton Output Waveform 1e-2 Solution Tolerance                                    | 87 |

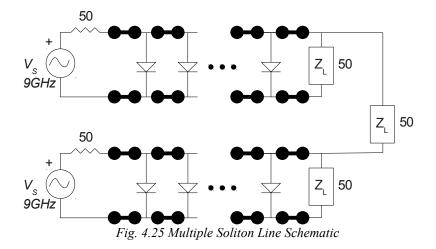

| Fig. 4.25 Multiple Soliton Line Schematic           | 88  |

|-----------------------------------------------------|-----|

| Fig. B.1 Extrapolation on Reflected Wave            | 106 |

| Fig. B.2 Capacitor Extrapolation                    | 107 |

| Fig. B.3 Capacitor and Reflected Wave Extrapolation |     |

| Fig. B.4 Extrapolation on Reflected Wave            |     |

| Fig. B.5 Extrapolation on Reflected Wave            | 109 |

# **List of Tables**

| Table 4.1 Simulation Setup Table Definitions                                 | 58  |

|------------------------------------------------------------------------------|-----|

| Table 4.2 Wave HB Simulation Setup and Results                               | 59  |

| Table 4.3 Tolerance Stepping Setup                                           | 61  |

| Table 4.4 Simulation Setup and Results                                       | 63  |

| Table 4.5 Gradient Descent and Extrapolation Setup and Results               | 65  |

| Table 4.6 Wave HB Simulation Setup.                                          | 67  |

| Table 4.7 Pseudo Transient Compared with Wave and Newton-based HB            |     |

| Table 4.8 Gradient Descent Setup and Results                                 | 69  |

| Table 4.9 Simulation Setup and Results                                       | 72  |

| Table 4.10 Extrapolation and Gradient Descent Compared to 'Pseudo Transient' | 74  |

| Table 4.11 MESFET Amplifier Wave HB Simulation Setup and Results             | 77  |

| Table 4.12 MESFET Amplifier Tolerance Stepping Simulation Setup and Results  | 78  |

| Table 4.13 Characteristic Impedance Comparison                               | 81  |

| Table 4.14 Different Tolerance Comparisons.                                  | 82  |

| Table 4.15 Tolerance Stepping Simulation Setup and Results                   | 84  |

| Table 4.16 Comparison of Wave HB and Newton-based HB                         |     |

| Table 4.17 Soliton Line Wave HB as a Preconditioner Results                  | 87  |

| Table 4.18 Multiple Soliton Line Wave HB as a Preconditioner Results         |     |

| Table B.1 Simple Diode Extrapolation Setup                                   | 106 |

| Table B.2 Full Wave Rectifier Extrapolation Setup                            | 107 |

| Table B.3 Charge Pump Extrapolation Setup.                                   |     |

| Table B.4 MESFET Amplifier Extrapolation Setup                               | 109 |

# **List of Symbols**

| Symbol                                            | Meaning                                                              |

|---------------------------------------------------|----------------------------------------------------------------------|

|                                                   | Transmitted Power Wave Vector                                        |

| $rac{A}{ar{A}_0} \ ar{B}$                        | Source Power Vector                                                  |

| $ar{B}$                                           | Reflected Power Wave Vector                                          |

| $\overline{\mathcal{C}}_k$                        | Extrapolation Coefficient Vector                                     |

| d                                                 | Device Number                                                        |

| [D]                                               | Diagonal Matrix Containing $\sqrt{Z_{ref}}$ in the diagonal elements |

| $rac{ar{f}_i}{ar{f}_v}$                          | Current Error Vector                                                 |

| $\overline{f}_{v}$                                | Voltage Error Vector                                                 |

| $G_1$                                             | Parallel Conductance Value for 'Pseudo Transient'                    |

| $\nabla H$                                        | Gradient of H                                                        |

| $i_L$                                             | Time Domain Linear Port Current                                      |

| $I_{\tau}$                                        | Frequency Domain Linear Port Current                                 |

| $\overline{i}_{NL}$                               | Time Domain Nonlinear Port Current                                   |

| $\overline{I}_{N\!L}^{N\!L}$                      | Frequency Domain Nonlinear Port Current                              |

| $[J_{i}]$                                         | Current Jacobian Matrix                                              |

| $[J_v]$                                           | Voltage Jacobian Matrix                                              |

| k                                                 | Iteration Number                                                     |

| m                                                 | Harmonic Number                                                      |

| $[M_{_{SV}}]$                                     | Frequency Domain Modified Nodal Admittance Matrix                    |

| n                                                 | State Number                                                         |

| p                                                 | Port Number                                                          |

| $p_n$                                             | Convergence Parameter                                                |

| q                                                 | Time Domain Charge                                                   |

| $egin{array}{c} Q \ [S] \ ar{S}_{SV} \end{array}$ | Frequency Domain Charge                                              |

|                                                   | Scattering Parameter Matrix                                          |

|                                                   | Frequency Domain Source Vector                                       |

| $\bar{u}_k$                                       | Extrapolation Difference Vector                                      |

| $[U_k]$                                           | Extrapolation Difference Matrix                                      |

| ${oldsymbol{v}}_L$                                | Time Domain Linear Port Voltage                                      |

| $V_L$                                             | Frequency Domain Linear Port Voltage                                 |

| $\overline{oldsymbol{ u}}_{NL}$                   | Time Domain Nonlinear Port Voltage                                   |

| $\overline{V}_{N\!L}$                             | Frequency Domain Nonlinear Port Voltage                              |

| $\hat{x}$                                         | Estimate of Solution                                                 |

| $\overline{x}$                                    | Time Domain State Variable Vector                                    |

| $\bar{x}_{_D}$                                    | Time delay State Variable                                            |

| $\bar{X}$                                         | Frequency Domain State Variable Vector                               |

| [Y]                                               | Admittance Matrix                                                    |

| $Z_{\it ref}$                                     | Reference Transmission Line Characteristic Impedance                 |

| ${\mathcal F}$     | Fourier Transform                           |

|--------------------|---------------------------------------------|

| $\mathcal{F}^{-1}$ | Inverse Fourier Transform                   |

| $\Re$              | Real Part                                   |

| 3                  | Imaginary Part                              |

| $\Gamma$           | Reflection Coefficient                      |

| α                  | Nonlinear Port Newton Update Scaling Factor |

| $\omega$           | Frequency (rad/s)                           |

| $\Omega$           | Diagonal $\omega$ Matrix                    |

| $\Phi$             | Phase                                       |

| $	au_i$            | Time Delay                                  |

# **List of Abbreviations**

| Abbreviation | Meaning                                     |

|--------------|---------------------------------------------|

| AC           | Alternating Current                         |

| DC           | Direct Current                              |

| DFT          | Discrete Fourier Transform                  |

| FFT          | Fast Fourier Transform                      |

| GD           | Gradient Descent                            |

| <b>GMRES</b> | General Minimum Residual                    |

| HB           | Harmonic Balance                            |

| INHB         | Inexact Harmonic Balance                    |

| LAPACK       | Linear Algebra PACKage                      |

| LU           | Lower Upper (Matrix Decomposition )         |

| LNA          | Low Noise Amplifier                         |

| MESFET       | Metal Semiconductor Field Effect Transistor |

| MMIC         | Monolithic Microwave Integrated Circuit     |

| MPE          | Minimum Polynomial Extrapolation            |

| MTL          | Matrix Template Library                     |

| NL           | Nonlinear                                   |

| NA           | Not Applicable                              |

| RMS          | Root Mean Squared                           |

| SVHB         | State Variable Harmonic Balance             |

| Tol Step     | Tolerance Stepping                          |

# Chapter 1

# Introduction

# 1.1 Motivation and Objectives of This Study

As technologies advance new possibilities emerge. With these advances the demand for faster, smaller and more complex designs occur. The electronics field is not exempt from this and may be one of the major driving forces in technology. From this stems the need for quicker and more efficient ways to design and simulate electronic circuit operation. There are two common approaches used for solving such problems. They are commonly divided into two broad groups being time and frequency based. There are various available approaches for implementing these two methods.

This thesis presents a harmonic balance (HB) approach using a relaxation technique based on the work performed by Kerr [3] and Hicks and Khan [4]. The idea draws from the multiple reflection technique of Kerr and considers a network partition similar to the approach proposed by Hicks and Khan. Transmission line theory and power waves are used to model the circuit operation along with various techniques to improve and control convergence. A rigorous extension using waves (unlike the extensions developed in References [9,12]) for solving harmonic balance analysis formulated using state variables for nonlinear circuit simulations is presented for the first time. Combining the use of power waves with the addition of parallel connected capacitors, extrapolation and gradient descent methods are also tested for the first time.

The basic existing harmonic balance techniques (discussed in Chapter 2) work well for circuits of smaller size and that demonstrate fairly linear characteristics. Krylov-subspace methods with inexact Newton harmonic balance using generalized minimum residual technique (GMRES) and preconditioning has demonstrated success for larger nonlinear circuits [2,5]. However there are limitations to these approaches in the size of problem which can be solved, convergence to the solution and CPU time. One of the major limitations of the harmonic balance approaches is convergence. Predicting convergence at the on set of a simulation can not be determined. A matrix preconditioner is used to improve the properties and initial guess of solving a system of equations. The use of a preconditioner can become a requirement for successful convergence and thus plays a crucial role in obtaining a successful solution [2]. These improvements still do not entirely overcome all of these limitations.

The proposal of using wave quantities, more specifically power waves, shows some promise. The use of waves closely represents the actual signal propagation during circuit operation. Iterative methods based on power waves can be made theoretically constrained to avoid the possibility of divergence.

The majority of techniques mentioned in Chapter 2 have been formulated using Kirchoff's voltage law and/or Kirchoff's current law to represent the circuit quantities. The proposed process is based on transmission line theory and the propagation of wave quantities, by using transmission lines to connect the linear and nonlinear sub-circuits together. The transmission lines have been selected to have a length of zero and thus have no effect on the circuit. The use of wave properties should allow for better convergence, the ability to easily divide the problem into smaller pieces and shows promise for parallelization which can take advantage of todays

multi-core and cluster computers.

## 1.2 Thesis Overview

This thesis covers the following topics. Chapter 2 begins with a brief introduction to the history of solving nonlinear circuits, followed by a review of basic concepts related to circuit simulation. The Harmonic balance concept is then introduced. Various present harmonic balance approaches are described. Finally the circuit simulator used to implement the techniques developed in the thesis is discussed.

Chapter 3 presents a new harmonic balance based technique based on waves. The main equations are derived first, followed by an analysis of convergence and some strategies to improve/accelerate convergence. Numerical simulations are presented in Chapter 4. The performance of the proposed methods is evaluated with the simulations of several circuits: Resistor Diode, Full Wave Rectifier, Charge Pump, MESFET Amplifier, and a Soliton line. Chapter 5 presents conclusions and suggested future research directions.

# Chapter 2

# Literature Review

### 2.1 Introduction

There are two main categories that most circuit simulation techniques fall into, those being time and frequency based. Time based circuit simulations such as transient analysis use small time steps to sample the circuit operation [2]. The use of frequency based methods implies that there is some advantage over time based methods for certain circuit solutions. One of such frequency based methods is harmonic balance.

Unlike transient analysis, harmonic balance calculates the steady state solution directly. This is accomplished by using a linear addition of sinusoids to produce the solution [1]. There have been many different approaches proposed to solve circuits using the harmonic balance technique. The conventional process used for harmonic balance is to divide the circuit up into two subnetworks comprised of the linear and nonlinear elements of the circuit [2]. The linear network can then be solved in the frequency domain and the nonlinear network solved for in the time domain. This being the reason that harmonic balance is sometimes referred to as a mixed domain method [1]. The name harmonic balance stems from the process where currents are balanced between the linear and non-linear sub-circuits [4]. The linear network is typically represented in the form of an admittance matrix (Y-parameters) [2]. Other representations such as the scattering matrix (S-parameters) have been proposed and show some promise with certain techniques [5,17].

As the number of elements in the circuit increase so does the number of unknowns and therefore the complexity in solving the system. There have been different proposed methods to help deal with these complexities when solving a system of equations. Details of some of these approaches will be discussed in the following sections. Section 2.2 presents numerical techniques that are used to solve the harmonic balance equations, such as Newton's method. The use of extrapolation and gradient descent techniques is also covered. The basics of voltage and power waves is discussed in Section 2.3. Section 2.4 discusses conventional and current harmonic balance techniques and various approaches to solve the harmonic balance equations. The solution approaches discussed included, optimization, relaxation techniques, Newton based methods, and the use of matrix preconditioners. Section 2.5 discusses the architecture of the fREEDA simulator and implementation of a new simulation technique.

# 2.2 Numerical Techniques

#### 2.2.1 Newton's Method

Newton's method more correctly referred to as the Newton-Raphson method is one of the most common numerical approaches used in todays computers to solve systems of nonlinear equations. It is especially powerful when it comes to solving complex systems with nonlinearities where conventional substitution methods are not possible or difficult [7]. Practically all of todays circuit simulation programs use some form of Newton based technique. Newton's method extrapolates to the axis of the independent variable using its first derivative [2].

Consider the system of nonlinear equations given by:

$$f_{1}(x_{1,}x_{2,...},x_{n}) = 0$$

$$f_{2}(x_{1,}x_{2,...},x_{n}) = 0$$

$$\vdots$$

$$f_{n}(x_{1,}x_{2,...},x_{n}) = 0$$

(2.1)

If the functions  $(f_1, f_2, ..., f_n)$  are expanded using a Taylor series about an arbitrary point  $(x_1, x_2, ..., x_n)$  and only the linear terms retained we can obtain exact solution values  $(\hat{x}_1, \hat{x}_2, ..., \hat{x}_n)$  [7]. Setting the equations defined from the Taylor series expansion equal to zero and defining a  $\Delta x_i$  term as the correction to the guess of  $x_i$ ,

$$\Delta x_i = \hat{x}_i - x_i \text{ where } (i = 1, 2, ..., n)$$

, (2.2)

can be formed. Rewriting the the Taylor series expansion in general form,

$$\begin{bmatrix} \frac{\partial f_1}{\partial x_1} & \frac{\partial f_1}{\partial x_2} & \cdots & \frac{\partial f_1}{\partial x_n} \\ \frac{\partial f_2}{\partial x_1} & \frac{\partial f_2}{\partial x_2} & \cdots & \frac{\partial f_2}{\partial x_n} \\ \vdots & \vdots & \ddots & \vdots \\ \frac{\partial f_n}{\partial x_1} & \frac{\partial f_n}{\partial x_2} & \cdots & \frac{\partial f_n}{\partial x_n} \end{bmatrix} \begin{bmatrix} \Delta x_1 \\ \Delta x_2 \\ \vdots \\ \Delta x_n \end{bmatrix} = \begin{bmatrix} -f_1 \\ -f_2 \\ \vdots \\ \vdots \\ -f_n \end{bmatrix}.$$

(2.3)

The matrix on the left of Equation (2.3) is referred to as the Jacobian and is calculated for each approximation of  $x_i$ . The use of the first order partial derivatives for each device and harmonic considered creates the Jacobian matrix. The Jacobian contains the maximum amount of information about the system and its error. With this large amount of information about the system good convergence characteristics can typically be achieved [2].

The  $\Delta x_i$  term is solved at each iteration (k) and the approximation of the solution  $x_i$  is updated by,

$$x_i^{k+1} = x_i^k + \Delta x_i^k \tag{2.4}$$

This process can be broken down into six main steps. First the initial guess is selected ( $x_i^0$ ), the function is evaluated at  $x_i^0$  and the partial derivatives are calculated to form the Jacobian matrix. The update  $\Delta x_i$  is solved, a new solution  $x_i^1$  is determined and checked for convergence to a solution. If convergence to a solution was achieved then the process is stopped otherwise it repeats using the newest approximate solution as the initial guess [7].

Newton's method is quite good at solving systems of this form. However this approach still does not guarantee convergence if the the initial guess is far from the solution. It also becomes impractical for solving very large systems of equations. This occurs because the Jacobian size becomes too large to directly factor efficiently, even in today's powerful computers [15]. These issues and limitations lead to modifications of Newton's method to help alleviate them as discussed in Section 2.3.

### 2.2.2 Minimum Polynomial Extrapolation

Minimum polynomial extrapolation (MPE) is a technique to find the fixed point (s) of a sequence of vectors which satisfies the system of equations. If the system in question is linear using a MPE will extrapolate to the fixed point. For systems which are nonlinear performing a MPE with enough samples has the ability to extrapolate to a solution relatively close to the correct one. Minimum polynomial extrapolation is based on using vector differences to calculate the solution [19].

Given a vector sequence  $\bar{x}_{1,}\bar{x}_{2,}\cdots,\bar{x}_{k+1}$  generated by an equation of the form:

$$\bar{x}_{j+1} = [A]\bar{x}_j + \bar{b}, \qquad j = 0, 1, 2, \cdots,$$

(2.5)

Where [A] is a fixed matrix and  $\bar{b}$  a fixed vector. Both [A] and  $\bar{b}$  do not necessarily have to be known, only that there is a way of generating  $\bar{x}_{1,}\bar{x}_{2,}\cdots,\bar{x}_{k+1}$  [19]. From an initial starting point of  $\bar{x}_{0}$  a sequence  $\bar{x}_{1,}\bar{x}_{2,}\cdots,\bar{x}_{k+1}$  is generated. Using a fixed amount of samples k, a  $N\times k$  matrix is formed, where the columns are the vectors of the vector differences:

$$\bar{u}_i = \Delta \bar{x}_i = \bar{x}_{i+1} - \bar{x}_i \tag{2.6}$$

$$[U] \equiv [U_k] = [\bar{u}_0, \bar{u}_1, \dots, \bar{u}_{k-1}] \tag{2.7}$$

Using the [U] matrix a coefficient c vector is defined to satisfy.

$$[U]\bar{c} = -\bar{u}_k \tag{2.8}$$

The values of  $\bar{c}$  are calculated using the following formula,

$$\bar{c} = -[U]^{\dagger} \bar{u}_k \quad , \tag{2.9}$$

where  $[U]^+$  is the Moore Penrose pseudo-inverse.

For any consecutive term sequence with a length of k+1 the fixed point (s) can be calculated [19] as follows,

$$\sum_{j=0}^{k} c_{j} x_{m+j} = \left( \sum_{j=0}^{k} c_{j} \right) s$$

(2.10)

with the *m* term being an offset within the generated sequence and  $c_k = 1$ . The conditions for a

successful extrapolation calculation requires that the fixed point exists and the number of samples k is equal or greater then the number of nonzero eigenvalues of the [U] matrix.

The outcome of using MPE on nonlinear equations can be incorrect if the selected sequence length k is too short, the generated sequence is far from the correct solution or the system of equations exhibits strong nonlinearity.

#### 2.2.3 Gradient Descent

Gradient descent is a first order optimization routine which can be used to find the local minima scalar field. During an iteration routine the gradient of the function is calculated and used to determine the direction of the update. The update is scaled toward the minimum of the function or proportionally to the negative of its gradient. Analogous to the descent method is gradient ascent which is used to find local maxima. Care must be taken when using gradient methods. Performing a gradient update on the system before being relatively close to solution can trap the iteration process at an incorrect result.

Given a function  $F(x^k)$  where at solution equals zero. The gradient of the function can be calculated if the function is defined and differentiable in the area around a selected solution point g [31]. The fastest way to decrease  $F(x^k)$  from a starting point of g is to move in the direction of the negative gradient or  $-\nabla F(g)$ . If

$$h = g - \gamma \nabla F(g) , \qquad (2.11)$$

for a value of y small enough, then  $F(g) \ge F(h)$ . From this observation and starting from an initial guess of  $x^0$  for a local minimum of the function  $F(x^k)$ . A generated sequence  $x^0, x^1, x^2, \dots$  can be calculated from:

$$x^{k+1} = x^k - y^k \nabla F(x^k) , k \ge 0 ,$$

(2.12)

such that  $F(x^0) \ge F(x^1) \ge F(x^2) \ge \dots$  which will hopefully converge to the local minimum. The value of  $\gamma$  is not necessarily the same for each iteration.

## 2.3 Basics of Waves

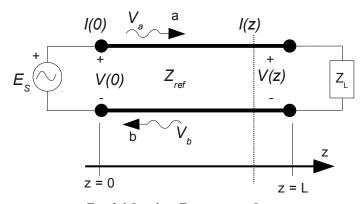

Consider the lossless transmission line in Fig. 2.1 with characteristic impedance  $Z_{ref}$ , terminating load impedance  $Z_L$  and sinusoidal voltage source  $E_S$ .

Fig. 2.1 Lossless Transmission Line

The sinusoidal wave produced by  $E_s$  and propagating in the positive z direction is reflected back in the negative z direction when it reaches the termination at z=L. The voltage and currents at any point along the transmission line consists of both positive and negative going waves. The voltage and current at any point along the transmission line consists of waves propagating along the positive and negative z direction:

$$V(z) = V_{a'} e^{-j\beta z} + V_{b'} e^{+j\beta z}$$

(2.13)

$$I(z) = \frac{V_{a'}}{Z_{ref}} e^{-j\beta z} - \frac{V_{b'}}{Z_{ref}} e^{+j\beta z}$$

(2.14)

The magnitudes of voltage in the positive and negative z direction are  $V_{a'}$  and  $V_{b'}$  respectively and  $\beta$  is the phase constant [8]. The ratio between the positive z direction propagating wave and the negative z direction propagating wave is referred to as the reflection coefficient  $\Gamma$  and is given by,

$$\Gamma = \frac{V_{b'}e^{+j\beta z}}{V_{a'}e^{-j\beta z}}$$

$$\Gamma = \frac{Z_L - Z_{ref}}{Z_L + Z_{ref}}$$

(2.15)

With  $V_a$  and  $V_b$  being the RMS values of traveling wave voltage, then  $|V_b| = \frac{|V_b|}{\sqrt{2}}$  and

$|V_a| = \frac{|V_a|}{\sqrt{2}}$ . The power flowing in the positive z direction is given by,

$$P = \frac{|V_a|^2}{Z_{ref}} - \frac{|V_b|^2}{Z_{ref}}$$

(2.16)

## 2.3.1 Voltage Wave

Given the length of the transmission line is L then the voltage and current at z = L is,

$$V(L) = V_{a'}e^{-j\beta L} + V_{b'}e^{+j\beta L}$$

$$I(L) = \frac{V_{a'}}{Z_{ref}} e^{-j\beta L} - \frac{V_{b'}}{Z_{ref}} e^{+j\beta L}$$

(2.17)

Setting the length of the transmission line equal to zero the voltage and current become,

$$V = V_{a'} + V_{b'} = \sqrt{2}(V_a + V_b)$$

(2.18)

and

$$I = \frac{V_{a'}}{Z_{ref}} - \frac{V_{b'}}{Z_{ref}}$$

$$= \frac{\sqrt{2}}{Z_{ref}} (V_a - V_b)$$

(2.19)

The use of a zero length transmission line allows the voltage and currents at any node to be converted to voltage waves. The use of voltage waves can then be used as parameters to formulate circuit analysis [8].

#### 2.3.2 Power Wave

The use of waves is not limited to just voltage. The circuit parameters can also be formulated using power waves. Considering 'a' as the positive propagating power wave and 'b'

as the negative propagating power wave in such a away that  $|a|^2 = \frac{|V_a|^2}{Z_{ref}}$  and  $|b|^2 = \frac{|V_b|^2}{Z_{ref}}$  in

$$V = \sqrt{Z_{ref}}(a + b) \tag{2.20}$$

and

$$I = \frac{1}{\sqrt{Z_{ref}}}(a - b) \tag{2.21}$$

The power wave equations (2.20) and (2.21) are the bases used throughout this work.

## 2.4 Harmonic Balance Formulation

(Fig. 2.1) [8]. The voltage and currents can be expressed as,

Early use of piecewise harmonic balance approach is demonstrated by Nakhla and Vlach [6]. The basis of piecewise harmonic balance is to separate the linear and nonlinear devices into two sub networks. Current and voltage equations are formed for the two ports. An error function

is formed by taking the difference between the currents and/or the voltages of the linear and nonlinear ports. Detailed equation formulation is presented next.

### 2.4.1 Conventional Harmonic Balance Equations

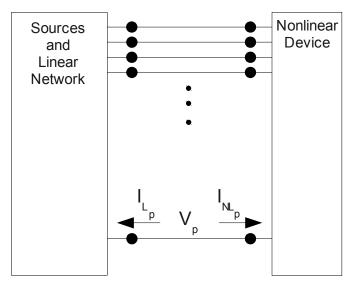

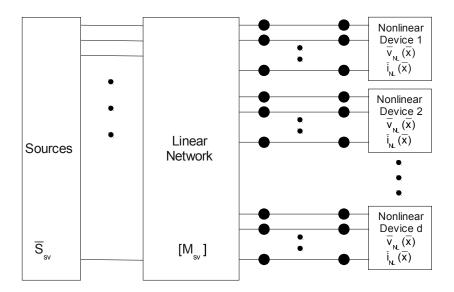

As mentioned above the idea is to partition the circuit into its linear and nonlinear components. This reduction allows the nonlinear sub-circuit to be solved independently of the linear sub-circuit. The linear network can then be solved directly in the frequency domain. While the nonlinear subnetwork element models can be solved in the time domain and subsequently converted to the frequency domain. This partitioning can be seen in Fig. 2.2.

Fig. 2.2 Harmonic Balance General Partitioning

The voltage and currents at each port (p) are assumed to be periodic having a period of

T which is defined as  $T = \frac{2\pi}{\omega}$  and  $\omega$  being the angular velocity. The voltage at port p can be expressed using the following equation:

$$v_p(t) = \Re \left\{ \sum_{k=0}^m V_k e^{(j\omega kt + \phi_k)} \right\} ,$$

(2.22)

where the unknown values are the amplitude  $V_k$  and phase  $\phi_k$  for each frequency.

The error function is formulated as the sum of the currents at the ports connecting the linear and nonlinear ports [2].

$$F(V) = I(V) + j\Omega Q(V) + YV + I_S = 0$$

(2.23)

where I(V) is the current from the nonlinear conductances or voltage-controlled sources and  $\Omega Q(V)$  is the current contribution from the nonlinear capacitors. These two terms together represent the current contribution by the nonlinear network ( $I_{N\!L}$ ). The  $\Omega$  symbol represents a diagonal matrix containing k  $\omega$  elements in the main diagonal,

$$\Omega = \begin{bmatrix}

0 & 0 & \cdots & \cdots & 0 \\

0 & \omega & \ddots & \cdots & 0 \\

\vdots & \vdots & 2\omega & \ddots & 0 \\

\vdots & \vdots & \ddots & \ddots & 0 \\

0 & 0 & \cdots & \cdots & m\omega

\end{bmatrix}$$

(2.24)

The  $I_S$  term is the current contribution from the circuit sources and YV is the current contribution from the linear elements. These two together represent the linear port current  $I_{LIN}$ . The name of harmonic balance is easily seen because a correct guess for V in Equation (2.23) will balance the linear and nonlinear currents for each Harmonic.

Consider just the nonlinear part from Equation (2.23). The nonlinear current contribution  $I_{\it NL}$  can be written as:

$$I_{NI}(V) = \mathcal{F}\{i[\mathcal{F}^{-1}(V)]\} + \Omega \mathcal{F}\{q[\mathcal{F}^{-1}(V)]\}$$

(2.25)

where  $\mathcal{F}$  and  $\mathcal{F}^{-1}$  are the Fourier and Inverse Fourier transforms and i() and q() represent the nonlinear currents and charge, respectively, in the time domain [2]. The estimate of voltage (V) in the frequency domain is converted into the time domain using Fourier transform. The nonlinear current  $i_{NL}$  is then solved for in the time domain. Using inverse Fourier transform  $i_{NL}$  is then converted back to the frequency domain and used to calculate the error F(V) [2].

For the correct selection of V in Equation (2.14) F(V) will be approximately zero. Due to the iterative technique used to solve such a problem, a solution is found when all elements of the F(V) vector are less than a defined tolerance.

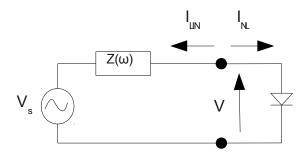

A simple harmonic balance example can be demonstrated using the circuit in Fig. 2.3. The source is made up of both a DC voltage and an AC fundamental frequency. First defining the linear current ( $I_{LIN}$ ), nonlinear current ( $I_{NL}$ ) and port voltage allows for easy equation setup.

Fig. 2.3 Simple Diode Circuit

The circuit is divided up into its two sub-circuits. Fig. 2.4 represents the linear sub-circuit in the frequency domain. The diode is replaced with the voltage seen at the terminals.

Fig. 2.4 Linear Sub-Circuit (I<sub>LIN</sub>)

Writing the equation for the linear current in the frequency domain Equation (2.26).

$$I_{LIN} = \frac{V(k\omega_p) - V_s(k\omega_p)}{Z(k\omega_p)}$$

(2.26)

Fig. 2.5 represents the nonlinear sub-circuit in the time domain.

Fig. 2.5 Nonlinear Sub-Circuit (I<sub>NL</sub>)

Writing the equation for the nonlinear current in the frequency domain is accomplished by first calculating the diode current in the time domain using,

$$i_{NL}(t) = i_{sat}(e^{\frac{v_{NL}(t)}{nv_T}} - 1)$$

(2.27)

where  $i_{sat}$  is the saturation current,  $v_T$  is the thermal voltage and n is the ideality factor of the diode. The error function for the circuit is given by,

$$I_{LIN}(k \omega_p) + I_{NL}(k \omega_p) = 0$$

(2.28)

Substituting the two currents into the error function Equation (2.28) and using Fourier transform to convert the nonlinear current into the frequency domain,

$$\frac{V(k\omega_p) - V_s(k\omega_p)}{Z(k\omega_p)} + \mathcal{F}[I_{sat}(e^{\frac{\mathcal{F}^{-1}(V(k\omega_p))}{nv_t}} - 1)] = 0$$

(2.29)

is formed. A correct guess of  $V(k\omega_p)$  will balance the linear and nonlinear currents for each harmonic therefore satisfying Equation (2.29). The diode example is a brief demonstration using the harmonic balance approach. The more complex problem of how to efficiently select and update V using the numerical techniques from Section 2.2 is now discussed.

### 2.4.2 Existing Harmonic Balance Techniques

With the general structure of harmonic balance discussed lets look further into how the solution is found. The task that is being attempted is basically finding the zeros of the system of equations. Thankfully these problems have been largely studied by mathematicians. The most common approach involves using Newton method [2,5,14,15]. Newton's method is a very powerful and commonly used technique for indirectly solving complicated problems. However there are still some limitations to this approach. Convergence can not be guaranteed and the size of the Jacobian matrix produced using Newton's method is directly related to the number of nonlinear devices and harmonics considered. These two major limiting factors can lead to problems finding the solution of strongly nonlinear circuits and inefficiencies for large circuits due to long solution times and large amounts of computer memory usage. To overcome some of these limitations, modifications and alternative techniques have been proposed and used. Some of which are, Optimization [2], Relaxation methods [3,4], matrix conditioning [2], Sparse Matrix

Solvers incorporating Krylov-Subspace methods with preconditioners [5,11,14,15].

### 2.4.3 Optimization

Optimization routines can be used to solve equation (2.30) using a norm of the error ( $\epsilon$ ).

$$\epsilon = F^*(V)F(V) \tag{2.30}$$

where  $F^*(V)$  denotes the complex conjugate transpose of F(V).

This method has an advantage that many scientific libraries already have an optimization routine built in. However this process destroys information about the contribution of each individual element to the error therefore convergence can suffer [2]. This technique is only practical for relatively small and simple circuits. This technique reduces programing complexity and therefore implementation time at the cost of sometimes poor convergence and inefficiency.

## 2.4.4 Relaxation Techniques

Relaxation methods derive their name from the fact that they allow the iteration process to gradually move towards a solution. One of the simplest examples of relaxation is the bisection method [7]. One main advantage of relaxation techniques are their ease of implementation [2]. These methods show promise on some circuits but in a more general sense tend to lead to poor and unpredictable convergence. Two of the more commonly known methods are those of Kerr [3] and Hicks and Khan [4].

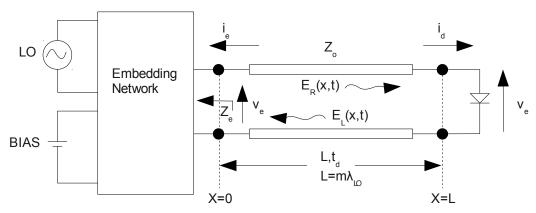

Kerr's method starts by connecting a transmission line with characteristic impedance  $Z_0$  between a linear network port and one nonlinear device, in this case a diode. Equations are

formed by separating the circuit at both ends of the transmission line. This is accomplished by increasing the transmission line length (L) so that the period between transient reflections is long enough that the ends can reach their steady state condition [3]. To solve the circuit the left propagating wave ( $E_L$ ) is calculated and after a time delay will reach the left side embedding network (Fig. 2.6). The right propagating wave ( $E_R$ ) is calculated and after another time delay will reach the right side diode. The multiple reflections continue until the voltage and current that are calculated at each end of the transmission line are equal [3].

Fig. 2.6 Kerr's Circuit Partitioning

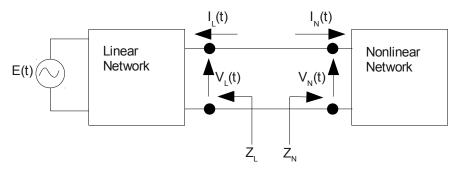

Hicks and Khan propose a method using either voltage or current updates with a circuit partitioning as seen in Fig. 2.7 The process involves selecting a value of the nonlinear port voltage  $v_N(t)$  and using it to determine the nonlinear current  $i_N(t)$  [4].

Fig. 2.7 Hicks and Khan Circuit Partitioning

From the circuit topology the nonlinear current must be equal and opposite to the linear current.

$$i_N(t) = -i_L(t) \tag{2.31}$$

The linear current is converted to the frequency domain to obtain  $I_L(\omega)$ , from which  $V_L(\omega)$  can be easily calculated and converted back to the time domain for comparison. Using the calculated value for  $v_L(t)$  the error between  $v_L(t)$  and  $v_N(t)$  can be determined. The iteration process is continued until [4]:

$$v_N^{k+1}(t) = v_N^k(t) = v_L^k(t)$$

(2.32)

The voltage update is calculated using:

$$v_{N(m)}^{k+1} = p_n v_{L(m)}^k + (1 - p_m) v_{N(m)}^k , \qquad (2.33)$$

where m is the harmonic number and k is the iteration number. The  $p_m$  term is referred to as the convergence parameter and is bound between the range of  $0 < p_m < 1$  [4]. Adjusting the value of  $p_m$  can increase the area of convergence which is typically offset by a longer solution time [4]. The equations for the current update method are analogous of those of the voltage method and therefore are not shown.

The use of an "identity network" has also been proposed to help with convergence. An example of an identity network is shown in Fig. 2.8. Where Fig. 2.8(a) is used for the voltage update method and Fig. 2.8(b) for the current update method [4].

Fig. 2.8 Identity Networks (a) Voltage Update Method (b) Current Update Method

The purpose of the identity network is to modify the harmonic impedance ratios and therefore help with solution convergence [4].

A modified version of Kerr's method [3] is proposed by Tait [12]. The technique is referred to as the Accelerated Fixed Point Algorithm. The approach maintains the fictitious transmission lines between the linear and nonlinear devices and uses the idea of multiple reflections. A Steffensen acceleration technique [30] with a voltage update method similar to that of Hicks and Khan [4] is formulated for the iteration process. For Tait's example of a frequency multiplying circuit the Steffensen acceleration process demonstrates a super linear convergence rate that approaches the quadratic rate of Newton's method [12]. This is accomplished without the need of a derivative calculation [12].

Borich [9] proposes a method based from the work of Tait [12]. The method expands Tait's approach to a more general case supporting any number of nonlinear devices. Complex characteristic impedance values for the fictitious transmission lines are also examined. The use

of complex characteristic impedance values is shown to improve convergence especially in cases with nonlinear capacitances [9].

An advantage to the use of relaxation techniques is their somewhat easier implementation [2]. They however often demonstrate poor convergence performance in general terms and difficulties arise when dealing with large circuits. The general convergence properties of Borich's work is shown by Blakey to be possible for circuits containing only a few nonlinear devices and recommends the use of conventional harmonic balance for more complex circuits [13]. Improvements in dealing with large circuits and solution convergence have been shown with the use of Newtons method [5,14,15].

#### 2.4.5 Newton Based Methods for Harmonic Balance

As has been discussed before issues arise when the problem size is increased. Krylov subspace with inexact harmonic balance and GMRES (Section 2.4.5) has shown good performance for solving complex systems with success. However large circuits which are strongly nonlinear therefore requiring many harmonics increase this process into a huge computational task. For this reason it becomes apparent that sub dividing the circuit into smaller sub circuits is appealing. This is accomplished by decoupling parts of the circuit that have little to no dependence on one another [15,18]. The technique requires the individual partitions to converge to solution. The entire system then must satisfy global convergence between all sub circuits. The use of Newtons method has been demonstrated to be a powerful tool for solving nonlinear circuits using the harmonic balance approach [2,5,15].

The Jacobian matrix in harmonic balance is made up of partial derivatives of every port

with respect to every frequency and because all harmonics except DC are complex the size must be doubled. The size of the Jacobian matrix required for the full newton method is M x M where,  $M = p \times (2m+1)$ , p is the number of ports and m is the number of harmonics.

The size of the Jacobian itself becomes an issue in memory storage but the major problem arises when the calculation to factor it occurs. The Jacobian matrix formed during calculations, is not usually sparse. Direct matrix solves such as LU decomposition require a large amount of memory space. The approximate time required to compute the LU decomposition of a dense matrix is related to its dimension cubed. For example doubling the matrix dimension will require approximately eight times the amount of time to decompose [2].

Sparse matrix solvers are used to improve processing time and memory usage as the zero matrix entries are not stored in memory. For sparse matrix solvers to have a benefit the Jacobian matrix is typically pruned to further increase the number of zero entries. As the matrix is factored during calculations the zeros entries can tend to "fill-in" with non-zero values. Care must be taken to prevent or limit such "fill-ins" as they reduce the sparse matrix solving benefits [2].

## 2.4.6 Krylov-Subspace Methods

The general consensus for solving harmonic balance problems is using a version of Krylov-Subspace method called generalized minimum residual technique or GMRES [2,5]. The technique works the way it sounds. Assuming we must solve an equation of the form  $[A]\bar{x} = \bar{b}$  where [A] is a matrix and  $\bar{x}$  and  $\bar{b}$  are vectors. Defining the residual  $\bar{r}$  as  $\bar{r} = \bar{b} - [A]\hat{x}$  and using iterative methods to reduce the residual, with the  $\hat{x}$  term being an estimation of the solution. However if the matrices are ill-conditioned to begin with, convergence

has very little chance of being achieved [2]. Also for this process to succeed the approximate guess  $\hat{x}$  must be relatively close to solution, therefore the use of preconditioning becomes a requirement [2].

#### 2.4.7 Preconditioning

With the techniques discussed in the previous section the use of preconditioning is a requirement for achieving convergence to solution. Some variations of preconditioning are block diagonal [5], static time, iterative time [11] and incomplete LU factorization [15,16].

Block diagonal preconditioning has shown good convergence properties when used with Krylov subspace using inexact harmonic balance and GMRES. As is the problem with full Newton iterations computer storage and computational cost of large circuits limit its efficiency [5]. Rizzoli proposes a method called incomplete LU factorization [15]. The idea is based on exploiting the sparsity pattern in the Jacobian matrix. This sparsity is artificially generated by examining the interaction or dependence between different nonlinear devices [5]. It has been demonstrated that this approach works better when the linear network is represented by its scattering parameters instead of conventional admittance parameters [5,17].

The time based preconditioners both static and iterative are developed using the time counterpart of the frequency domain Jacobian [11]. The difference between static and iterative preconditioners is in the steps of achieving the preconditioning matrix. Terms are dropped in the static method to eliminate the need to iteratively solve for the preconditioning matrix. The iterative method does not neglect these terms [11].

The use of a preconditioner is a requirement for the use of Krylov subspace methods. The

type of preconditioner selected plays an integral role in finding the solution and therefore the convergence performance.

### 2.5 The fREEDA Circuit Simulator

#### 2.5.1 fREEDA State Variable Formulation

The fREEDA simulator is a free program which supports different circuit analysis types such as transient, harmonic balance and wavelet-based transient analysis. fREEDA is a circuit simulator which uses state variables to represent the nonlinear device models.

fREEDA uses the previously discussed linear and nonlinear sub-circuit partitioning for harmonic balance as shown in Fig. 2.2. The state variable approach models the nonlinear devices using a set of general parametric equations,

$$\overline{i}_{NL}(t) = w \left[ \overline{x}(t), \frac{d\overline{x}}{dt}, \dots, \frac{d^m \overline{x}}{dt^m}, \overline{x}_D(t) \right]$$

(2.34)

$$\bar{v}_{NL}(t) = u \left[ \bar{x}(t), \frac{d\bar{x}}{dt}, \cdots, \frac{d^m \bar{x}}{dt^m}, \bar{x}_D(t) \right]$$

(2.35)

The currents and voltages present at each of the nonlinear device ports is represented by vectors  $\bar{i}_{NL}(t)$  and  $\bar{v}_{NL}(t)$  [10]. The vector of state variables is defined as  $\bar{x}(t)$  and the vector of time delayed state variables is defined as  $\bar{x}_D(t)$ . The time-delayed state variable vector  $\bar{x}_D(t)$  can be written as a function of time (t) with a time delay  $\tau_i$ , i.e.  $(\bar{x}_D(t))_i = \bar{x}_i(t-\tau_i)$ . The time delay term  $\tau_i$  can be a function of the state variables  $\bar{x}(t)$  [10]. The size of the all vectors in equations (2.34) and (2.35) are the same and equal to the number of ports between the subcircuits [10]. The use of parametric equations allows for complete generality in the modeling of

each nonlinear device.

The use of harmonic balance requires the availability of port voltage and currents in the frequency domain. So far equations have been written and formulated in the time domain. The conversion to the frequency domain is accomplished using a vector of time domain samples of the  $i^{TH}$  state variable given by,

$$\bar{\mathbf{x}}_i = [x_i(t_0), x_i(t_1), \dots, x_i(t_{2m}),]^T$$

(2.36)

Converting all of the frequency based state variables to the time domain is accomplished as follows:

$$\bar{\mathbf{x}}_i = \mathcal{F}^{-1}(\bar{X}_i) \tag{2.37}$$

For one device having n states, the state-variable vector in frequency domain is defined as follows,

$$\bar{X} = \begin{bmatrix} \bar{X}_1 \\ \bar{X}_2 \\ \vdots \\ \bar{X}_n \end{bmatrix}$$

(2.38)

Each state from Equation (2.38) is comprised of individual frequency components (m),

$$\bar{X}_{i} = \begin{bmatrix} X_{i,0} \\ X_{i,1} \\ \vdots \\ X_{i,m} \end{bmatrix}$$

(2.39)

The time-domain vectors of the derivatives and time-delayed state variables are obtained using the following equations:

$$\frac{d\,\bar{\mathbf{x}}_{i}(t)}{dt} = \mathcal{F}^{-1}(j\,\Omega\,\bar{X}_{i}) \quad \text{where} \quad \Omega = \begin{bmatrix} 0 & 0 & \cdots & 0 \\ 0 & \omega_{0} & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & \cdots & m\omega_{0} \end{bmatrix}$$

(2.40)

$$\bar{\mathbf{x}}_{D(i)}(t) = \mathcal{F}^{-1} \begin{bmatrix} e^{j\omega_0(0)\tau_{D(i)}} & 0 & \cdots & 0 \\ 0 & e^{j\omega_0(1)\tau_{D(i)}} & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & \cdots & e^{j\omega_0(m)\tau_{D(i)}} \end{bmatrix} \bar{X}_i$$

(2.41)

The samples of  $\bar{i}_{NL}(t)$  and  $\bar{v}_{NL}(t)$  are generated using equations (2.34) and (2.35). Finally the Fourier transform is used to obtain the  $\bar{I}_{NL}$  and  $\bar{V}_{NL}$  vectors in the frequency domain.

$$\bar{I}_{NL(i)} = \mathcal{F}[\bar{i}_{NL(i)}(t)] \tag{2.42}$$

$$\bar{V}_{NL(i)} = \mathcal{F}[\bar{v}_{NL(i)}(t)] \tag{2.43}$$

where

$$\bar{V}_{NL} = \begin{bmatrix} \bar{V}_{NL(1)} \\ \bar{V}_{NL(2)} \\ \vdots \\ \bar{V}_{NL(n)} \end{bmatrix} & \qquad \bar{I}_{NL} = \begin{bmatrix} \bar{I}_{NL(1)} \\ \bar{I}_{NL(2)} \\ \vdots \\ \bar{I}_{NL(n)} \end{bmatrix}$$

(2.44)

### 2.5.2 fREEDA Architecture and Addition of New Simulation Technique

The fREEDA simulator is programmed mainly using the C++ language. The circuit description is entered as a netlist file that has a format similar to the open source Simulation Program with Integrated Circuit Emphasis (SPICE)[26]. This allows the circuit to be formulated in a standard way which can be used for various simulation types. Internally the code for each circuit analysis type is defined in a separate class. For a particular analysis type to be used a command line is entered in the netlist file with various user configurable options. The device

models are formulated using state variables and adding a new device is done separately of the main program. The addition of a new circuit analysis type requires minimal changes in the core code and consists mainly in the addition of a new class. The circuit data is available to the new class in an internal representation format (a graph).

In fREEDA the frequency domain vectors  $\bar{I}_{NL}$  and  $\bar{V}_{NL}$  are directly available as functions of the state variables  $\bar{X}$  (also in the frequency domain). This simplifies the task of implementing frequency domain analysis techniques such as harmonic balance.

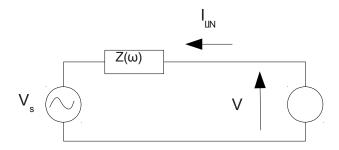

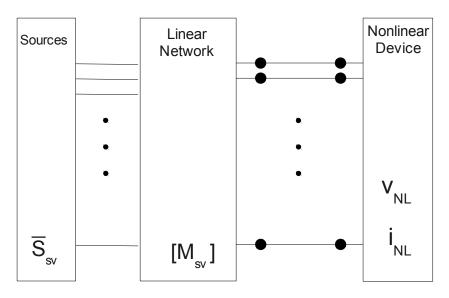

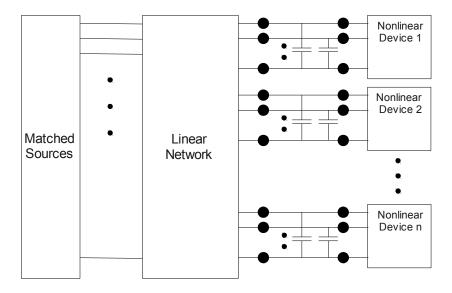

The programing architecture provides access to the circuit information in various forms such as, modified nodal admittance matrix, source vector, linear network impedance matrix and others. FREEDA uses a circuit partitioning shown in Fig. 2.9 which allows for the easy addition of a new simulation technique.

Fig. 2.9 fREEDA Circuit Partition

The selected implementation approach uses the linear network impedance matrix represented by  $[M_{SV}]$ , containing the linear network information and topology. The  $\bar{S}_{SV}$  vector

contains the contribution of the sources to the circuit.

The circuit partitioning required for the wave approach is shown in Fig. 2.10. Each nonlinear device is divided up into its own block with subsequent ports. Each nonlinear device is represented by independent state variables ( $\bar{X}$ ) which are used to calculate the voltages and currents at the ports of nonlinear devices.

Fig. 2.10 Circuit Partition Used in This Thesis.

The error function within fREEDA is given by,

$$\bar{S}_{sv} - [M_{sv}]\bar{I}_{NL}(\bar{X}) - \bar{V}_{NL}(\bar{X}) = \bar{0}$$

(2.45)

The nonlinear devices can have any number of state variables. For example a two terminal device such as a diode has one state variable. A BJT transistor with emitter, base and collector would be a two state variable device.

#### 2.5.3 Example Netlist in fREEDA

An example of a simple netlist used in fREEDA is shown in Fig. 2.11.

```

**** Wave HB Simple Diode Circuit ***

*Simulation options

.options freq=1e8

*Simulation Type and setup parameters

.wavehb n_freqs=15 fundamental=freq tol=1e-8 usecaps=0 n_iter=100 zref=800

*Circuit netlist

vsource:v1 1 0 f=freq vac=5 phase=-90

resistor:r1 1 2 r=1k

diode:d1 2 0 js=5.1e-14 alfa=38.696 jb=1.0e-5 vb=-1.0e50 e=10

+ CT0=1.32767e-15 gama=0.810205 fi=1.27517 afac=38.696 area=271 r0=10.

*Simulation Output

.out plot term 2 vf invfft 2 repeat in "simplediodev.whb"

.out plot term 1 vf term 2 vf sub invfft 2 repeat in "simpledioderesv.whb"

.end

Fig. 2.11 Example Netlist

```

The first two lines are comments marked at the beginning by an '\*'. The .options line is where various simulation names can be defined in this example the frequency is set to 1e8. The next line after the comment selects the type of simulation to run. In this case the wave harmonic balance (Wave HB) simulation technique is called (.wavehb). The various setup options for the simulation technique are also included on this line. The number of frequencies considered for the harmonic balance simulation is 15, the fundamental frequency is 'freq', the solution tolerance is set to 1e-8, the number of Newton iterations for each nonlinear device is 100 and the reference impedance is 800Ω. The next few lines represent the circuit configuration and values. The vsource, resistor and diode represent the type of component in the circuit. The following numbers are the nodes the device is connected to and the specific values and parameters of the device. The final lines set the output data to be saved when the simulation is complete. For this simulation the voltage at the specified nodes is converted from the frequency domain (invfft) to produce the voltage with respect to time waveform plot.

# Chapter 3

## **Wave Based Harmonic Balance**

## 3.1 Introduction

This chapter presents a formulation of HB using power waves that expands the techniques discussed in Section 2.4.2, i.e., Kerr's multiple reflections [3] and Hicks and Khan's voltage updates [4]. The use of power waves could improve the convergence of the system because conservation of power restraints can be implemented on the reflections to prevent possible divergence situations; if a device is passive then the power of the reflected waves must be less than or equal to the power of the incident waves. The wave-based HB technique is implemented and demonstrated in fREEDA. This chapter covers the formulation of equations, flow of the algorithm, convergence analysis, convergence improvements, programming and implementation, preconditioner applications and problems encountered.

Section 3.2 presents the formulation of the HB equations, harmonic balance solution process and programing implementation. Section 3.3 analyzes the convergence of the proposed wave HB method and Section 3.4 proposes convergence improvements. Section 3.5 explores the possibilities of the wave HB method being used as a preconditioner. Section 3.6 highlights problems with implementation and their solutions.

## 3.2 fREEDA Programing and Implementation

As previously discussed fREEDA is used to implement the proposed wave HB technique. Starting from the general form between the linear and nonlinear circuit partition discussed in Section 2.5, we need to interface with fREEDA. For this some transformations of circuit information and programing structure must be performed. This is broken into three parts, equation formulation, solution process, and implementation.

### 3.2.1 fREEDA Equation Formulation (Linear)

The first step for the proposed method is connecting fictitious transmission lines between the linear and nonlinear networks. The characteristic impedance of the transmission lines is denoted as  $Z_{ref}$  and their length is set to zero. The characteristic impedance is the same for all transmission lines connected between the linear and nonlinear ports.

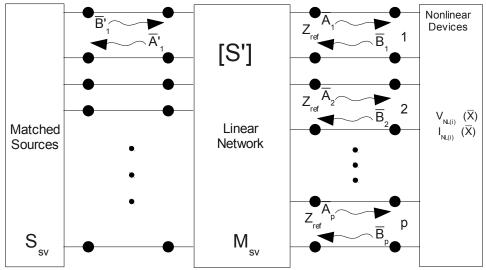

Incident power waves  $\bar{A}$ ,  $\bar{A}$  and reflected power waves  $\bar{B}$ ,  $\bar{B}$  are defined as shown in Fig. 3.1. The direction of the incident and reflected power waves differs from that of a conventional two port network by referencing to the nonlinear devices.

With the use of transmission line theory the network matrix  $[M_{SV}]$  must be transformed into a scattering parameter matrix ([S]). The transmitted and reflected power waves replace the voltages and currents. The changes to the partitioning and introduction of power waves is shown in Fig. 3.1. In this section the power waves ( $\bar{A} \& \bar{B}$ ) and port voltage ( $\bar{V}_{NL}$ ) and currents ( $\bar{I}_{NL}$ ) are valid for all ports at one frequency.

Fig. 3.1 Partition with Fictitious Transmission Lines and Power Waves

For each frequency the scattering parameter matrix ( [S'] ) represents a multi-port network with two groups of ports,

$$\begin{bmatrix} \bar{A} \\ \bar{A}' \end{bmatrix} = \begin{bmatrix} S' \end{bmatrix} \begin{bmatrix} \bar{B} \\ \bar{B}' \end{bmatrix} = \begin{bmatrix} \begin{bmatrix} S_{11} \end{bmatrix} & \begin{bmatrix} S_{12} \end{bmatrix} \begin{bmatrix} \bar{B} \\ \bar{B}' \end{bmatrix}$$

$$(3.1)$$

The network topology and linear device values are contained in the scattering matrix. The individual blocks in equation (3.1) represent the relationships between the incident and reflected waves at the two port groups. Since the sources are assumed to be matched,  $\bar{B}'(\text{vector})$  is independent of  $\bar{A}'$ . Thus  $\bar{A}'$  is not needed to calculate the waves incident to the nonlinear device ports (p) and  $\bar{A}$  is given by:

$$\bar{A} = [S_{11}]\bar{B} + [S_{12}]\bar{B}'$$

(3.2)

Defining  $\bar{A}_0 = [S_{12}]\bar{B}'$  and  $[S] = [S_{11}]$  , respectively leads to,

$$\bar{A} = [S]\bar{B} + \bar{A}_0 \tag{3.3}$$

The relation between  $[M_{SV}]$ ,  $\bar{S}_{SV}$ , [S] and  $\bar{A}_0$  will be derived next. Starting from the original error function provided in fREEDA given in equation (2.45) and repeated here for convenience,

$$\bar{S}_{sv} - [M_{sv}]\bar{I}_{NL}(\bar{X}) - \bar{V}_{NL}(\bar{X}) = \bar{0}$$

(3.4)

a relationship between  $\bar{V}_{NL}$ ,  $\bar{I}_{NL}$  and  $\bar{A}$ ,  $\bar{B}$  is required. Defining a diagonal matrix [D] of size  $p \times p$  which contains the square root of the characteristic impedance of the transmission lines and has a structure of,

$$[D] = \begin{bmatrix} \sqrt{Z_{ref}} & 0 & 0 & 0\\ 0 & \sqrt{Z_{ref}} & 0 & 0\\ 0 & 0 & \dots & \dots\\ 0 & 0 & \dots & \sqrt{Z_{ref}} \end{bmatrix}$$

(3.5)

$\bar{I}_{NL}$  and  $\bar{V}_{NL}$  can be written as follows:

$$\bar{V}_{NL} = [D](\bar{A} + \bar{B}) \tag{3.6}$$

$$\bar{I}_{NL} = [D]^{-1}(\bar{A} - \bar{B})$$

(3.7)

Substituting Equation (3.6) and Equation (3.7) into the original fREEDA error function Equation (3.4) the new equation is formed.

$$\bar{S}_{sv} - [M_{sv}][D]^{-1}(\bar{A} - \bar{B}) - [D](\bar{A} + \bar{B}) = \bar{0}$$

(3.8)

Rearranging Equation (3.8) to isolate for the incident power wave  $\overline{A}$  yields,

$$\bar{A} = ([M_{sv}][D]^{-1} + [D])^{-1} [-\bar{S}_{sv} + ([M_{sv}][D]^{-1} - [D])\bar{B}]$$

(3.9)

Multiplying  $([M_{sv}][D]^{-1} + [D])^{-1}$  into  $[-\bar{S}_{sv} + ([M_{sv}][D]^{-1} - [D])\bar{B}]$  the Equation (3.9) is arranged to match the structure of Equation (3.3).

$$\bar{A}_{m} = ([M_{sv}][D]^{-1} + [D])^{-1}([M_{sv}][D]^{-1} - [D])\bar{B}_{m} + ([M_{sv}][D]^{-1} + [D])^{-1}\bar{S}_{sv}$$

(3.10)

From this a new definition of [S] and  $\bar{A}_0$  is obtained:

$$[S] = ([M_{sv}][D]^{-1} + [D])^{-1}([M_{sv}][D]^{-1} - [D])$$

(3.11)

$$\bar{A}_0 = ([M_{sv}][D]^{-1} + [D])^{-1} \bar{S}_{sv}$$

(3.12)

With a definition of [S] and  $\bar{A}_0$  their values are calculated. The parameters of the scattering matrix and source vector change with respect to frequency. This requires independent  $[S_m]$  and  $\bar{B}_{0,m}$  terms for each harmonic (m) plus DC considered. Each element of the scattering matrix and source vector are also comprised of complex values.

### 3.2.2 fREEDA Equation Formulation (Nonlinear)

In this section the power waves ( $\bar{A} \& \bar{B}$ ), state variables ( $\bar{X}$ ), port voltages ( $\bar{V}_{NL}$ ) and port currents ( $\bar{I}_{NL}$ ) are valid for all harmonics (m) plus DC for one nonlinear device (d). The vector containing power wave reflections from the nonlinear devices ( $\bar{B}_m$ ) is calculated using Newton's method. Combining Newton's technique with the use of state variables requires the development of both the update equations and the error functions for each port. The error functions are based from Equation (3.6) and Equation (3.7) by moving all terms to the right and defining error functions  $\bar{f}_v$  and  $\bar{f}_i$  as follows:

$$\bar{f}_{v} = D^{-1} \bar{V}_{NL} - \bar{A} - \bar{B}$$

(3.13)

$$\bar{f}_i = D\bar{I}_{NL} - \bar{A} + \bar{B} \tag{3.14}$$

There is a set of voltage and current error functions defined for each nonlinear device and each frequency and the [D] matrix has dimensions  $(n \times (m+1)) \times (n \times (m+1))$  where,

( $n=number\ of\ states$  and  $m=number\ of\ harmonics$ ). The [D] matrix is comprised of diagonal elements of  $\sqrt{Z_{ref}}$  the same as in Section 3.2.1.

With the use of Newton's method (Section 2.2.1) the formulation of the Newton iteration equations is as follows,

$$\begin{bmatrix}

\frac{\partial f_{v}}{\partial X} & \frac{\partial f_{v}}{\partial B} \\

\frac{\partial f_{i}}{\partial X} & \frac{\partial f_{i}}{\partial B}

\end{bmatrix} \begin{bmatrix}

X^{k+1} - X^{k} \\

B^{k+1} - B^{k}

\end{bmatrix} = -\begin{bmatrix}

f_{v}(X^{k}, B^{k}) \\

f_{i}(X^{k}, B^{k})

\end{bmatrix}$$

$$\rightarrow \begin{bmatrix}

\frac{\partial f_{v}}{\partial X} & \frac{\partial f_{v}}{\partial B} \\

\frac{\partial f_{i}}{\partial X} & \frac{\partial f_{i}}{\partial B}

\end{bmatrix} \begin{bmatrix}

X^{k+1} - X^{k} \\

B^{k+1} - B^{k}

\end{bmatrix} + \begin{bmatrix}

f_{v}(X^{k}, B^{k}) \\

f_{i}(X^{k}, B^{k})

\end{bmatrix} = \begin{bmatrix}

0 \\

0

\end{bmatrix}$$

(3.15)

Taking the partial derivative of the error function given in Equation (3.13),

$$\frac{\partial f_{v}}{\partial X} = [D]^{-1} \frac{\partial V_{NL}(X)}{\partial X} \text{ and } \frac{\partial f_{v}}{\partial B} = -[I]$$

$$= [D]^{-1} [J_{v}]$$

(3.16)

Similarly for Equation (3.14),

$$\frac{\partial f_i}{\partial X} = [D]^{-1} \frac{\partial I_{NL}(X)}{\partial X} \text{ and } \frac{\partial f_i}{\partial B} = [I]$$

$$= [D]^{-1} [J_i]$$

(3.17)

Substituting Equation (3.16) and Equation (3.17) into Equation (3.15),

$$\begin{bmatrix} [D]^{-1}J_{v} & [I] \\ [D]J_{i} & [I] \end{bmatrix} \begin{bmatrix} \Delta X \\ \Delta B \end{bmatrix} + \begin{bmatrix} f_{v} \\ f_{i} \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \end{bmatrix}$$

(3.18)

And solving for  $\Delta B$  and  $\Delta X$  leads to,

$$\Delta \bar{B} = -\bar{f}_i - [D][J_i] \Delta \bar{X}$$

(3.19)

and

$$\Delta \bar{X} = ([D][J_i] + [D]^{-1}[J_v])^{-1}(-\bar{f}_i - \bar{f}_v)$$

(3.20)

Defining the updates for one nonlinear device ( $\bar{X}_d$  and  $\bar{B}_d$ ) from (3.19) and (3.20) is given by,

$$\Delta \bar{X}_d = ([D][J_{i(d)}] + [D]^{-1}[J_{v(d)}])^{-1}(-\bar{f}_{i(d)} - \bar{f}_{v(d)})$$

(3.21)

$$\Delta \bar{B}_d = -\bar{f}_{i(d)} - [D][J_{i(d)}] \Delta \bar{X}_d$$

(3.22)

Where  $[J_{v(d)}]$  and  $[J_{i(d)}]$  are the Jacobian matrices of the port voltage and currents for the nonlinear device being calculated using the state variables from Section 2.5.1.

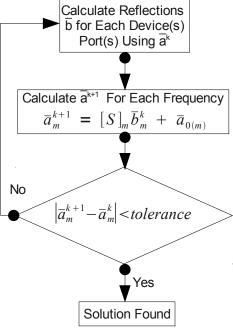

Harmonic balance technique requires the state variables in the frequency domain. fREEDA provides the Jacobian matrix, state variables, port voltages and currents directly, using the process discussed in section 2.5.1. Combining the linear and nonlinear calculations together produces a fixed point iterations technique given by,

$$\bar{A}_m^{k+1} = [S]_m \bar{B}_m^k + \bar{A}_{0(m)} \tag{3.23}$$

Each nonlinear device's reflected power wave ( $\bar{B}_d$ ) is calculated independently for each nonlinear device considering all frequencies simultaneously. When all of the nonlinear device's reflected waves have been solved for the current iteration (k), Equation (3.23) is independently calculated for each harmonic considered using the reflected waves provided from the nonlinear device's Newton iterations. The solution is found when Equation (3.23) is satisfied for all harmonics. A more detailed explanation of this process is discussed in the next in Section.

### 3.2.3 Solution Methodology