# AN INTEGRATED FULL-BRIDGE CLASS-DE ULTRASOUND TRANSDUCER DRIVER FOR HIFU APPLICATIONS

by Ruiqi Song

Supervised by Dr. Carlos E. Christoffersen, and Dr. Laura Curiel

A thesis submitted in partial fulfilment of the requirement of the M. Sc. degree in Electrical and Computer Engineering department of Lakehead University

Thunder Bay, Ontario

May 3, 2016

#### Abstract

This thesis present a CMOS integrated transducer driver for high intensity focused ultrasound (HIFU) applications. Because this driver will be used in a magnetic resonance imaging (MRI) environment, no magnetic components such as inductors and transformers have been used in this design. The transducer is directly connected to the driver without a matching network. The output stage of this driver is a full-bridge Class DE RF amplifier which is able to deliver more power than the previous design that has a half-bridge Class DE amplifier.

The driver was also designed to be used in a transducer array. A digital control unit was integrated with the power amplifier that allows to program the drivers phase shift and duty ratio. A strategy to drive a ultrasound transducer array using the designed driver is also presented in this thesis.

This design was implemented using the AMS H35B4 CMOS technology using the Cadence suite of design tools and occupies a die area of 2mm by 1.5mm with 20 input and output pads. Simulation and initial experimental results are presented in this work. The proposed integrated CMOS driver has an efficiency of 89.4% with 3.60 W of output power. Results are little bit different for each transducer.

# Acknowledgements

This thesis was supported by Lakehead University and CMC Microsystems.

It gives me great pleasure in acknowledge my supervisor, Dr. Carlos E. Christoffersen, and my co-supervisor, Dr. Laura Curiel, for allowing me to work on this research project and for their support by providing insightful guidance.

I also would like to thank my family for their encouragement, patience and understanding.

Ruiqi Song rsong1@lakeheadu.ca

# Contents

| 1        | Inti | roduction                                          | 1  |

|----------|------|----------------------------------------------------|----|

|          | 1.1  | Objectives and Motivation of this study            | 1  |

|          | 1.2  | Thesis Overview                                    | 3  |

| <b>2</b> | Bac  | ckground Information and Literature Review         | 4  |

|          | 2.1  | Introduction                                       | 4  |

|          | 2.2  | Characterization of Ultrasound Transducer          | 4  |

|          | 2.3  | Switched RF Amplifiers                             | 7  |

|          |      | 2.3.1 Class-D Amplifiers                           | 7  |

|          |      | 2.3.2 Class-E Amplifiers                           | 11 |

|          |      | 2.3.3 Class-DE Amplifier                           | 12 |

|          |      | 2.3.4 Step-up Driving Circuit                      | 14 |

|          |      | 2.3.5 Flyback Topology                             | 14 |

|          |      | 2.3.6 Push-pull driving circuit                    | 14 |

|          | 2.4  | Literature Review                                  | 16 |

|          | 2.5  | Previous Design by Our Group                       | 20 |

|          | 2.6  | Summary                                            | 30 |

| 3        | Stra | ategy to Drive a Transducer array in Class-DE Mode | 32 |

|          | 3.1  | Characterization of the Transducer Array           | 34 |

|          | 3.2  | The Transducer Array Driving Strategies            | 35 |

|          |      | 3.2.1 Using an External Parallel Capacitor         | 38 |

|          |      | 3.2.2 Using the Average frequency                  | 42 |

|          | 3 3  | Summary                                            | 49 |

CONTENTS

| 4            | Ult | rasonic Transducer Driver Design                    | 45 |

|--------------|-----|-----------------------------------------------------|----|

|              | 4.1 | Introduction                                        | 45 |

|              | 4.2 | Full-bridge Class-DE Amplifier                      | 46 |

|              | 4.3 | The Gate driver                                     | 49 |

|              | 4.4 | Digital Logic Unit                                  | 50 |

|              |     | 4.4.1 The Structure of Each Block                   | 50 |

|              |     | 4.4.2 Operating procedure of the digital logic unit | 56 |

|              |     | 4.4.3 Additional Safety Logic Block                 | 60 |

|              |     | 4.4.4 Simulation Results of Digital Logic Unit      | 62 |

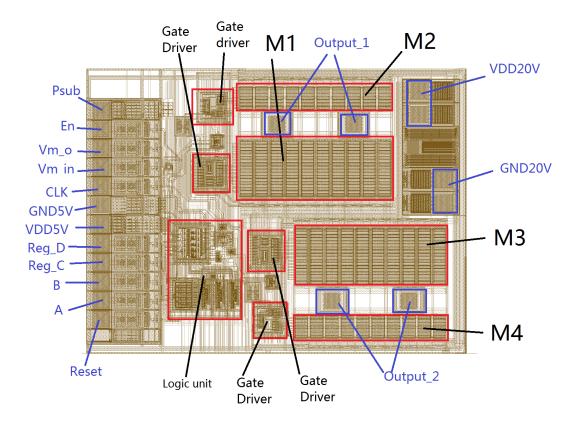

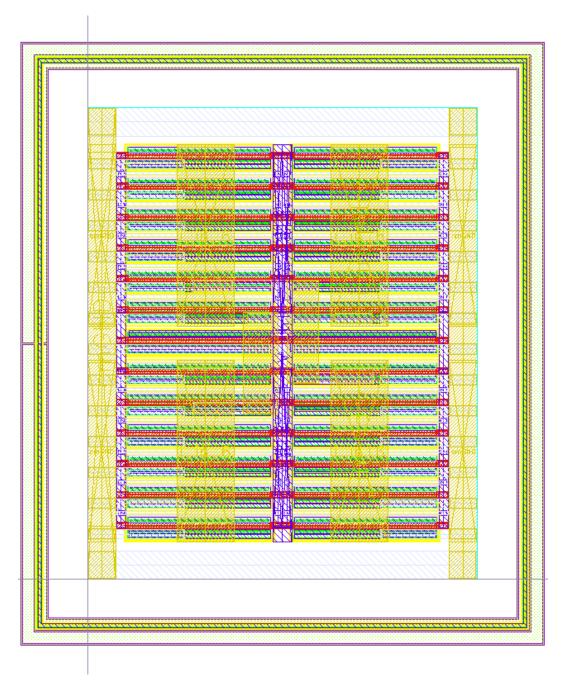

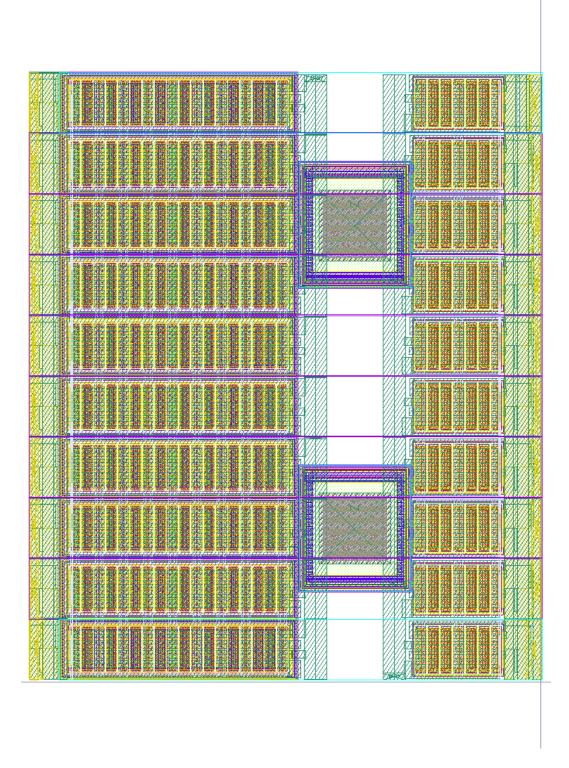

|              | 4.5 | The Layout Design                                   | 65 |

| 5            | Sim | ulation and Experimental Results                    | 67 |

|              | 5.1 | Simulation Results with Optimum Parameters          | 67 |

|              | 5.2 | Experimental Setup                                  | 70 |

|              | 5.3 | Experimental Results                                | 72 |

| 6            | Cor | nclusions and Future Work                           | 77 |

|              | 6.1 | Conclusions                                         | 77 |

|              | 6.2 | Future Work                                         | 77 |

| $\mathbf{A}$ | Pin | Diagram of the Full-Bridge Class-DE Driver          | 79 |

| В            | Par | ameter Calculations of MOSFETs                      | 80 |

|              | B.1 | Gate Capacitance of MOSFETs                         | 80 |

|              | B.2 | $\mathbf{K}'$ and Threshold Voltage                 | 82 |

|              |     | B.2.1 Calculation of on-resistance                  | 86 |

| $\mathbf{C}$ | Sch | ematic Diagrams                                     | 87 |

| D            | Lay | out View                                            | 91 |

# List of Figures

| 1.1  | Block diagram of driving an Ultrasound transducer array                                  | 2  |

|------|------------------------------------------------------------------------------------------|----|

| 2.1  | Structure of an ultrasound transducer [2]                                                | 5  |

| 2.2  | BVD equivalent circuit of a resonator near its resonance frequency $[1,2]$               | 5  |

| 2.3  | Impedance and admittance plots of the equivalent circuit of transducers $\dots \dots$    | 6  |

| 2.4  | Plots of measured reflection coefficient and equivalent circuit model's reflection coef- |    |

|      | ficient on a Smith Chart                                                                 | 8  |

| 2.5  | Schematic of the CMOS integrated Class-D RF amplifier $[6]$                              | 9  |

| 2.6  | Input and output waveforms of the CMOS integrated Class-D RF amplifier $[6]$             | 9  |

| 2.7  | Topology of the CMOS integrated Class-D full-bridge RF amplifier                         | 10 |

| 2.8  | Topology of the CMOS integrated Class-E RF amplifier                                     | 11 |

| 2.9  | Input and output waveforms of the CMOS integrated Class-E RF amplifier. $[6]$            | 12 |

| 2.10 | Schematic of the CMOS integrated Class-DE RF amplifier                                   | 13 |

| 2.11 | Schematic of the step-up driving circuit                                                 | 13 |

| 2.12 | Topology of the flyback transducer driver [8]                                            | 15 |

| 2.13 | Schematic of the Push-pull driving circuit                                               | 15 |

| 2.14 | Schematic of the transducer driver which was proposed by Cain and Hall [9]               | 16 |

| 2.15 | Schematic of the driver that is used by Tang and Clement [7]                             | 17 |

| 2.16 | Input waveform of the driver that is used by Tang and Clement $[7]$                      | 18 |

| 2.17 | Schematic of driver that is proposed by Yang and Xu [10]                                 | 18 |

| 2.18 | Schematic of high voltage pulser that is proposed by Zhao and Tian [11]                  | 19 |

| 2.19 | Block diagram of A. Bozkurk and O. Farhanieh's driver IC $[12]$                          | 20 |

| 2.20 | Schematic of staircase-wave driver that is proposed by K. Moro and J. Okada. $[13]$ .    | 21 |

| 2.21 | Input and output voltage waveforms of the staircase-wave driver [13]                     | 22 |

| 2.22 | Schematic of driver that is proposed by Wai Wong. [5]                                    | 23 |

LIST OF FIGURES V

| 2.23 | Output waveforms of half-bridge Class-DE amplifier [5]                                     | 23 |

|------|--------------------------------------------------------------------------------------------|----|

| 2.24 | Equivalent circuits of Class-DE amplifier in each interval. [6]                            | 24 |

| 2.25 | Variations of $f_r$ and $f_x$ with duty ratio of an ultrasound transducer                  | 27 |

| 2.26 | $f_r$ and $f_x$ plots of transducer Tx.3                                                   | 29 |

| 2.27 | Effect of duty ratio on efficiency,output power and current peak with variable duty        |    |

|      | ratios                                                                                     | 29 |

| 2.28 | Output waveforms for transducer Tx.3                                                       | 30 |

| 3.1  | Multi-element ultrasound transducer array that was designed by J. L. Kivinen $[4]$         | 32 |

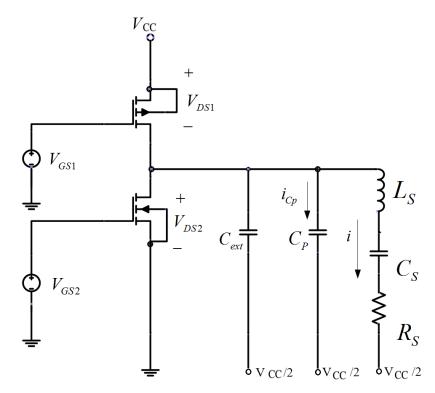

| 3.2  | Half-bridge Class-DE amplifier which was proposed by Wai Wong $[1,2,5]$                    | 33 |

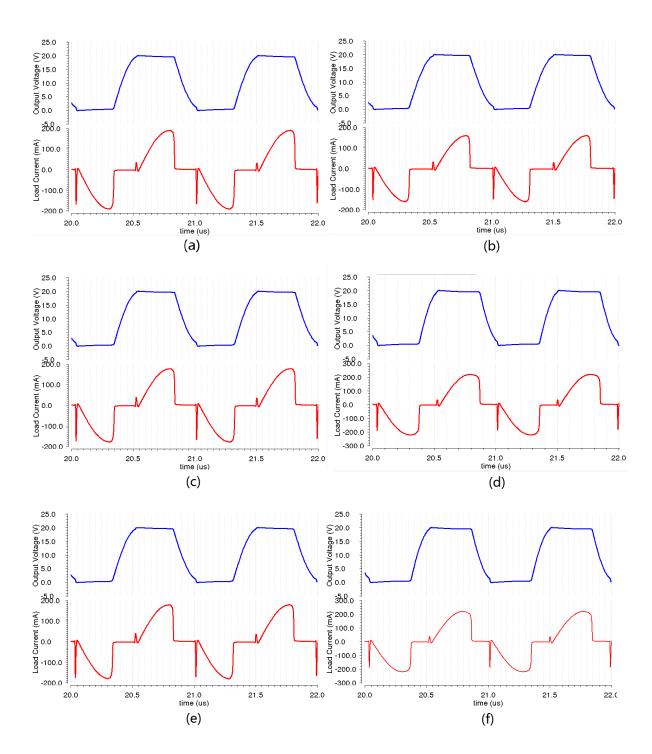

| 3.3  | Output voltage and current waveforms of all the six elements that are driven by            |    |

|      | Class-DE amplifier                                                                         | 36 |

| 3.4  | Output voltage and current waveforms of element B that is driven under $1024 \mathrm{kHz}$ |    |

|      | which is a non-optimum frequency for element B $$                                          | 37 |

| 3.5  | Half-bridge Class-DE amplifier with the parallel external capacitor $\dots \dots$          | 38 |

| 3.6  | $C_{ext,r}$ and $C_{ext,x}$ 's plots of element E in Kivinen's transducer array            | 39 |

| 3.7  | Output waveforms of all the elements that are driven by the using the external ca-         |    |

|      | pacitor method                                                                             | 41 |

| 3.8  | Output waveforms of all the elements that are driven by the average of their optimum       |    |

|      | frequencies                                                                                | 43 |

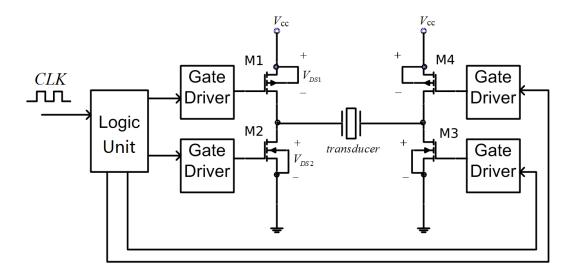

| 4.1  | Block diagram of the proposed integrated transducer driver [5]                             | 45 |

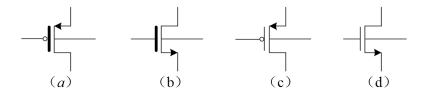

| 4.2  | Symbols of the MOSFETs (a) HV PMOS; (b) HV NMOS; (c) LV PMOS; (d) LV NMOS                  | 46 |

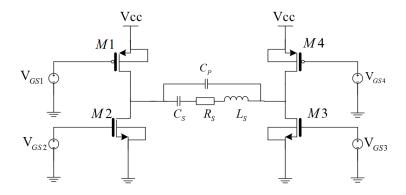

| 4.3  | Topology of the full-bridge Class-DE amplifier                                             | 47 |

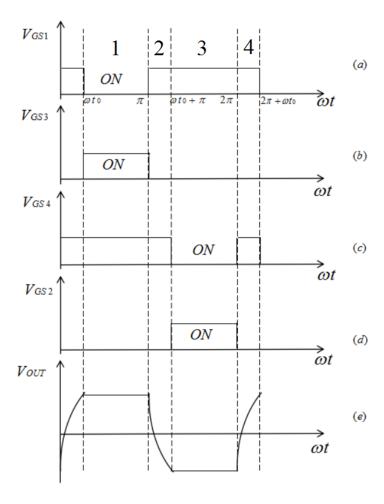

| 4.4  | Inputs and output waveforms of the full-bridge Class-DE amplifier, (a), (b), (c) and       |    |

|      | (d) The switch-on diagram of transistors M1, M2, M3 and M4. (e) The voltage                |    |

|      | waveform across the load                                                                   | 48 |

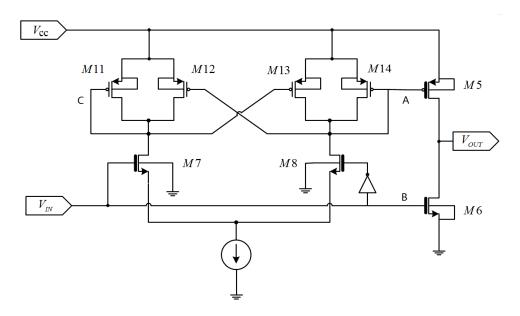

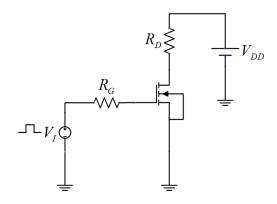

| 4.5  | Schematic of MOSFETs' gate driver $[2,16]$                                                 | 50 |

| 4.6  | Input signal and output signal of the gate driver                                          | 51 |

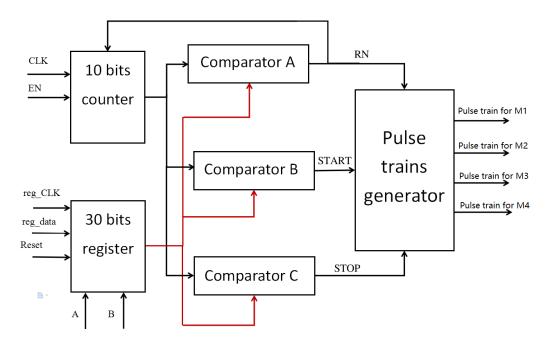

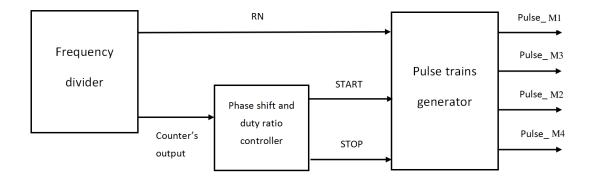

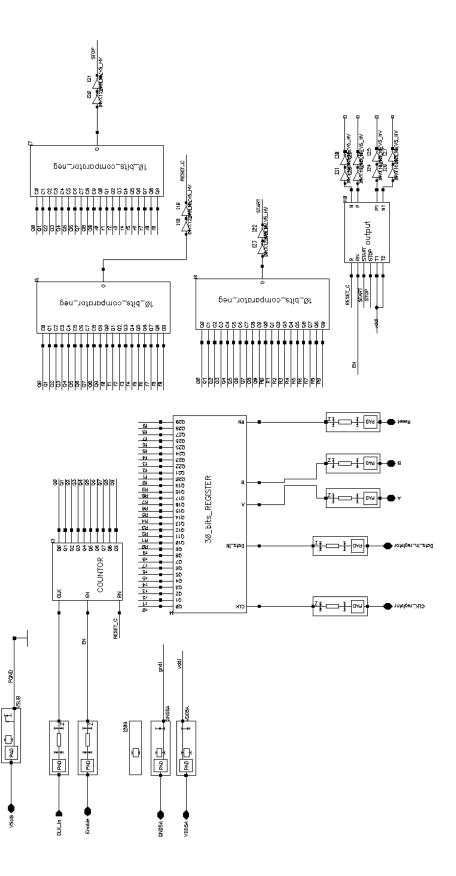

| 4.7  | Structure of the digital logic unit                                                        | 51 |

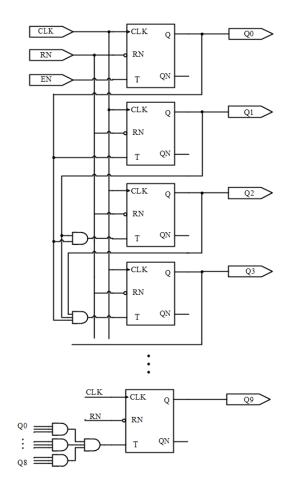

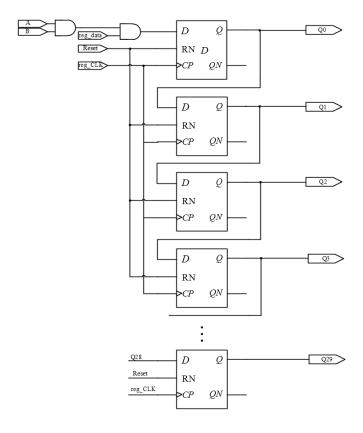

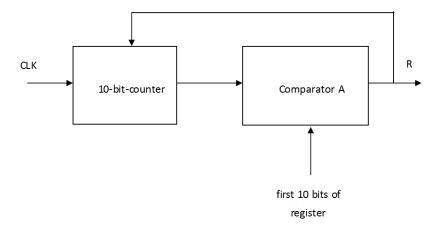

| 4.8  | Structure of 10-bit-counter                                                                | 53 |

| 4.9  | Schematic of 30-bit-register                                                               | 54 |

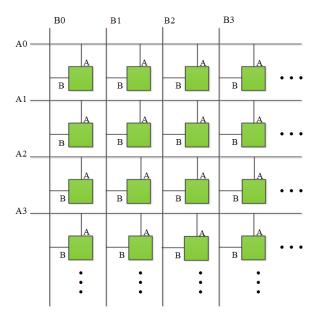

| 4.10 | Transducer array driving method                                                            | 54 |

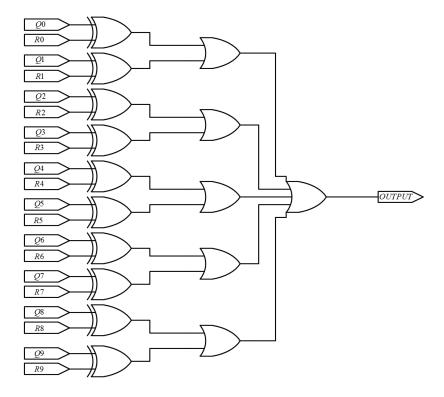

| 4.11 | Schematic of the 10-bit-comparator                                                         | 55 |

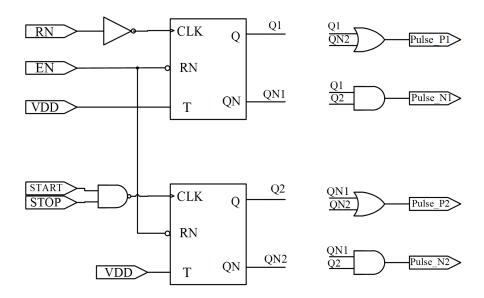

| 4.12 | Schematic of the pulse-trains-generator                                                    | 56 |

LIST OF FIGURES VI

| 4.13 | Block diagrams of the relationship of the frequency divider, phase shift and duty ratio                                                                            |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | controller and pulse train generator                                                                                                                               | 57 |

| 4.14 | Block diagram of the frequency divider                                                                                                                             | 57 |

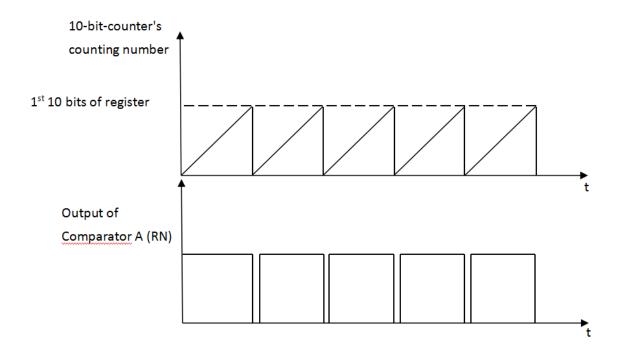

| 4.15 | Output diagrams of the frequency divider                                                                                                                           | 58 |

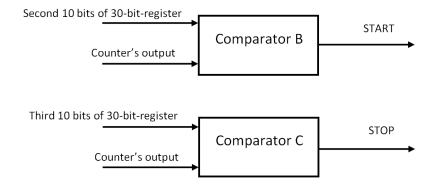

| 4.16 | Block diagram of the phase shift and duty ratios controller                                                                                                        | 59 |

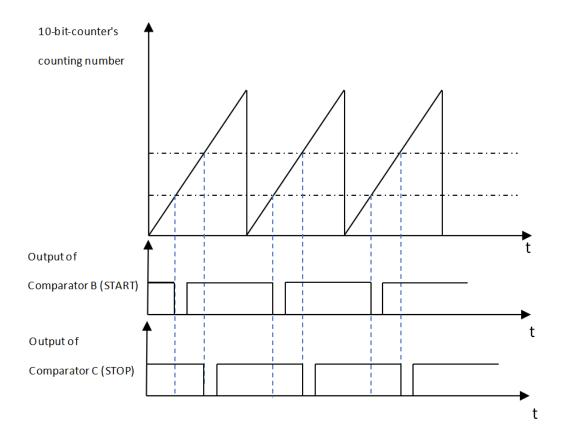

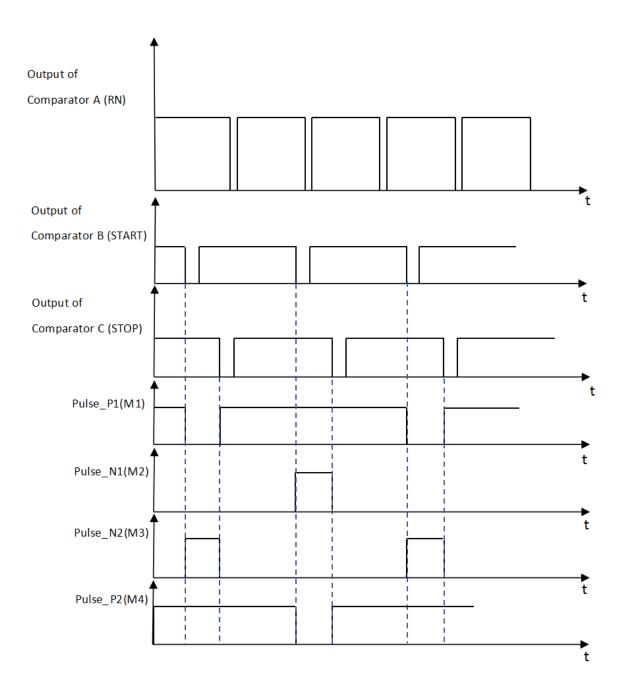

| 4.17 | Output diagrams of the phase shift and duty ratios controller                                                                                                      | 59 |

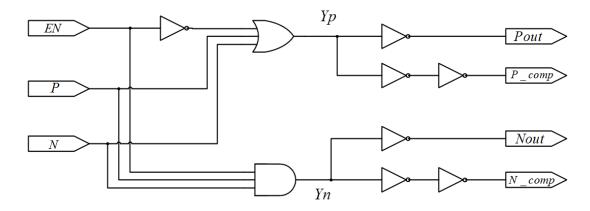

| 4.18 | Input and output diagrams of the pulse trains generator                                                                                                            | 61 |

| 4.19 | Schematic of the additional safety logic block [2]                                                                                                                 | 62 |

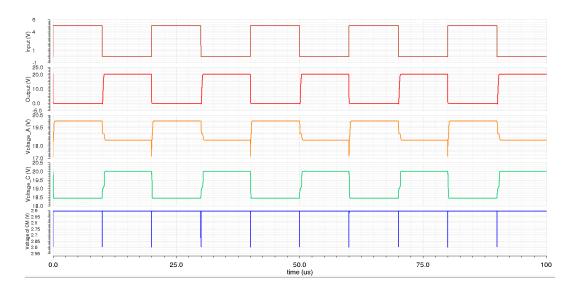

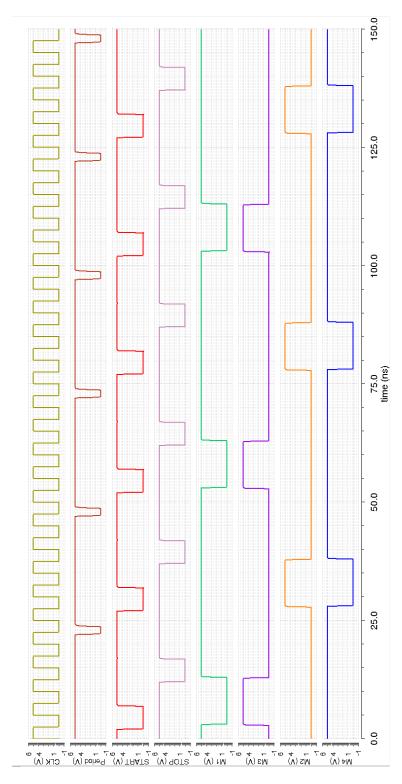

| 4.20 | Outputs waveforms of the digital logic unit, its input clock signal's frequency is                                                                                 |    |

|      | 200MHz, phase shift is 10%, duty ratio is $20\%$                                                                                                                   | 64 |

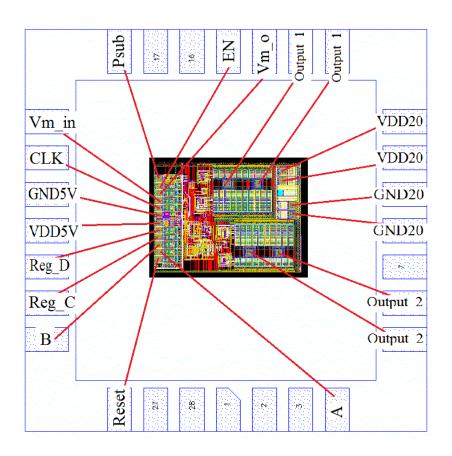

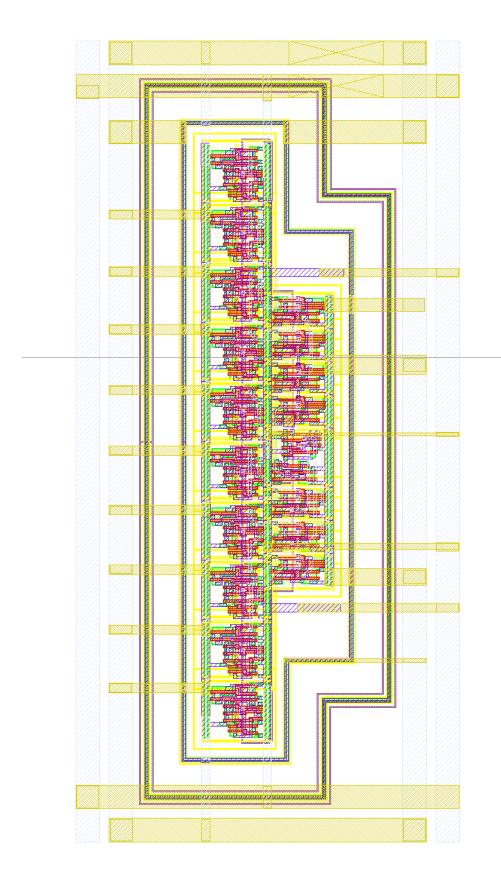

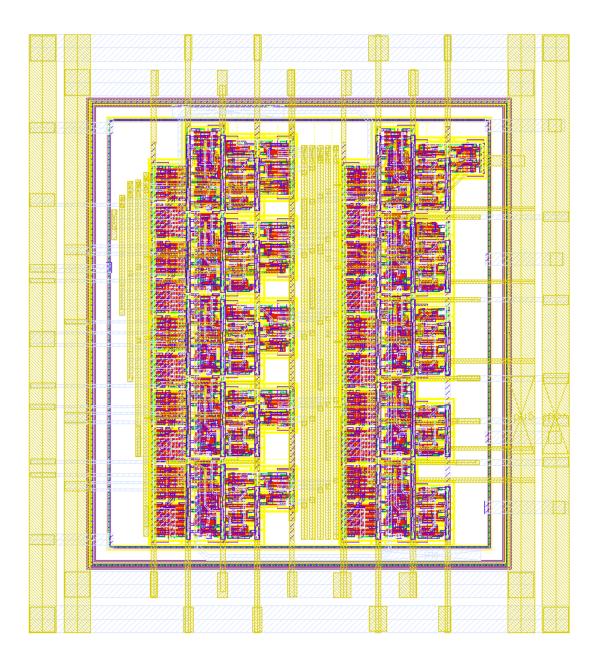

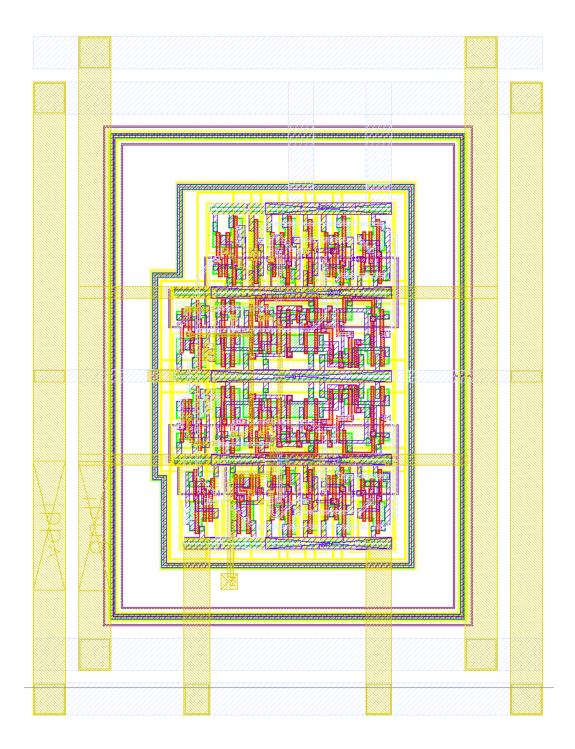

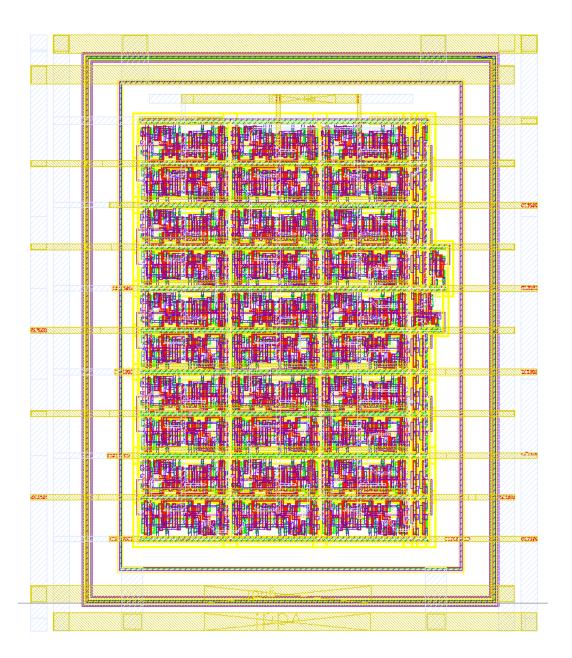

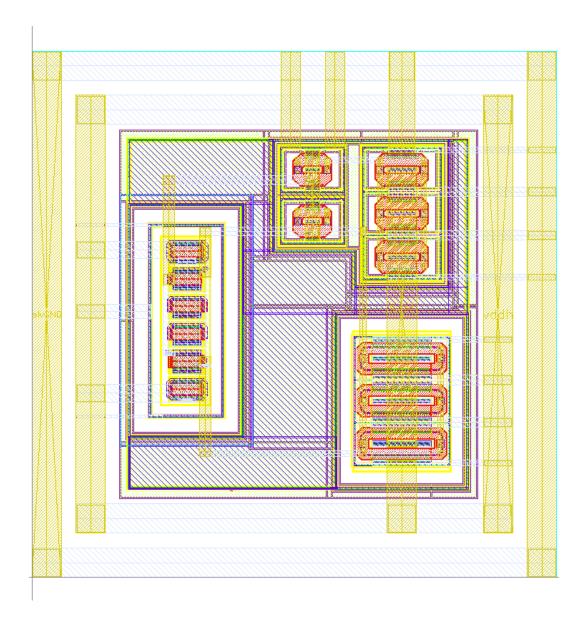

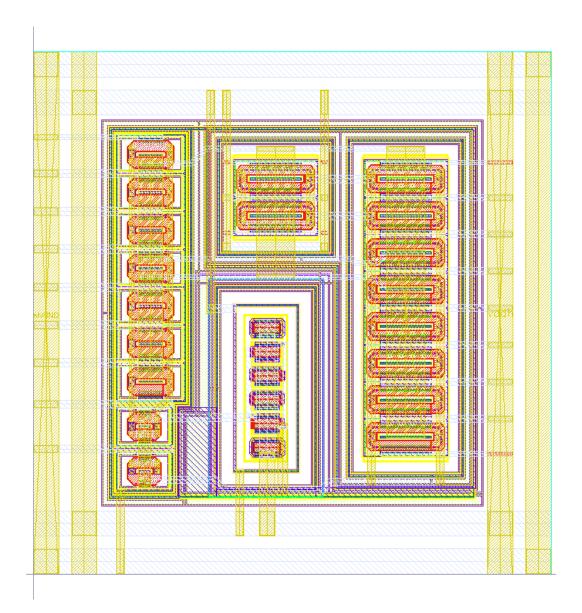

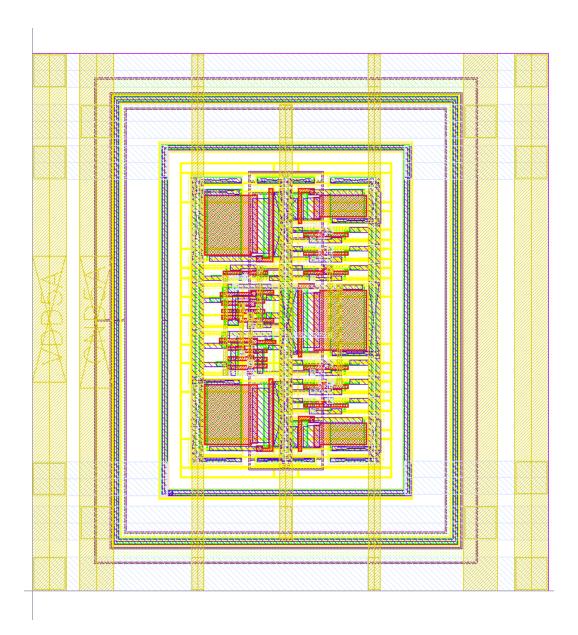

| 4.21 | Layout view of the driver                                                                                                                                          | 66 |

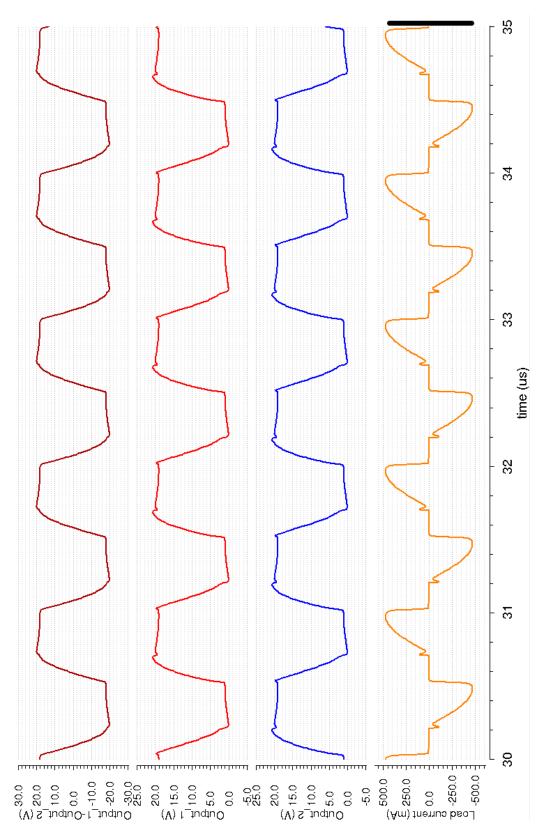

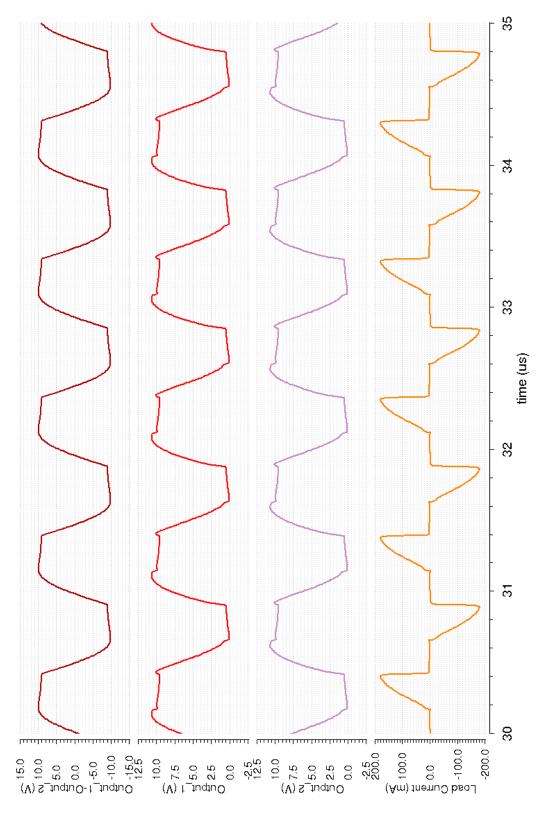

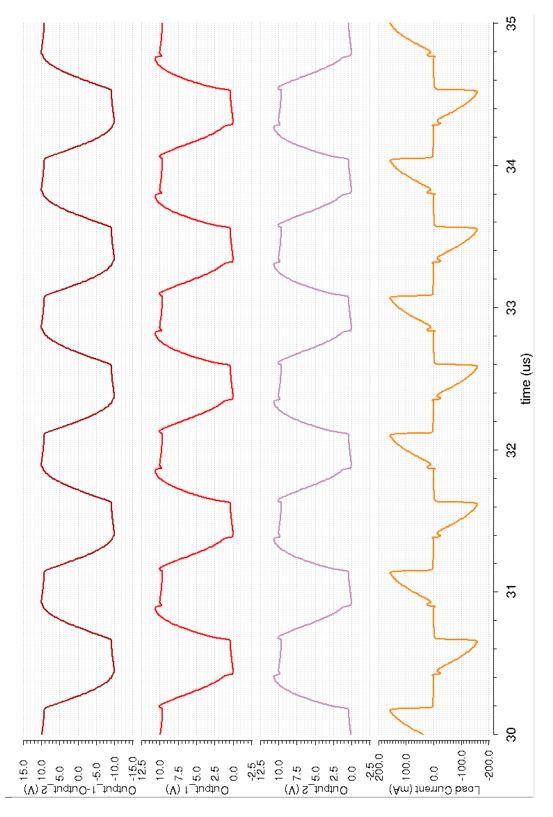

| 5.1  | Simulation results of the full-bridge Class-DE driver that is proposed in this the-                                                                                |    |

|      | sis. Brown: output voltage (Output1-Output2); Red: potential of Output1; Pink:                                                                                     |    |

|      | potential of Output2; Orange: load current                                                                                                                         | 68 |

| 5.2  | Simulation results of the half-bridge Class-DE driver that was designed by our group                                                                               |    |

|      | [5]. Brown: output voltage ; Red: load current $\dots \dots \dots$ | 69 |

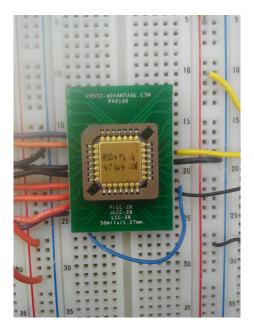

| 5.3  | Fabricated driver in a testing circuit                                                                                                                             | 70 |

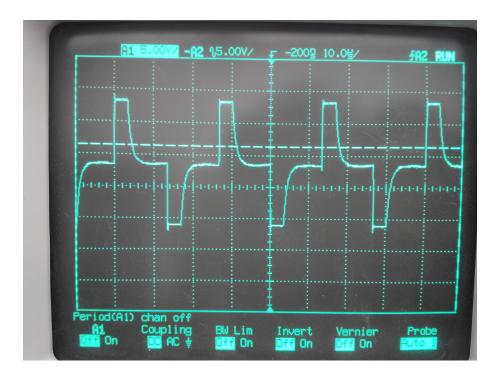

| 5.4  | Logic test result of the driver                                                                                                                                    | 71 |

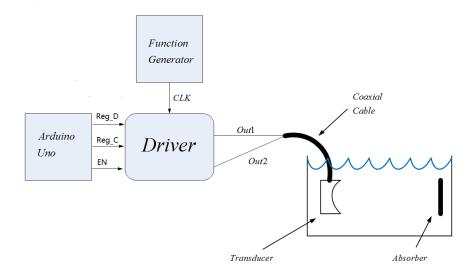

| 5.5  | Block diagram of the testing setup of the driver                                                                                                                   | 72 |

| 5.6  | Simulation results of driving the transducer with $C_{ext}=128~\mathrm{pF}$ by 1028 kHz, $0^\circ$ phase                                                           |    |

|      | shift and $25\%$ duty ratio pulse trains. Brown: output voltage (Output1-Output2);                                                                                 |    |

|      | Red: potential of Output1; Pink: potential of Output2; Orange: load current                                                                                        | 74 |

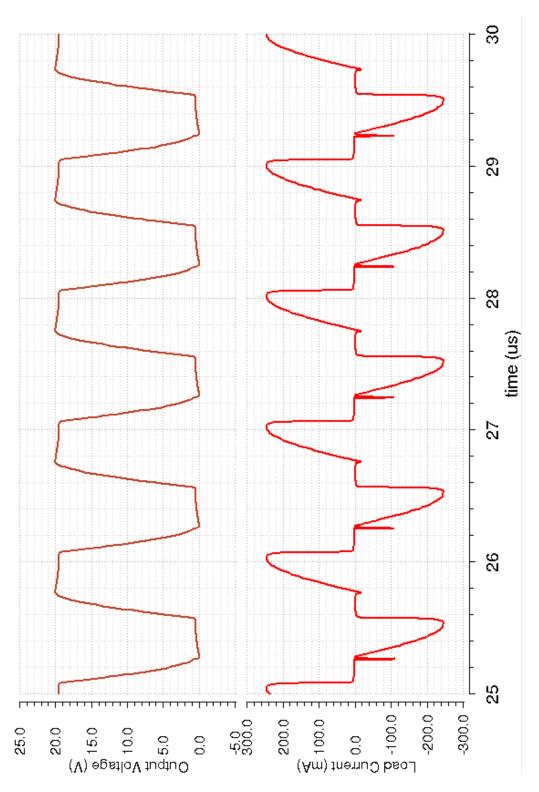

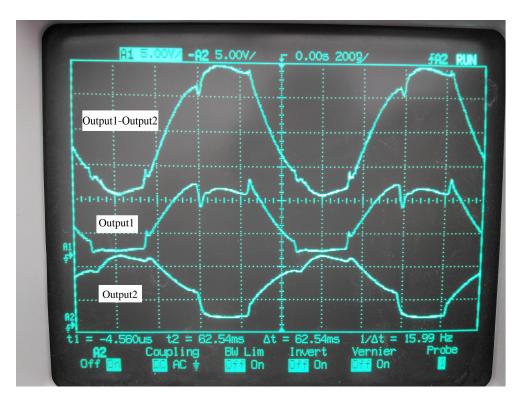

| 5.7  | Experimental result of driving the transducer by 1036 kHz and 25% duty ratio pulse                                                                                 |    |

|      | trains                                                                                                                                                             | 75 |

| 5.8  | Simulation results of driving the transducer with $C_{ext}=128~\mathrm{pF}$ by 1036 kHz, $0^\circ$ phase                                                           |    |

|      | shift and $25\%$ duty ratio pulse trains. Brown: output voltage (Output1-Output2);                                                                                 |    |

|      | Red: potential of Output1; Pink: potential of Output2; Orange: load current                                                                                        | 76 |

| A.1  | Pin diagram of the full-bridge Class-DE driver                                                                                                                     | 79 |

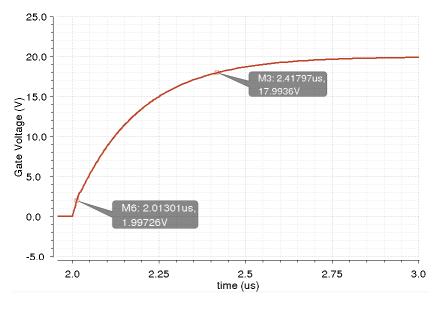

| B.1  | Gate capacitance extraction circuit                                                                                                                                | 81 |

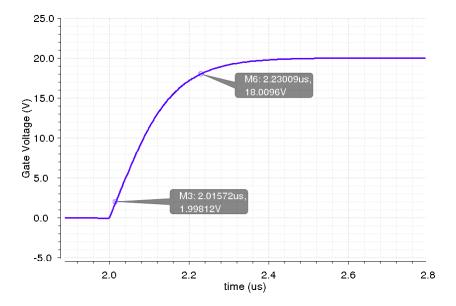

| B.2  | Gate voltage plot of NMOS                                                                                                                                          | 81 |

| B.3  | Gate voltage plot of PMOS                                                                                                                                          | 82 |

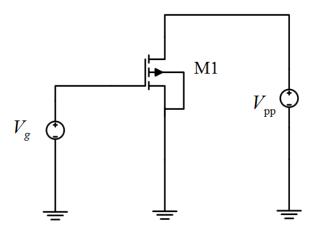

| B.4  | Schematic of a MOSFET's parameters extraction [2]                                                                                                                  | 83 |

LIST OF FIGURES VII

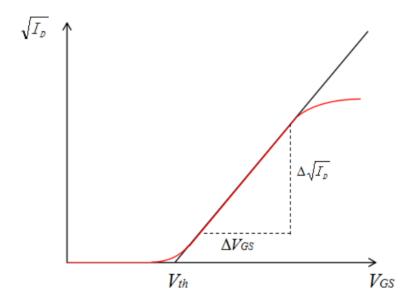

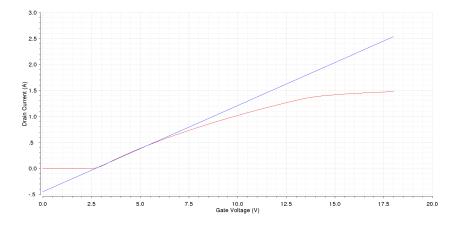

| B.5 | $\sqrt{I_D}$ plots of a real MOSFET and a theoretical model, the red line is the real MOS-                 |     |

|-----|------------------------------------------------------------------------------------------------------------|-----|

|     | FET's plot and the black line is the theoretical model's plot $[2]$                                        | 84  |

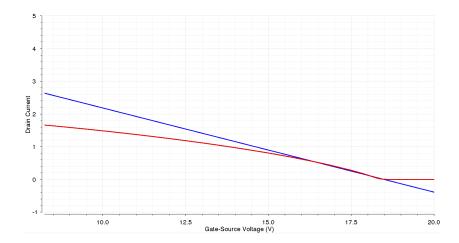

| B.6 | $\sqrt{I_D}$ plots the PMOS, the blue line is the theoretical squire root of drain current $\sqrt{I_{Dt}}$ |     |

|     | and the red line is the real model's squire root of drain current $\sqrt{I_D}$                             | 85  |

| B.7 | $\sqrt{I_D}$ plots the NMOS, the blue line is the theoretical squire root of drain current                 |     |

|     | $\sqrt{I_{Dt}}$ and the red line is the real model's squire root of drain current $\sqrt{I_D}$             | 85  |

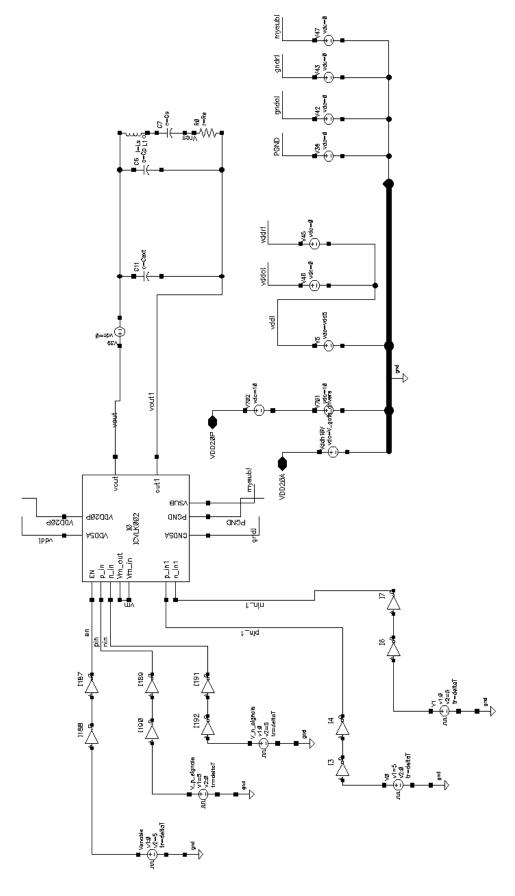

| C.1 | Block diagrams of simulation circuit of the full-bridge Class-DE amplifier                                 | 88  |

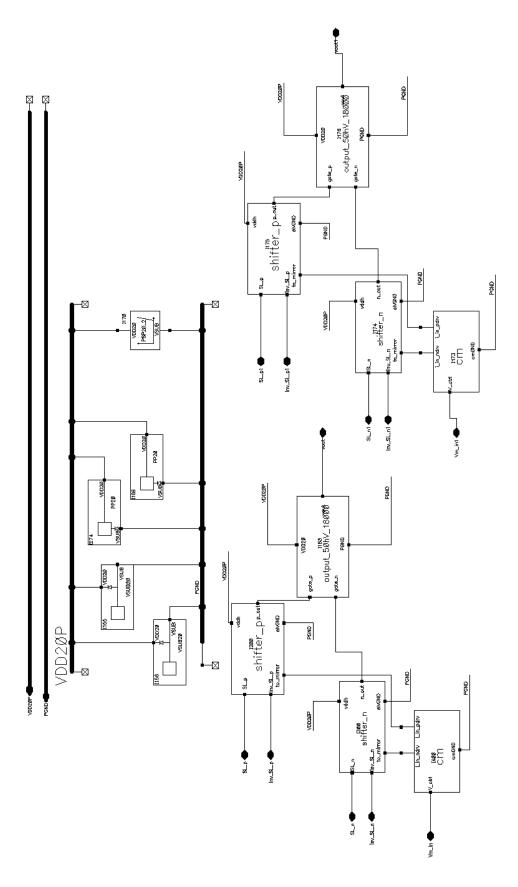

| C.2 | Block diagrams of the logic control unit                                                                   | 89  |

| C.3 | Block diagrams of the Class-DE amplifier with gate drivers                                                 | 90  |

| D.1 | Layout of the 10-bit-comparator                                                                            | 92  |

| D.2 | Layout of the 10-bit-counter                                                                               | 93  |

| D.3 | Layout of the pulse trains generator                                                                       | 94  |

| D.4 | Layout of the 30-bit-register                                                                              | 95  |

| D.5 | Layout of the NMOS's gate driver that designed by Wai Wong                                                 | 96  |

| D.6 | Layout of the PMOS's gate driver that designed by Wai Wong                                                 | 97  |

| D.7 | Layout of the gate drivers' current mirror that designed by Wai Wong $\ \ldots \ \ldots$                   | 98  |

| D.8 | Layout of a branch of Class-DE amplifier that designed by Wai Wong                                         | 99  |

| D.9 | Layout of the additional safety logic block that designed by Wai Wong                                      | 100 |

# List of Tables

| 1   | List of Symbols                                                                          | IX |

|-----|------------------------------------------------------------------------------------------|----|

| 2.1 | Equivalent circuit's parameters of an ultrasound transducer                              | 26 |

| 2.2 | Optimum Class-DE switching frequencies and duty ratios of the instance transducer.       | 27 |

| 2.3 | Equivalent circuit components' values of Tx.3                                            | 28 |

| 2.4 | DC supply power, output power and efficiency for transducer Tx.3                         | 29 |

| 2.5 | Comparison of some published works                                                       | 31 |

| 3.1 | $f_S, f_P$ and $ Z $ values of each element of Kivinen's transducer array                | 34 |

| 3.2 | Equivalent circuit parameters of all the six elements of Kivinen's transducer array $$ . | 34 |

| 3.3 | Operation frequencies and duty cycles of all elements in the transducer array $\dots$    | 35 |

| 3.4 | Simulation results of all the elements in the transducer array $\dots \dots \dots$       | 37 |

| 3.5 | External capacitance values of all the elements in Kivinen's transducer array $\dots$    | 40 |

| 3.6 | Efficiencies of all the elements that are driven at 1.0242MHz with $C_{ext}$             | 40 |

| 3.7 | Efficiencies of all the six elements that are driven at 1.0242MHz without $C_{ext}$      | 40 |

| 3.8 | Efficiencies of all elements which are driven by average frequency                       | 42 |

| 4.1 | Half-bridge Class-DE amplifier's width and length parameters [5]                         | 47 |

| 4.2 | Truth table of the additional safety logic block $[2]$                                   | 63 |

| 5.1 | Equivalent circuit parameters of the transducer [5]                                      | 67 |

| 5.2 | DC supply power, output power and efficiencies of driving the transducer by full-        |    |

|     | bridge and half-bridge Class-DE drivers                                                  | 70 |

| B.1 | Step signal responds of gate voltage of the PMOS and NMOS that used in the amplifier     | 81 |

| B.2 | Summary of extracted parameters values of the PMOS and NMOS                              | 86 |

LIST OF TABLES IX

Table 1: List of Symbols

| Symbols                   | Meaning                                                                     |

|---------------------------|-----------------------------------------------------------------------------|

| $\overline{Z}$            | Impedance                                                                   |

| $C_P$                     | Parallel capacitance                                                        |

| $C_S$                     | Series capacitance                                                          |

| $R_S$                     | Series resistance                                                           |

| $L_S$                     | Series inductance                                                           |

| $\omega$                  | Angular frequency                                                           |

| $\omega_r$                | Angular frequency obtained from real part of impedance                      |

| $\omega_x$                | Angular frequency obtained from imaginary part of impedance                 |

| $f_s$                     | Series resonance frequency                                                  |

| $\stackrel{f_p}{Y}$       | parallel resonance frequency                                                |

|                           | Admittance                                                                  |

| G                         | Real part of admittance                                                     |

| R                         | Real part of impedance                                                      |

| $V_{DS1}$                 | Voltage across the M1                                                       |

| $V_{DS2}$                 | Voltage across the M2                                                       |

| $i_1$                     | Instantaneous current of M1                                                 |

| $i_2$                     | Instantaneous current of M2                                                 |

| $i_3$                     | Instantaneous current of M3                                                 |

| $i_4$                     | Instantaneous current of M4                                                 |

| $i_C \ i_L$               | Instantaneous current of $C_p$<br>Instantaneous current of series capacitor |

| $\stackrel{\iota_L}{V_1}$ | The fundamental component of $V_{DS2}$                                      |

| $I_1$                     | The fundamental component of $i$                                            |

| $Z_L$                     | Load impedance                                                              |

| $Z_S$                     | Impedance of series branch                                                  |

| $\overset{\circ}{R_L}$    | Real part of $Z_L$                                                          |

| $X_L$                     | Imaginary part of $Z_L$                                                     |

| $f_r$                     | Frequency obtained from real part of impedance                              |

| $f_x$                     | Frequency obtained from imaginary part of impedance                         |

| D                         | Duty ratio                                                                  |

| $C_{ext}$                 | External capacitance                                                        |

| $C_{ext,r}$               | External capacitance solved from real part of impedance                     |

| $C_{ext,x}$               | External capacitance solved from imaginary part of impedance                |

| $\phi$                    | Phase angle related to the duty ratio                                       |

| $v_{OUT}$                 | Output voltage                                                              |

| $C_{gate}$                | Gate capacitance of MOSFET                                                  |

| $C_{ox}$                  | Oxide capacitance per unit area<br>Gate oxide thickness                     |

| $t_{ox} = \epsilon$       | Permittivity                                                                |

|                           | Permittivity Permittivity of free space                                     |

| $\epsilon_0$              | Relative permittivity                                                       |

| $rac{\epsilon_r}{L_D}$   | Lateral diffusion                                                           |

| $\mathbf{W}$              | Width of MOSFET's gate                                                      |

| L                         | Length of MOSFET's gate                                                     |

| $I_{Dt}$                  | Theoretical drain current                                                   |

| $I_D$                     | Drain current                                                               |

| $V_{GS}$                  | Voltage across the gate and source                                          |

| $V_{th}$                  | Threshold Voltage                                                           |

| $R_{ch}$                  | Channel resistance of MOSFETs                                               |

# Chapter 1

# Introduction

# 1.1 Objectives and Motivation of this study

High Intensity Focused Ultrasound (HIFU) is a surgical technique that ablates human tissues by using the thermal energy that is generated by focused ultrasound [1,2]. It is a kind of non-invasive technique that can be used for the ablation of tumours or other kind of damaged tissues in human bodies. The ablation process is very precise. A movement of patient's body would cause the displacement of the focal zone of the HIFU, and then other tissues that are around the tumour could be damaged. In order to avoid that, Magnetic Resonance Imaging (MRI) can be used [1,2] to guide the HIFU operation by monitoring the tissues' temperature, so that the focal zone can be located and the patient's body movements can be compensated in real time. Multi-element ultrasound transducer array is required to allow electronic steering of the focal point. Every element in the transducer array is driven by different phase information to create sufficient acoustic pressure level on the focal zone [1,2]. But the transducer driver cannot include any magnetic components, such as inductors, because they would interfere with the MRI.

Wai Wong has designed an integrated CMOS ultrasound transducer driver for the HIFU operation [1]. The output stage of it is a Class-DE RF amplifier whose efficiency is over 90%, it can deliver 1W of power from the power source to the loaded transducer and it does not have any magnetic components. In this design, the driver needs a pair of pulse trains to drive the PMOS and the NMOS in Class-DE amplifier, so we must provide programmed external pulse trains for the driver.

If we generate the pulse trains inside of the driver, the connection setup of it will be highly simplified. Also, for more flexibility the driver should deliver more power to the load. Therefore, the objective is to design an integrated CMOS transducer driver that can generate the pulse trains and

deliver more than 1W of power to the load transducer. All the challenges of designing the intended driver are listed below:

- 1. The driver should occupy minimum possible area.

- 2. We cannot use any magnetic components because of MRI conditions.

- 3. The phase angle, duty ratios and operating frequencies of Class-DE amplifier's driving pulse trains can be programmable.

- 4. It should be able to deliver more than 1W of power to the load, if possible

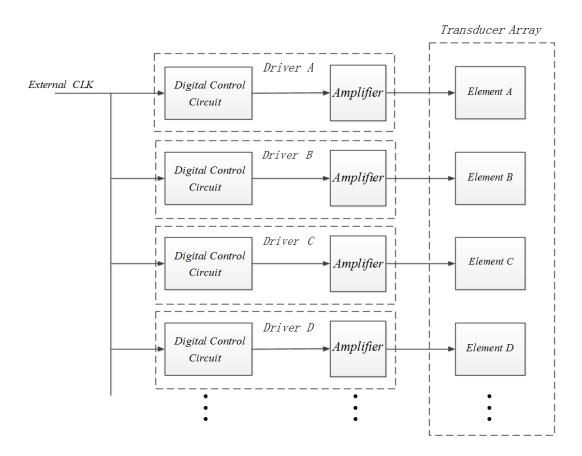

Figure 1.1: Block diagram of driving an Ultrasound transducer array

Figure 1.1 shows the intended block diagram of driving a transducer array. Each element of the array will be driven by a driver and a digital control circuit will make the pulse trains, phase shifts and duty ratio programmable. The control circuit along with a full-bridge Class-DE amplifier will be fabricated on a single chip. All drivers will be driven by an external clock signal and share a

common power source. Also we would like to make a feedback from each driver to measure power delivered to load.

# 1.2 Thesis Overview

In this thesis, Chapter 2 describes the applicability of switched RF amplifiers, especially Class-DE amplifier, characterization of ultrasound transducer which are used in HIFU application, as well as some published works on the subject of this project. Chapter 3 discusses two strategies of driving a transducer array in Class-DE mode. Chapter 4 discusses the characteristics and design procedure of full-bridge Class-DE amplifiers and its driving strategies and also includes the digital logic control unit of the driver and the functions of each component. Chapter 5 summarizes the experimental results of the driver.

# Chapter 2

# Background Information and Literature Review

# 2.1 Introduction

In common ultrasound therapy, people usually use analog amplifiers to drive the ultrasound transducers, especially Class-A RF amplifiers. But the analog amplifiers' efficiency is not high enough to preclude overheating. So in many published works on this subject, it is proposed to use switched amplifiers to drive the transducers. In this Chapter, the characterization of ultrasound transducers, some switched amplifiers and some published works on this subject will be reviewed.

This Chapter is organized as follows: Section 2.2 reviews the background information about characterization of ultrasound transducers; Section 2.3 covers the topologies of some switched amplifiers; Section 2.4 reviews some published works; Section 2.5 introduces the previous design by our group and Section 2.6 summarizes drivers that were reviewed in this chapter.

# 2.2 Characterization of Ultrasound Transducer

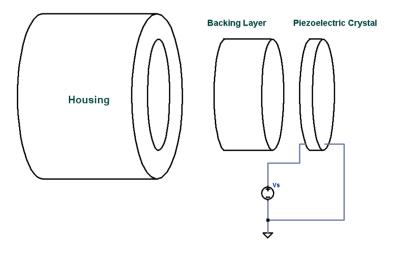

The ultrasound wave that is used in HIFU applications is often generated by piezoelectric transducers. The structure of a transducer is shown in Figure 2.1. As we can see in this Figure, the right most component is called piezoelectric crystal which is the resonator, and the ultrasound wave generator. Electrodes are coated on both sides of resonator for the electrical connections. The leftmost part which is the outer case is called housing. It protects the internal circuitry and resonator from the physical environment.

Figure 2.1: Structure of an ultrasound transducer [2]

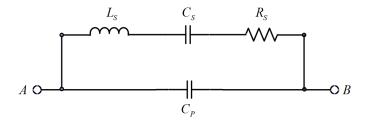

Figure 2.2: BVD equivalent circuit of a resonator near its resonance frequency [1,2]

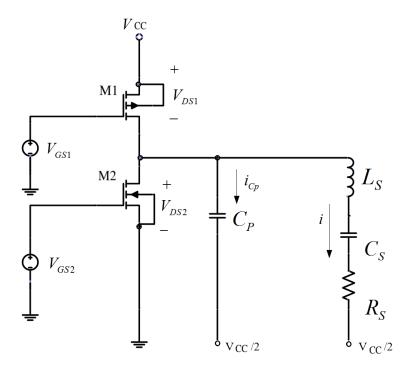

The Butterworth Van Dyke (BVD) equivalent circuit of a piezoelectric resonator near its own resonance frequency is shown in Figure 2.2 [1, 2]. This equivalent circuit is a combination of a parallel capacitance  $C_p$  and a series resonance branch. The parallel capacitance  $C_p$  describe the static capacitor of the piezoelectric resonator and is determined by the physical characteristics of the resonator. The series branch which is made up by  $L_s$ ,  $C_s$  and  $R_s$  represent the mechanical oscillator near the resonator's resonance frequency. The two terminals A and B that we can see in the Figure 2.1 are the input terminals of the resonator. Usually, one of them is connected to the output of the driver and another one is connected to the ground or the reference point of the circuit. Mathematically, the impedance of the BVD equivalent circuit can be expressed as below:

$$Z = \frac{\frac{1}{j\omega C_P} \left(\frac{1}{j\omega C_S} + R_S + j\omega L_S\right)}{\frac{1}{j\omega C_P} + \frac{1}{j\omega C_S} + R_S + j\omega L_S}$$

(2.1)

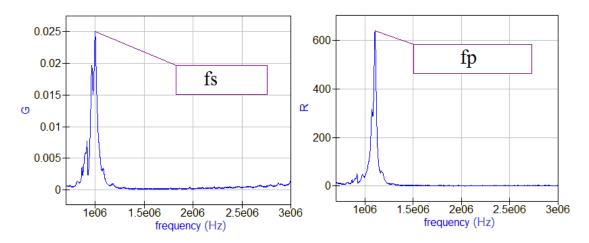

Figure 2.3: Impedance and admittance plots of the equivalent circuit of transducers

where the  $\omega$  is the angular frequency and the  $j=\sqrt{-1}$ . In Equation (2.1), we can see that the impedance of this equivalent circuit is a function of the frequency  $f(\omega=2\pi f)$ . The admittance of the impedance is denoted by Y(Y=1/Z). If we let the real part of impedance Re(Z)=R and real part of admittance Re(Y)=G, and then plot them in a certain frequency range, we obtain Figure 2.3. In Figure 2.3,  $f_p$  is the parallel resonance frequency in which R (the real part of the resonator's impedance) reaches its maximum value [4];  $f_s$  is the series resonance frequency when G (the real part of admittance of the resonator) is at its maximum [4].

The expressions of the values of all components [1,3] are shown below:

$$C_S = C_P \left[ \left( \frac{f_P}{f_S} \right)^2 - 1 \right] \tag{2.2}$$

$$L_S = \frac{1}{(2\pi f_S)^2 C_S} \tag{2.3}$$

$$C_P = \frac{-Im(Z_S)}{2\pi f_S |Z_S|^2} \tag{2.4}$$

$$R_S = \frac{|Z_S|^2}{Re(Z_S)} \tag{2.5}$$

where the  $Z_s$  is the resonator's impedance at its series resonance frequency. Once  $C_p$  is found using Equation (2.4), apply Equations (2.2), (2.3) and (2.5) to find the values in the series resonance branch.

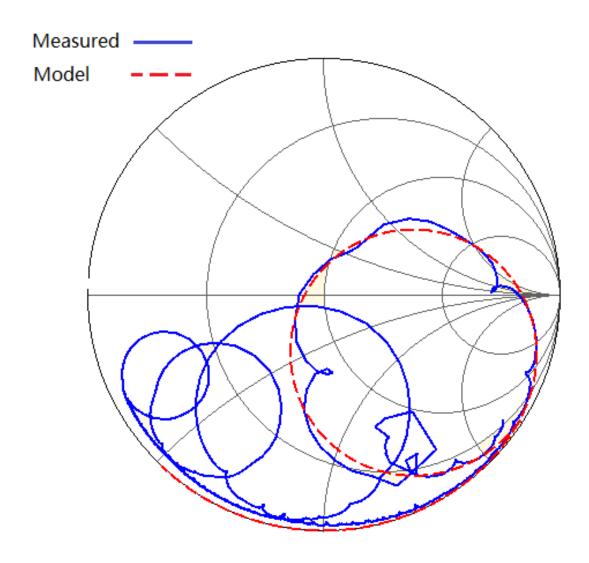

By using a vector network analyzer, we can get the reflection coefficient plots of the transducer's resonator on a Smith chart (Figure 2.4). In this figure, the blue solid line is the measured reflection coefficient plot and the red, dashed line is the equivalent circuit model's reflection coefficient plot.

# 2.3 Switched RF Amplifiers

In RF amplifier family, there are two categories of amplifier: 1. Analog RF amplifiers; and 2. Switched amplifiers. The analog amplifiers (such as Class-A, Class-B and Class-AB amplifiers) power efficiency are not as high as the switched amplifiers, so the overheating problem is the main drawback of analog amplifiers. Because of that reason, analog amplifiers do not meet our requirements, and this section reviews switched amplifiers. In contrast, the power efficiency of switched amplifiers (such as Class-D, Class-E and Class-DE amplifiers) is very high, they can achieve almost 100% theoretically.

## 2.3.1 Class-D Amplifiers

Due to their simple circuitry and high efficiency, switched amplifiers are commonly used in many applications. In contrast with analog amplifiers, a switched amplifier operates its transistors as switches. When the switch is turned on, it will apply all voltage to the load. When the switch is turned off, no voltage will be applied to the load [6].

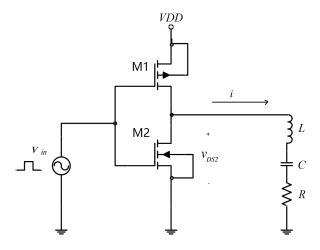

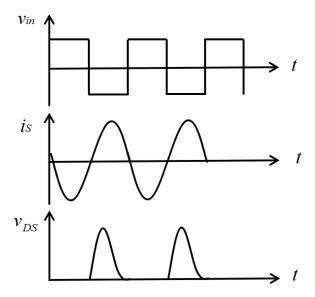

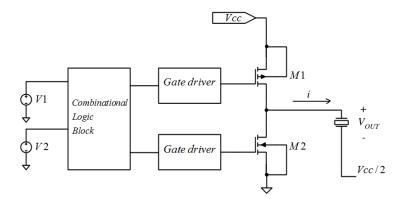

Figure 2.5 shows the schematic of a Class-D CMOS RF amplifier, in which a PMOS MOSFET  $M_1$  and a NMOS MOSFET  $M_2$  are used as switching devices. This kind of amplifier circuitry can be integrated for high-frequency applications, such as RF transmitters for wireless communications.

Figure 2.4: Plots of measured reflection coefficient and equivalent circuit model's reflection coefficient on a Smith Chart

Figure 2.5: Schematic of the CMOS integrated Class-D RF amplifier [6]

Figure 2.6: Input and output waveforms of the CMOS integrated Class-D RF amplifier [6]

It only requires one driver. However, cross-conduction of both transistors during the MOSFETs transitions may cause spikes in the drain currents. Non-overlapping gate-to-source voltages may reduce this problem, but driver will become very complex. The peak-to-peak value of the gate-to-source drive voltage which is also the input signal  $V_{GS}$  is equal or close to the dc supply voltage  $V_{DD}$ , like in CMOS digital gates. Therefore, this circuit is appropriate only for low values of the dc supply voltage  $V_{DD}$ , usually below 20V. At high values of the dc supply voltage  $V_{DD}$ , the gate-to-source voltage should also be high, which may cause voltage breakdown of the gate [6].

The operating procedure of the Class-D amplifier is the transistor M1 and M2 will be turned on alternatively with 50% duty ratio in the operation, to output the square wave that charges and discharges the load. The load of Class-D amplifiers is a series resonance circuit whose quality factor Q is high enough so that the load current is sinusoidal. The harmonics at the output of the Class-D amplifier are thus suppressed. Theoretically the efficiency of the Class-D amplifier can reach 100%, but in practice the efficiency is reduced because of the switching loss. When the transistors are turned on, the voltage across the transistors are not zero, and also the derivative of the voltage are not zero. The input and output waveforms of Class-D amplifiers are shown in the Figure 2.6. [6]

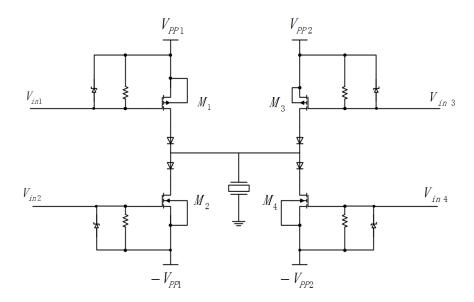

Figure 2.7: Topology of the CMOS integrated Class-D full-bridge RF amplifier

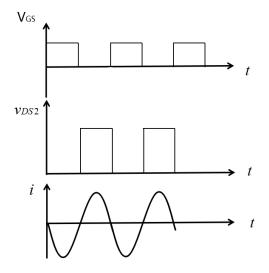

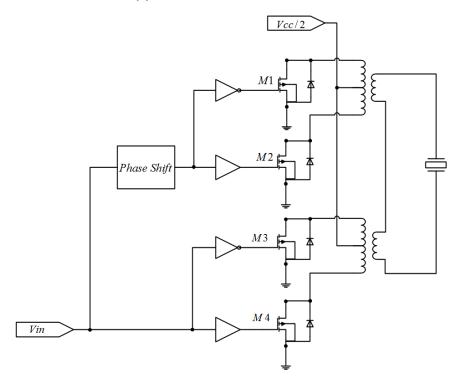

The schematic of full-bridge Class-D amplifier is shown in Figure 2.7, it consist of 4 transistors M1, M2, M3 and M4. This full-bridge Class-D amplifier's operating strategy is the same as the half-bridge one that we discussed before. M1 and M2 are turned on and off alternatively at same

time as the half-bridge Class-DE amplifier that discussed before, the main difference is the M3 will be turned on and off at same time as M1 and M4 will be turned on and off at same time as M2. So the output voltage swing will be doubled compared to the half-bridge Class-DE amplifier (from  $-V_{DD}$  to  $+V_{DD}$ ). [6]

In general, the Class-D amplifier is a very popular choice for ultrasound therapy. However, it need a tuned filter to attenuate the harmonics to achieve the highest efficiency which will interfere with the MRI operation. [2]

## 2.3.2 Class-E Amplifiers

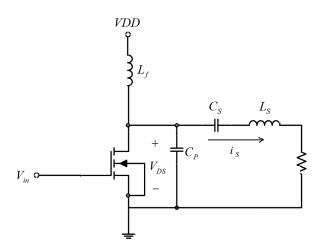

Figure 2.8: Topology of the CMOS integrated Class-E RF amplifier.

The Class-E amplifier is also called Class-E DC-AC inverter. The schematic of it is shown in Figure 2.8. It consists of a MOSFET operating as a switch, LCR series resonance circuit, shunt capacitor  $C_P$  and a choke inductor  $L_f$ . In this circuit the choke inductance  $L_f$  is assumed to be high enough to eliminate the AC current ripple on the DC supply  $V_{DD}$ 's current. A small inductance will result in a large current ripple. [6]

Circuit with hard-switching operation of semiconductor components, such as the Class-D amplifiers and digital gates, always suffer from switching losses. The voltage waveform in these circuits decrease abruptly from a high value (often equal to the dc supply  $V_{DD}$ ) to almost zero, when a switching device, such as a MOSFET, turns on. When the switch is turned on, the current is circulating through the switch's on-resistance and all the stored energy is lost in the on-resistance as heat. This switching loss energy is independent of the transistor on-resistance. [6]

The switching losses can be avoided if the voltage across the transistor  $V_{DS}$  is zero. The main

Figure 2.9: Input and output waveforms of the CMOS integrated Class-E RF amplifier. [6]

idea of the Class-E RF amplifier is that the transistor turns on as a switch at zero voltage, resulting in zero switching loss and high efficiency. The Class-E amplifier contains a single transistor, it turns on at zero voltage switching (ZVS), and it also turns on at zero derivative switching (ZDS). In general, this type of operation is called soft-switching. The input and output waveforms of the Class-E amplifier are shown in Figure 2.9. [6]

The major drawback of the Class-E amplifier is that it needs a large choke inductance to eliminate the DC current ripples. Because of that it is not a suitable choice for the integrated driver to be used in MRI conditions. [2]

# 2.3.3 Class-DE Amplifier

The schematic of the Class-DE amplifier is shown in Figure 2.10. It is the combination of the topology of Class-D amplifiers and the switching condition of Class-E amplifiers. The theoretical efficiency is 100%. In Figure 2.10, the M1 and M2 turns on and off with a duty ratio of 25% which means that the duty ratio of the dead time is also 25% to let the ZVS and ZDS happen. It doesn't have any switching loss theoretically. Our previous design which was proposed by Wong et al. [2] used this kind of RF amplifier as the output stage of the driver. A detailed analysis is provided in Section 2.4.

Figure 2.10: Schematic of the CMOS integrated Class-DE RF amplifier  $\,$

Figure 2.11: Schematic of the step-up driving circuit

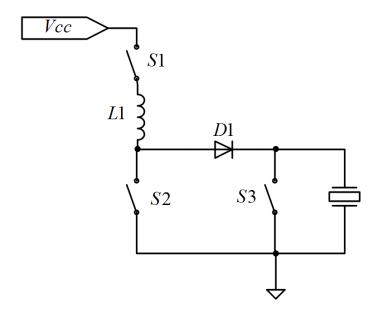

# 2.3.4 Step-up Driving Circuit

The step-up driving circuit's schematic is shown in the Figure 2.11. It is derived directly from the classical step-up DC/DC circuit which is also known as boost-buck converter. The only difference is the charge storage capacitor is replaced by the parallel capacitor in the equivalent circuit of the transducer  $(C_P)$ . The voltage on the transducer terminals depends in the pumping pulse train switching frequency, duty ratio, inductance  $L_1$  and the switch  $S_1$ ,  $S_2$  on-resistance [8].

The operating process is: first, both the  $S_1$  and  $S_2$  turns on to charge up the inductance  $L_1$ . Then  $S_2$  turns off to let the energy that was stored in the inductor to be transferred to the transducer. At last,  $S_1$  turns off and  $S_3$  turns on to discharge the transducer. Because it includes 3 transistors in the step-up driving circuit, its timing and control circuit can be very complicated and the diode used in this circuit introduces additional losses [8].

# 2.3.5 Flyback Topology

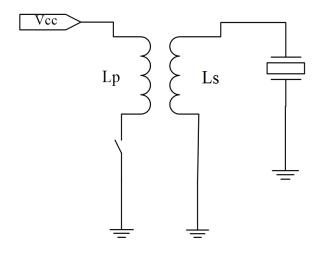

The schematic of the flyback topology is shown in Figure 2.12., in this figure, the  $L_P$  and  $L_S$  operate as a transformer,  $L_P$  connects the supply voltage and switch and  $L_S$  connects ground and transducer. By turning switch on and off, that will make the voltage change across the transducer [8].

The major advantage of the flyback topology is that it just needs one transistor to generate the pulse signal to the transducer [2]. But a major drawback of this topology is that this circuit has a secondary winding resonance generated by the transducer parasitic capacitance  $C_P$ , which will cause long ringing after the switch is open and it needs a transformer which is a magnetic component, thus it cannot be used in the MRI conditions [8].

#### 2.3.6 Push-pull driving circuit

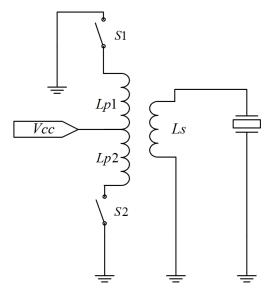

The push-pull topology is almost the same as the flyback topology, the schematic is shown in Figure 2.13. This topology uses two switches that turn on and off at different times. At start, both switches are turned off, then the  $S_1$  is turned on for the half of the transducer excitation pulse period. After that it is turned off, but the  $S_2$  is turned on [8].

In this topology, the transformer is used to match the impedance of the transducer to maximize power transfer, but it will occupy a large portion of area and it cannot be used in the MRI conditions, so this kind of topology will not be applied in our design.

Figure 2.12: Topology of the flyback transducer driver [8]

Figure 2.13: Schematic of the Push-pull driving circuit

# 2.4 Literature Review

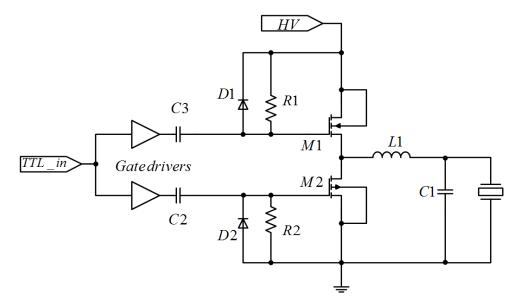

Hall and Cain [9] proposed a Class-D amplifier, whose efficiency is 90% and output power is 20 W, operating frequency is 1 MHz, for a 512-channel transducer array. Its schematic is shown in Figure 2.14. The two transistors in this schematic form an inverter with the addition of transistor gate drivers. The duty ratio is decided by the input TTL signal which is a square wave. Tuned filter inductor  $L_1$  and capacitor  $C_1$  cancel out the higher harmonics of the square wave. [9]

The advantage of this topology is simplicity and low cost. But there are two resistors ( $R_1$  and  $R_2$ ) in this design, which will occupy a lot of area if we use them in an integrated circuit. Also the inductor  $L_1$  in the filter cannot be used in the MRI conditions. So this kind of topology is not suitable to our objective.

Figure 2.14: Schematic of the transducer driver which was proposed by Cain and Hall [9].

Tang and Clement [7] discussed the harmonic cancellation technique for a therapeutic ultrasound transducer in HIFU applications. The schematic of the driver that they used is shown in Figure 2.15. It contains two power converters in cascade and the operating frequency is 1 MHz. [7]

In their work, they point out that driving a piezoelectric ultrasound transducer in HIFU applications with a signal that contains harmonics will distort the shape of the ultrasound focal zone. This is because the harmonic in the driving signal will lead the transducer to generate unwanted sidelobes in the acoustic field. These sidelobes have extra energy and will distort the shape of the focal zone. So the harmonic cancellation technique was introduced to solve this problem. [7]

The harmonic cancellation technique uses a pre-calculated firing angle of the driving signal which

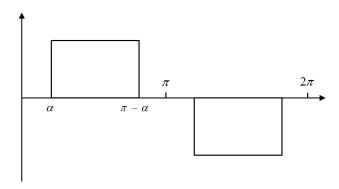

is a square wave pulse train. As shown in Figure 2.16, the square wave has a firing angle of  $\pi/3$  which eliminates the third harmonic. This technique does not require an LC filter circuit. [7]

However this design requires two transformers in the circuit which is not suitable for MRI. Also this harmonic cancellation technique must be very precise. Rise time and fall time must be minimized, otherwise, the unwanted harmonic will appear at the output of the driver. So this design is not suitable for our objective. [7]

Figure 2.15: Schematic of the driver that is used by Tang and Clement [7]

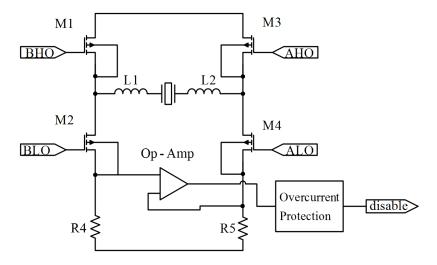

Yang and Xu [10] used a Class-D full-bridge amplifier to drive an Audio Beam system. The schematic of this driver is shown in Figure 2.17. The switching operating frequency is 600 kHz, and the Audio Beam System can generate a highly concentrated audio signals between 20 kHz to 60 kHz. There are two resistors  $R_1$  and  $R_2$  and an operational amplifier in this circuit to cooperate with the gate driver IC to make an over current protection for the MOSFETs at the output stage. Inductors  $L_1$  and  $L_2$  are connected with the transducer to make a reduction of instantaneous current that flows through the loaded transducer.

Because of the inductors and the resistors in this design, it will occupy a large portion of area and interfere the operation of MRI, so we cannot employ this design in our project.

D. Zhao et al. [11] proposed a high voltage pulser for ultrasound medical imaging applications. The schematic of their design is shown in Figure 2.18. This circuit is a Class-D amplifier with a

Figure 2.16: Input waveform of the driver that is used by Tang and Clement [7]

Figure 2.17: Schematic of driver that is proposed by Yang and Xu [10].

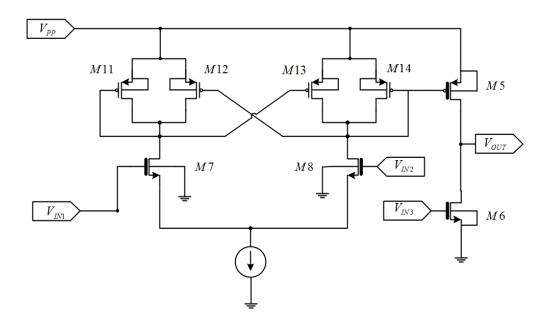

MOSFET's gate driver. It has three inputs  $V_{IN1}$ ,  $V_{IN2}$  and  $V_{IN3}$ . All of them are low voltage signals, and Vpp is the high voltage supply.

The operating procedure is: first, if the  $V_{IN1}$  and  $V_{IN3}$  are logic high, the  $V_{IN2}$  is logic low, so the M6, M7, M11 and M13 will be turned on and the gate voltage of M5 is logic high, so the M5 is turned off. Since the M5 is off and M6 is on, the output voltage is logic low. For same reason, if  $V_{IN1}$  and  $V_{IN3}$  are logic low and  $V_{IN2}$  is logic high, the output voltage is logic high (30V).

In this design, the authors didn't provide efficiency results, but Class-D amplifiers can achieve almost 90%. However, as we mentioned before, the switching loss of the Class-D amplifier is high; also the duty ratios and phase shift of the output pulse trains cannot be programmable.

Figure 2.18: Schematic of high voltage pulser that is proposed by Zhao and Tian [11].

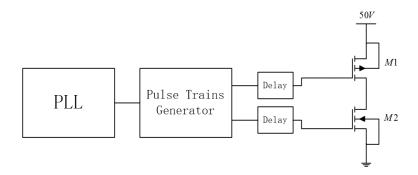

A. Bozkurk and O. Farhanieh [12] designed a driver IC for Catheter ablation system. Their driver's block diagram is shown in Figure 2.19. They integrate a phase locked loop in the driver to produce a high-frequency clock signal for a pulse train generator, the pulse train generator produces two driving pulse trains with programmed phase shift and duty ratio for the output stage which is a Class-D amplifier.

The main feature of this design is it generates clock signal and driving pulse trains inside of the driver, the setup process of driving a transducer array will be much simplified by using this feature. Also they didn't use any magnetic components in this driver. But the driver's output power is just 530mW, is not high enough, and we don't known its power efficiency.

Figure 2.19: Block diagram of A. Bozkurk and O. Farhanieh's driver IC [12]

K. Moro and J. Okada [13] designed a staircase-wave drive circuit to drive therapeutic array transducers. Their circuit is shown in Figure 2.20 and the waveforms of the schematic are shown in Figure 2.21. In the schematic, the  $V_{PP1}$  is higher than  $V_{PP2}$ . As shown in the Figure 2.21, the M3 is turned on first, so the output voltage is equal to  $V_{PP2}$ , and then M1 is turned on and off for a while, it generates a higher voltage pulse which is equal to  $V_{PP1}$ . When the M1 is turned off, the output voltage waveform falls back to  $V_{PP2}$ . In this process, a half period of staircase-wave is presented at the output. If we turned on and off M3 and M4 by the same procedure, a negative staircase-wave will be presented at the output. By using this stair-wave, the third and fifth harmonics will be reduced to zero, but the switching loss cannot be eliminated. It also needs a large portion of area to fit the 4 resistors in this design if we fabricate this circuit in a chip.

# 2.5 Previous Design by Our Group

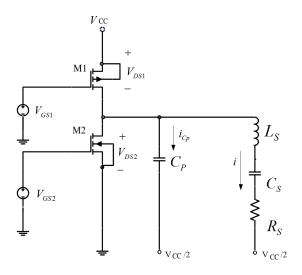

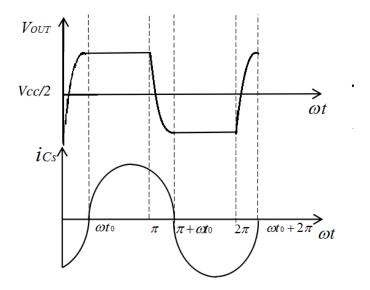

Our previous ultrasound transducer driver design was proposed by W. Wong *et al.* [1,2,5]. A Class-DE amplifier is driven by two gate drivers (Figure 2.22). This driver is implemented by using AMS H35B4 CMOS technology.

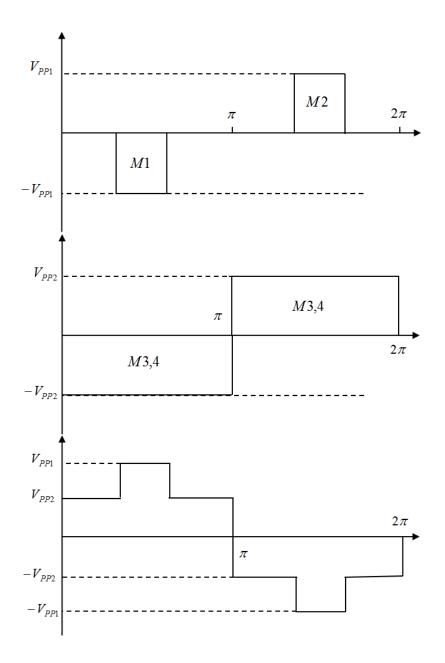

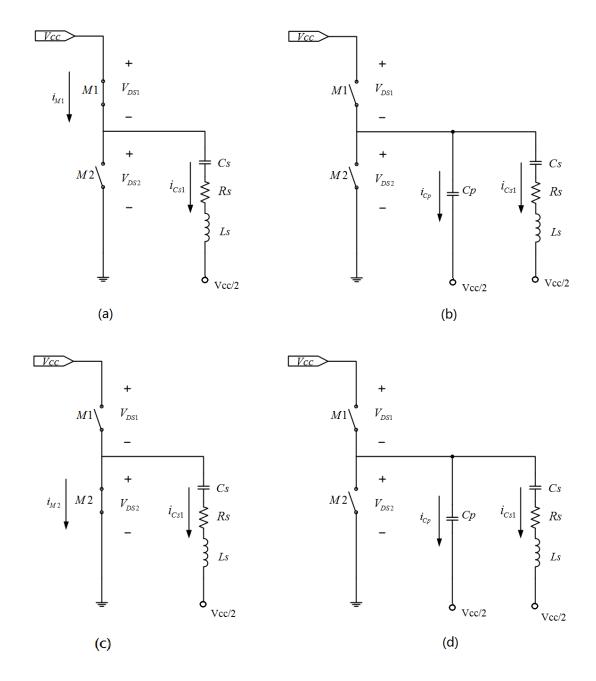

The operation of the Class-DE amplifier can be divided in 4 intervals. Figure 2.23 shows the voltage and current waveforms of the whole operation period and Figure 2.20 shows the equivalent circuits for each interval.

#### Interval 1

Between  $\omega t_0$  radians and  $\pi$ . Transistor M1 turns on and M2 turns off. The equivalent circuit is shown in Figure 2.24(a). The current  $i_{M1}$  slowly increases from 0 until its peak and then decreases until  $\omega t = \pi$ . The drain potential of M2 is at highest potential  $(V_{cc})$  in this whole interval, so no

Figure 2.20: Schematic of staircase-wave driver that is proposed by K. Moro and J. Okada. [13]

current flow through the parallel capacitor  $C_P$ . The current  $i_{M1}$  will be the only current that charges the series resonance branch [2]. In this interval the output voltage is  $V_{cc}$ .

#### Interval 2

Between  $\pi$  and  $\pi + \omega t_0$ . Both transistors M1 and M2 are turned off. The equivalent circuit of this interval is shown in Figure 2.24(b). There is no current flow through the transistors in this interval. So the parallel capacitor will provide the current to the series resonance branch, because the  $L_s$  and  $C_s$  maintains the continuity of the load current. Because of that, the load current falls down sinusoidally to 0 at  $\pi + \omega t_0$ . Since the  $C_P$  charges the series resonance branch in this interval, the voltage across the M2 will be decreased slowly, from  $V_{cc}$  until 0 at  $\pi + \omega t_0$ . The  $V_{DS1}$  will be decreased to  $-V_{cc}$  at this moment.

### Interval 3

Between  $\pi + \omega t_0$  and  $2\pi$ . In this interval the M2 is turned on and M1 is turned off. The equivalent circuit of this interval is shown in Figure 2.24(c). M2 is turned on when the  $V_{DS2}$  is zero, so the ZVS and ZDS conditions are reached. Because of the M2 being turned on, the  $V_{DS1}$  is maintained at  $-V_{cc}$  and no current flows through the  $C_P$ . The series resonance branch will discharge through M2, its current keeps decreasing until its lowest peak.

Figure 2.21: Input and output voltage waveforms of the staircase-wave driver [13]

Figure 2.22: Schematic of driver that is proposed by Wai Wong. [5]

Figure 2.23: Output waveforms of half-bridge Class-DE amplifier [5]

Figure 2.24: Equivalent circuits of Class-DE amplifier in each interval. [6]

#### Interval 4

Between  $2\pi$  and  $2\pi + \omega t_0$ . In this interval both M1 and M2 are turned off. The equivalent circuit of this interval is shown in Figure 2.24(d). Because of  $C_s$  and  $L_s$ , the series resonance branch keep discharging in this interval. Because of M2 being turned off, the load current will flow through  $C_P$  to charge it and let the  $V_{DS2}$  increase, at the end of this interval which is at  $2\pi + \omega t_0$ , the  $V_{DS2}$  will reach its highest point that is  $V_{cc}$ . After  $2\pi$ , its the fifth interval which is same as the first one, the M1 will be turned on and M2 will be turned off. At the moment that M1 is turned on which is at  $\omega t = 2\pi + \omega t_0$  the  $V_{DS1}$  is equal to zero which matches the ZVS and ZDS conditions again.

If we want to drive an ultrasound transducer by using this design, we must decide its operating frequency (f) and corresponding duty ratio (D) to maximize the power transmission efficiency. The expression of the output voltage and load current of the Class-DE amplifier in the interval 2 and 4 is [14]:

$$v_{OUT} = V_{CC} \frac{2cos(\omega t - \phi) - (1 + cos\phi)}{2(1 - cos\phi)} \quad t \in [0 + k\pi, t_0 + k\pi], k = 0, 1, 2...$$

(2.6)

$$i = I_m sin(\omega t - \phi) \tag{2.7}$$

where the  $\phi$  is an angle that relate to the duty ratio D by equation  $\phi = \pi(1 - 2D)$ , the  $\phi$  cannot be zero, because when  $\phi = 0$  the duty ratio is 50%, then the Class-DE condition is no longer exist. Then we can get the fundamental component of  $V_{OUT}$  and load current i by using Fourier analysis [14]:

$$V_{1} = \frac{4}{T} \left( \int_{0}^{t_{0}} v_{DS2}(t) exp(-j\omega t) dt + \int_{t_{0}}^{T/2} \frac{V_{CC}}{2} exp(-j\omega t) dt \right)$$

(2.8)

$$I_1 = \frac{2}{T} \int_0^T I_m \sin(\omega t - \phi) \exp(-j\omega t) dt$$

(2.9)

The fundamental components of the output voltage  $V_{OUT}$  and load current i are shown below (please note that  $V_{CC} = \frac{1}{C_P} \int i(t)dt$ ) [14]:

$$V_1 = V_{CC} \frac{\phi cos\phi - sin\phi - j\phi sin\phi}{\pi (1 - cos\phi)}$$

(2.10)

$$I_1 = -\frac{\omega C_P V_{CC}(\sin\phi + j\cos\phi)}{1 - \cos\phi}$$

(2.11)

If we substitute the equation (2.10) and (2.11) to equation Z = V/I, we can get the expression of the load impedance  $Z_L$  [5,14]:

$$Z_L = \frac{V_1}{I_1} = \frac{1 - \cos(2\phi)}{2\pi\omega C_P} + j\frac{2\phi - \sin(2\phi)}{2\pi\omega C_P}$$

(2.12)

In Equation 2.12, the real part and imaginary part of  $Z_L$  are [5]:

$$R_L = \frac{1 - \cos(2\phi)}{2\pi\omega C_P} \tag{2.13}$$

$$X_L = \frac{2\phi - \sin(2\phi)}{2\pi\omega C_P} \tag{2.14}$$

From Equation (2.1)

$$Z_L = R_S + j\omega L_S + \frac{1}{j\omega C_S} \tag{2.15}$$

So, let the  $R_L = R_S$ ,  $X_L = j\omega L_S + \frac{1}{j\omega C_S}$  and solve them for frequency [5]:

$$f_r = \frac{1 - \cos(2\phi)}{4\pi^2 C_P R_S} \tag{2.16}$$

$$f_x = \frac{1}{2\pi} \sqrt{\frac{2\phi - \sin(2\phi)}{2\pi C_P L_S} + \frac{1}{C_S L_S}}$$

(2.17)

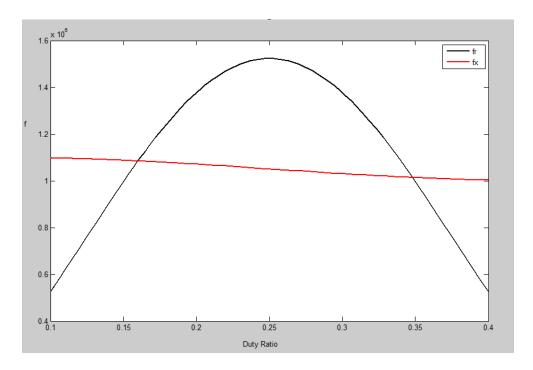

where the  $f_r$  is the frequency that we get from the real part of the impedance and  $f_x$  is the frequency that we get from the imaginary part of impedance. Equations (2.16) and (2.17) are functions of duty ratio D. If we plot these two equations in a duty ratio range [0.1,0.4], we can get the operation frequency and corresponding duty ratio of the Class-DE amplifier. For instance, in Figure 2.25 we plot  $f_r$  and  $f_x$  for a transducer that has the equivalent circuit values that are shown in Table 2.1: In this Figure the black line represents the plot of the  $f_r$  and red line represent the

$$\begin{array}{c|cccc} C_P & C_S & L_S & R_S \\ 827pF & 183pF & 139uH & 40.25\Omega \end{array}$$

Table 2.1: Equivalent circuit's parameters of an ultrasound transducer.

plot of  $f_x$ . As we can see, there are two intersection points of these two lines in this figure, these are

Figure 2.25: Variations of  $f_r$  and  $f_x$  with duty ratio of an ultrasound transducer

the points that Class-DE mode switching happens  $(f_r = f_x)$ . If we substitute equations (2.16) and (2.17) into  $f_r = f_x$ , we can find the optimum Class-DE switching frequencies and the corresponding duty ratios for this transducer. The optimum frequencies and corresponding duty ratios are shown in Table 2.2.

$$\begin{array}{c|cc}

D_1 = 0.160 & f_1 = 1084kHz \\

D_2 = 0.348 & f_2 = 1014kHz

\end{array}$$

Table 2.2: Optimum Class-DE switching frequencies and duty ratios of the instance transducer.

Because of the series resonance frequency of this transducer being  $f_s = 1/(2\pi\sqrt{L_sC_s}) \approx 1MHz$ , the operating frequency must be closest to it. That means we should use the  $f_2$  and  $D_2$  as the operating frequency and duty ratio. Also, because the  $D_2$  is larger than  $D_1$ , using  $D_2$  and  $f_2$  will let the transistors turned on time is longer than using  $D_1$  and  $f_1$ , which means more output power [5].

The efficiency of the transducer driver designed in [5] is 90% and there is no magnetic components, such as inductors and transformers, in this circuit, which means that we can use this driver in MRI conditions. Also the circuitry of this design is very simple, it won't occupy a large portion of area, so we can integrate it in a chip. The power will be delivered to the transducer by the driver is over 1 W which means we have achieved our minimum goal [5].

However, in this design the driving signals, which are pulse trains, of both transistors in the Class-DE amplifier are not generated by the driver itself. Instead external signals must be provided to the transducer driver. Because of that, the connection setup of the driver would be very complex in a large transducer array. If we want to decrease the complexity of the connection setup, we should internally generate the pulse trains that drive the switches of the Class-DE amplifier. The phase shift and duty ratios should be digitally programmable through an interface that is common to all drivers in an array (phase shifts determines when  $\phi$ isgetstarted and duty ratio determines the value of  $\phi$ ).

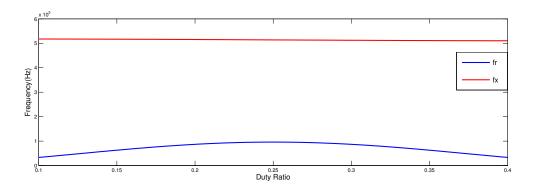

Some of transducers do not have Class-DE switching points, which means that they cannot be driven by Class-DE amplifiers. For instance, a transducer such as the one described in Table 2.3(Tx.3) [15].

| $C_P(pF)$ | $C_S(pF)$ | $L_S(mH)$ | $R_S(k\Omega)$ |

|-----------|-----------|-----------|----------------|

| 473       | 15        | 6.5       | 1.116          |

Table 2.3: Equivalent circuit components' values of Tx.3

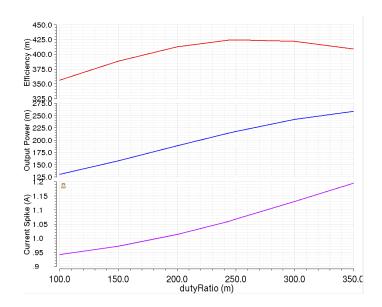

If we substitute these values to the equation 2.16 and 2.17 and plot them, we obtain curves of  $f_r$  and  $f_x$  that do not intersect (see Figure 2.26. In this case, if we want to drive this transducer by using Class-DE amplifiers, either an external matching network is required or the amplifier has to be driven in sub-optimal conditions near the series resonance frequency of the transducer, since at the series resonance frequency the transducer can get highest power delivery. Due to the MR environment concern, we can not use an external matching network in this case, which means driving it in sub-optimal condition is the only choice. In order to find the best duty ratio in this case, a duty ratio sweep can be used. Figure 2.27 shows the effect of duty ratio on efficiency, output power and current peak when the transducer is driven at the series resonance frequency. We can then use this sweep to use the operating duty cycle that allow for the maximum efficiency despite the sub-optimum condition.

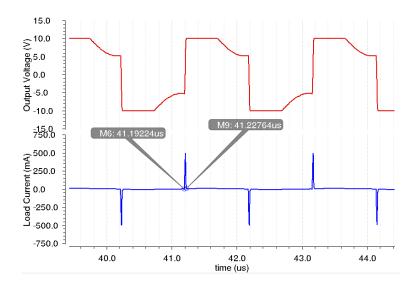

As we can see in this figure, the transducer Tx.3's efficiency reaches its maximum when duty ratio is near 0.25, so we choose 0.25 as the operating duty ratio for driving the transducer Tx.3. The output waveforms are shown in Figure 2.28. The amplifier is not operating in Class-DE mode and the output current waveform has high peaks, caused by the MOSFETs turning on when the voltage across the drain and source is not zero. The average current peak value is 1.06A, the current peaks width  $(41.22764\mu s - 41.19224\mu s = 0.0354\mu s)$  is shown in this Figure. Table 2.4 summarizes DC supply power, output power and efficiency for transducer Tx.3.

Figure 2.26:  $f_r$  and  $f_x$  plots of transducer Tx.3

Figure 2.27: Effect of duty ratio on efficiency, output power and current peak with variable duty ratios

| DC supply power(mW) | Output power (mW) | Efficiency(%) |

|---------------------|-------------------|---------------|

| 524                 | 227               | 43.3          |

Table 2.4: DC supply power, output power and efficiency for transducer Tx.3

2.6. SUMMARY 30

Figure 2.28: Output waveforms for transducer Tx.3

# 2.6 Summary

Overall, the Class-DE amplifier that was used in [5] is more suitable for our objectives than others. Because of that, the works that are presented in this thesis intend to upgrade that design to include the phase shift, driving frequency and duty ratios as programmable parameters. Furthermore, we intend to make the driver capable of delivering more power to the transducer. The comparison of the reviewed works is shown in Table 2.5.

2.6. SUMMARY 31

| Topology or Reference                             | Waveforms       | Efficiency | Power             | Comments                                                                                |

|---------------------------------------------------|-----------------|------------|-------------------|-----------------------------------------------------------------------------------------|

| Hall and Cain's design [9]                        | PWM Wave        | Over 90%   | 20W               | Need a LC matching network.                                                             |

| Tang and Clement's design [7]                     | Sinusoidal Wave | 90%        | Unknown           | Needs a transformer.                                                                    |

| Yang and Xu's design [10]                         | PWM             | Unknown    | Unknown           | Needs a inductor                                                                        |

| Zhao et al.'s design [11]                         | Square Wave     | Unknown    | Unknown           | Switching loss is high                                                                  |

| Moro and Okada's<br>design [13]                   | Staircase Wave  | Unknown    | Unknown           | Switching loss is<br>high and need a<br>large portion of<br>area for the resis-<br>tors |

| A. Bozkurk and<br>O. Farhanieh's de-<br>sign [12] | Square Wave     | Unknown    | $530 \mathrm{mW}$ | Output power is not high enough                                                         |

| W.Wong and<br>C.Christoffersen's<br>design [2,5]  | Class-DE Wave   | 90%        | 1W                | Duty ratios and phase shifts non-programmable                                           |

Table 2.5: Comparison of some published works

# Chapter 3

# Strategy to Drive a Transducer array in Class-DE Mode

Figure 3.1: Multi-element ultrasound transducer array that was designed by J. L. Kivinen [4]

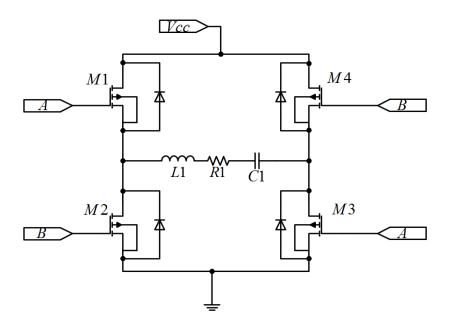

In last chapter, it was stated that the half-bridge Class-DE amplifier proposed in [5] is suitable to the objectives, it can deliver enough power and the efficiency is high. If we want to apply this ultrasound transducer driver in a MRI conditions for HIFU applications, we must use it to drive a multi-element transducer array which might include over 1000 elements. Since the transducers in

Figure 3.2: Half-bridge Class-DE amplifier which was proposed by Wai Wong [1,2,5]

an array are not exactly equal, the optimum driving parameters will be different for each individual transducer. However, all these elements will be driven at the same frequency. Therefore, a strategy must to be developed to drive an ultrasound transducer array with elements which have different optimum driving frequencies.

In this Chapter, we will use an ultrasound transducer array designed by J. L. Kivinen [4] (Figure 3.1) and the half-bridge Class-DE amplifier proposed by Wai Wong [1,5] (Figure 3.2). To develop the multi-element transducer array's driving strategy. Although this transducer array's elements can be used in HIFU applications, but it cannot focus the acoustic waves because of their arrangement pattern. It is however a good model to help us derive an array driving strategy since it has multiple piezoelectric elements.

The outline of this Chapter is: Section 3.1 introduced a transducer array and derived its equivalent circuit parameters; Section 3.2 introduced two strategies to drive a transducer array; The Section 3.3 summarizes this Chapter.

# 3.1 Characterization of the Transducer Array

We can plot each element's real part of the impedance and the real part of admittance of Kivinen's transducer array by using a vector network analyzer to find the series resonance frequency  $(f_S)$  and the parallel resonance frequency  $(f_P)$  of each element and their magnitude of impedance  $(Z|_{\omega=\omega_S}=R+jX)$ . The  $f_S$ ,  $f_P$  and |Z| are shown in Table 3.1.

Based on these parameters we can get all the equivalent circuit value of these six elements by

| Element      | $f_S(\mathrm{kHz})$ | $f_P(\mathrm{kHz})$ | $R(\Omega)$ | $X(\Omega)$ |

|--------------|---------------------|---------------------|-------------|-------------|

| A            | 997.5               | 1102.5              | 38.6        | 8.04        |

| В            | 997.0               | 1100.0              | 45.32       | 8.65        |

| $\mathbf{C}$ | 1000.0              | 1110.0              | 42.3        | 7.78        |

| D            | 1000.0              | 1110.0              | 38.4        | 9.27        |

| E            | 1000.0              | 1110.1              | 40.8        | 7.16        |

| F            | 1000.0              | 1110.3              | 38.0        | 8.82        |

|              |                     |                     |             |             |

Table 3.1:  $f_S$ ,  $f_P$  and |Z| values of each element of Kivinen's transducer array

using the Equations 2.2 to 2.5, all the parameters of are shown in Table 3.2, the differences among transducers can be observed in Table 3.1 and 3.2:

| Transducers     | $C_P(pF)$ | $C_S(pF)$ | $L_S(uH)$ | $R_S(\Omega)$ |

|-----------------|-----------|-----------|-----------|---------------|

| A               | 827       | 183       | 139       | 40.25         |

|                 | © <b></b> | 100       | 100       | 10.20         |

| D               | coo       | 150       | 167.0     | 45.20         |

| В               | 699       | 152       | 167.8     | 45.32         |

|                 |           |           |           |               |

| $^{\mathrm{C}}$ | 669       | 155       | 163.04    | 43.73         |

|                 |           |           |           |               |

| D               | 945       | 219       | 115.43    | 40.64         |

| D               | 540       | 213       | 110.40    | 10.01         |

| П               | 004       | 1 7 4     | 164.00    | 40.00         |

| $\mathbf{E}$    | 664       | 154       | 164.33    | 42.06         |

|                 |           |           |           |               |

| $\mathbf{F}$    | 922       | 214       | 118.31    | 40.05         |

|                 |           |           |           |               |

Table 3.2: Equivalent circuit parameters of all the six elements of Kivinen's transducer array

# 3.2 The Transducer Array Driving Strategies

We can get the optimum operation frequency and duty cycles (a transducer will reach its maximum efficiency when it is driven by its optimum frequency and duty ratio) for all elements in the transducer array using Equations (2.16) and (2.17). They are shown in the Table 3.3. If every element is driven

| Transducer   | Duty Cycle | Operation Frequency(kHz) |

|--------------|------------|--------------------------|

| A            | D = 0.348  | f = 1014                 |

| В            | D = 0.354  | f = 1012                 |

| $\mathbf{C}$ | D = 0.361  | f = 1014                 |

| D            | D = 0.328  | f = 1024                 |

| E            | D = 0.366  | f = 1013                 |

| F            | D = 0.334  | f = 1022                 |

Table 3.3: Operation frequencies and duty cycles of all elements in the transducer array

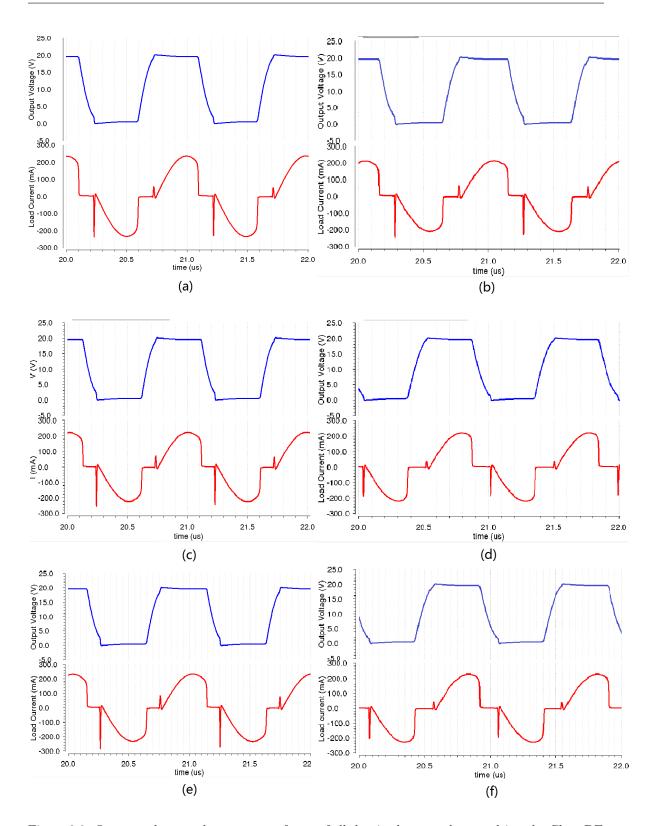

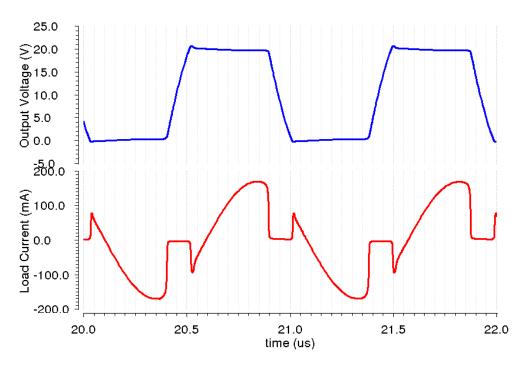

by its own optimum frequency and duty cycle separately, the output voltage and load current waveforms are shown in Figure 3.3. As we can see, all the elements are driven in Class-DE mode, but there are some small spikes on the output current waveform, because the input pulse trains need a rise time or fall time to reach their highest value and lowest value to turn on the transistors so that the transistors cannot be turned on at the exact time that they should be turned on. The efficiency when all elements are driven by their own optimum frequencies and duty cycles is shown in Table 3.4 In the table, DC supply power is the power that is provided by power supply and output power is the power that is delivered to the transducer. As we can see in Table 3.4, all the efficiencies are close to 92% and the output powers are close to 1 W. In practice, however, we must drive all the elements at the same frequency (the duty cycle can be different for each element). If we drive a transducer by using a non-optimum frequency, the switching loss of the Class-DE amplifier will be higher. The output waveforms of element B when it is driven under a non-optimum frequency 1024kHz is shown in Figure 3.4, the output waveforms show it is not in Class-DE mode (there are some distortions in the current waveform). So, to eliminate the switching loss and drive all the elements under a same frequency, we derived the following two strategies.

Figure 3.3: Output voltage and current waveforms of all the six elements that are driven by Class-DE amplifier

| Transducers  | DC supply power(mW) | Output power (mW) | Efficiency(%) |

|--------------|---------------------|-------------------|---------------|

| A            | 1242                | 1144              | 92.1          |

| В            | 1161                | 1071              | 92.2          |

| $\mathbf{C}$ | 1238                | 1142              | 92.3          |

| D            | 1071                | 984.4             | 91.9          |

| E            | 1300                | 1200              | 92.3          |

| ${ m F}$     | 1145                | 1053              | 92            |

Table 3.4: Simulation results of all the elements in the transducer array

Figure 3.4: Output voltage and current waveforms of element B that is driven under  $1024 \mathrm{kHz}$  which is a non-optimum frequency for element B

# 3.2.1 Using an External Parallel Capacitor

As we can see in the Figure 2.25, there are two intersection points of the plots of  $f_r$  and  $f_x$  which are the Class-DE switching points  $f_1$  and  $f_2$ . If the external capacitance  $C_{ext}$  increased, the  $f_1$  will increase and  $f_2$  will decrease until they meet each other [5]. As mentioned before, the  $f_2$  always is the optimum frequency, so we can increase a transducer's optimum operation frequency by adding an external capacitor that is in parallel with the load. The modified circuit is shown in Figure 3.5. So we can use the highest optimum operation frequency among these six elements, and add external capacitors to the other five elements to match this frequency. In these six elements, the highest optimum operation frequency is 1024 kHz which corresponds to Transducer D.

Figure 3.5: Half-bridge Class-DE amplifier with the parallel external capacitor

Based on Equations (3.1) and (3.2), let the  $f_r$  and  $f_x$  be equal to 1024 kHz and replace  $C_P$  by  $C_P + C_{ext}$ . Then solve them for  $C_{ext}$ , we can get following equations:

$$C_{ext,r} = \frac{1 - \cos(4\pi D)}{4\pi^2 f R_S} - C_P \tag{3.1}$$

$$C_{ext,x} = \frac{2\pi(1-2D) - \sin(2\pi D)}{2\pi L_S[(2\pi f)^2 - 1/(C_S L_S)]} - C_P$$

(3.2)

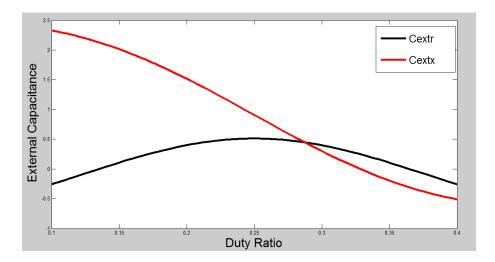

Figure 3.6:  $C_{ext,r}$  and  $C_{ext,x}$ 's plots of element E in Kivinen's transducer array

Where  $C_{ext,r}$  is the external parallel capacitance which is obtained from solving the equation for the real part of the transducer's impedance and  $C_{ext,x}$  is the external parallel capacitance that is obtained from solving the equation for the imaginary part of transducer's impedance. Then if we let the  $C_{ext,r} = C_{ext,x}$  and solve this equation, we can get the value of this external parallel capacitance with its corresponding duty ratio.

Let's use element E as an instance. In Equations (3.1) and (3.2), set f = 1024kHz and plot  $C_{ext,r}$  and  $C_{ext,x}$  versus the duty ratio D respectively. We obtain Figure 3.6 where the black line is the plot of the  $C_{ext,r}$  and the red line is the plot of the  $C_{ext,x}$ . There is an intersection of these two plots, the intersection point is the value of the external capacitance with its corresponding duty ratio. In this instance, the element E's external capacitance and its corresponding duty ratio is 449pF and 0.287.

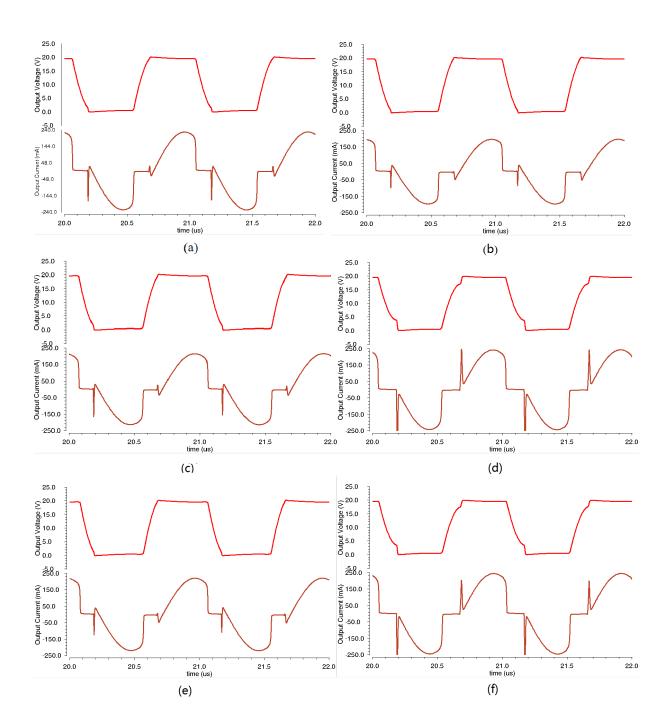

Based on above method, we can get all the external capacitance values of these six elements and their corresponding duty ratios. These values are shown in Table 3.5. The output voltage and current waveforms of all the 6 elements are shown in Figure 3.7. In this Figure, the periods of all the transducer elements are same, but their duty ratios are different. Their efficiency results are shown in Table 3.6. If we compare the efficiency results from Table 3.6 to the efficiency results of all the elements are driven under same frequency without the  $C_{ext}$ , which are shown in Table 3.7, the efficiencies have been increased.

However, the output power of this method is in some cases much lower than 1 W. Because the duty ratios are smaller than the optimum duty ratios, the turn on time of each transistor is shorter and less power is transferred to the load.

| Element      | D     | $C_{ext}$ |

|--------------|-------|-----------|

| A            | 0.291 | 323pF     |

| В            | 0.279 | 356pF     |

| $\mathbf{C}$ | 0.293 | 380pF     |

| D            | 0.328 | 0         |

| E            | 0.287 | 449pF     |

| $\mathbf{F}$ | 0.323 | 69pF      |

Table 3.5: External capacitance values of all the elements in Kivinen's transducer array

| Transducers  | DC supply power(mW) | Output power (mW) | Efficiency(%) |

|--------------|---------------------|-------------------|---------------|

| A            | 797                 | 726.8             | 91.1          |

| В            | 641.8               | 579.5             | 90.3          |