# ERROR CONTROL CODING FOR SEMICONDUCTOR MEMORIES

# A THESIS SUBMITTED TO LAKEHEAD UNIVERSITY IN PARTIAL FULFILMENT OF REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

BY HAO BAOMING ©

1993

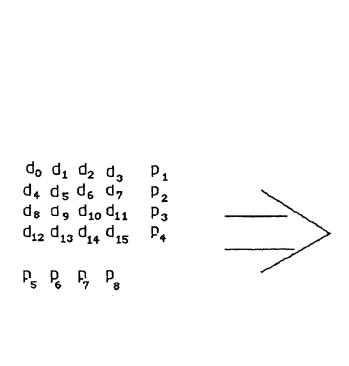

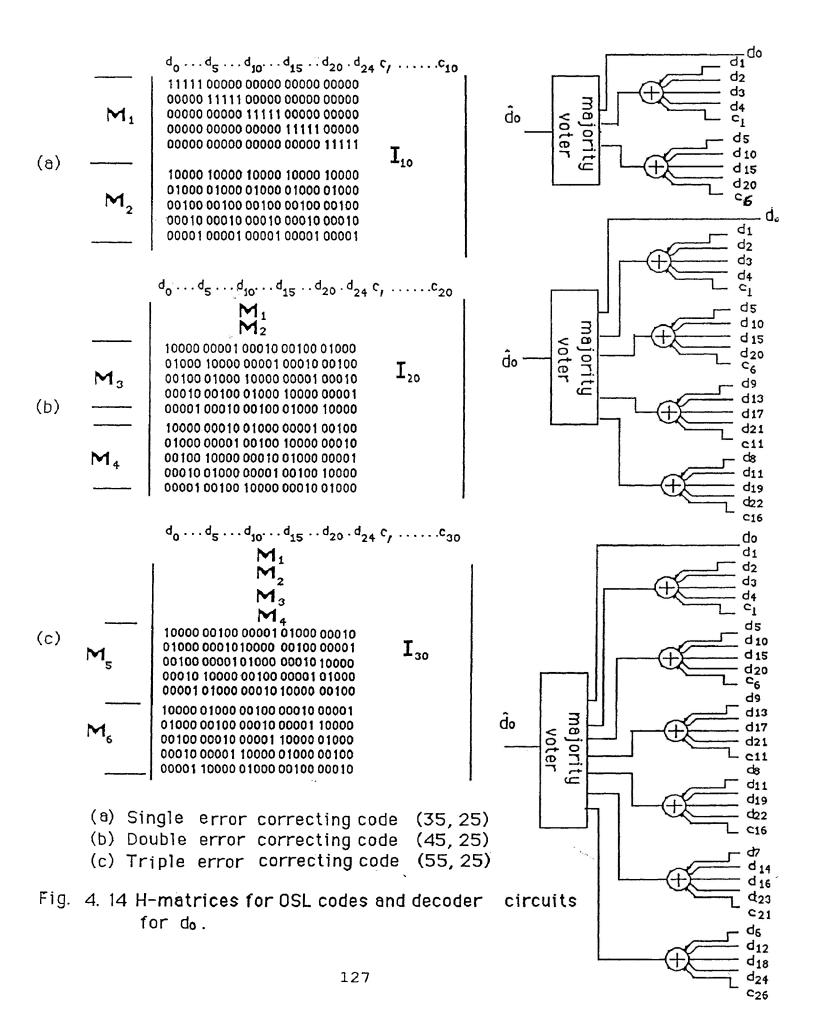

ProQuest Number: 10611858

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10611858

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our file Notre référence

The author has granted irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan. distribute sell copies or his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et exclusive non permettant à **Bibliothèque** la nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-86154-1

#### ERROR CONTROL CODING FOR SEMICONDUCTOR MEMORIES

#### Abstract

All modern computers have memories built from VLSI RAM chips. Individually, these devices are highly reliable and any single chip may perform for decades before failing. However, when many of the chips are combined in a single memory, the time that at least one of them fails could decrease to mere few hours. The presence of the failed chips causes errors when binary data are stored in and read out from the memory. As a consequence the reliability of the computer memories degrade. These errors are classified into hard errors and soft errors. These can also be termed as permanent and temporary errors respectively.

In some situations errors may show up as random errors, in which both 1-to-0 errors and 0-to-1 errors occur randomly in a memory word. In other situations the most likely errors are unidirectional errors in which 1-to-0 errors or 0-to-1 errors may occur but not both of them in one particular memory word.

To achieve a high speed and highly reliable computer, we need large capacity memory. Unfortunately, with high density of semiconductor cells in memory, the error rate increases dramatically. Especially, the VLSI RAMs suffer from soft errors caused by alpha-particle radiation. Thus the reliability of computer could become unacceptable without error reducing schemes. In practice several schemes to reduce the effects of the memory errors were commonly used. But most of them are valid only for hard

errors. As an efficient and economical method, error control coding can be used to overcome both hard and soft errors. Therefore it is becoming a widely used scheme in computer industry today.

In this thesis, we discuss error control coding for semiconductor memories. The thesis consists of six chapters. Chapter one is an introduction to error detecting and correcting coding for computer memories. Firstly, semiconductor memories and their problems are discussed. Then some schemes for error reduction in computer memories are given and the advantages of using error control coding over other schemes are presented.

In chapter two, after a brief review of memory organizations, memory cells and their physical constructions and principle of storing data are described. Then we analyze mechanisms of various errors occurring in semiconductor memories so that for different errors different coding schemes could be selected.

Chapter three is devoted to the fundamental coding theory. In this chapter background on encoding and decoding algorithms are presented.

In chapter four, random error control codes are discussed. Among them error detecting codes, single error correcting/double error detecting codes and multiple error correcting codes are analyzed. By using examples, the decoding implementations for parity codes, Hamming codes, modified Hamming codes and majority logic codes are demonstrated. Also in this chapter it was shown that by combining error control coding and other schemes, the

reliability of the memory can be improved by many orders.

For unidirectional errors, we introduced unordered codes in chapter five. Two types of the unordered codes are discussed. are systematic and nonsystematic unordered codes. Both of them are very powerful for unidirectional error detection. As an example of optimal nonsystematic unordered code, an efficient balanced code are analyzed. Then as an example of systematic unordered codes Berger codes are analyzed. Considering the fact that in practice random errors still may occur in unidirectional error memories, recently developed t-random correcting/all some error unidirectional error detecting codes are introduced. Illustrative examples are also included to facilitate the explanation.

Chapter six is the conclusions of the thesis.

The whole thesis is oriented to the applications of error control coding for semiconductor memories. Most of the codes discussed in the thesis are widely used in practice. Through the thesis we attempt to provide a review of coding in computer memories and emphasize the advantage of coding. It is obvious that with the requirement of higher speed and higher capacity semiconductor memories, error control coding will play even more important role in the future.

#### **ACKNOWLEDGEMENT**

I would like to take this opportunity to express my sincere thanks to my supervisor Dr. M. H. Kkan for his encouragement and support throughout the course of this program.

Thanks to Dr. Hasegawa for his invaluable advice.

Also I want to thank my family for their moral and patient support and understanding during the years of my study.

# ERROR CONTROL CODING FOR SEMICONDUCTOR MEMORIES

| Chap | ter One Introduction                   |    |

|------|----------------------------------------|----|

| 1.1  | Computer and Its Memory                | 1  |

| 1.2  | Coding for Computer Memories           | 7  |

| 1.3  | Summary                                | 12 |

| Refe | rences                                 | 13 |

|      |                                        |    |

| Chap | ter Two Semiconductor Memories         |    |

| 2.1  | Memory Cells                           | 17 |

| 2.2  | Memory Organizations                   | 31 |

| 2.3  | Errors in Semiconductor Memories       | 41 |

| 2.4  | Summary                                | 48 |

| Refe | rences                                 | 49 |

|      |                                        |    |

| Chap | ter Three Linear codes                 |    |

| 3.1  | Basic Concepts of Linear Codes         | 51 |

| 3.2  | Hamming Codes                          | 63 |

| 3.3  | Cyclic Codes and BCH Codes             | 67 |

| 3.4  | Summary                                | 76 |

| Refe | rences                                 | 79 |

|      |                                        |    |

| Chap | ter Four Codes Used in Computer Memory |    |

| 4.1  | Criteria for Code Selection            | 80 |

| 4.2                                           | Error Detection Codes                                                              | 83                |  |

|-----------------------------------------------|------------------------------------------------------------------------------------|-------------------|--|

| 4.3                                           | SEC-DED Codes                                                                      | 96                |  |

| 4.4                                           | Multiple Error Correction Codes                                                    | 118               |  |

| 4.5                                           | Erasures                                                                           | 133               |  |

| 4.6                                           | Summary                                                                            | 134               |  |

| Refe                                          | References                                                                         |                   |  |

|                                               |                                                                                    |                   |  |

|                                               |                                                                                    |                   |  |

|                                               |                                                                                    |                   |  |

| Chap                                          | ter Five Unidirectional Error Correction Code                                      | s                 |  |

| _                                             | ter Five Unidirectional Error Correction Code Unidirectional Error Detecting Codes | 142               |  |

| 5.1                                           |                                                                                    |                   |  |

| 5.1                                           | Unidirectional Error Detecting Codes                                               | 142               |  |

| 5.1                                           | Unidirectional Error Detecting Codes tEC-AUED Codes                                | 142               |  |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Unidirectional Error Detecting Codes tEC-AUED Codes                                | 142<br>150        |  |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Unidirectional Error Detecting Codes tEC-AUED Codes Summary                        | 142<br>150<br>158 |  |

#### CHAPTER ONE INTRODUCTIONS

Development in computer and its application has progressed rapidly during the last decades. Computer of today are much better in their performance and cheaper in cost. These have been achieved through dramatic improvement in hardware manufacturing as well as development of sophisticated software.

Reliability of the computers has also become a major issue as its applications become widespread. These criteria among other things require efficient and error free digital transmission and storage systems in computers. Computer memories, as one of the main subsystems of computer are playing a significant role towards computer's reliability and performance. As the memory system becomes larger, failures, including hardware and software failures, influence the behaviours of computer more seriously than ever.

#### 1.1 Computer and Its Memory

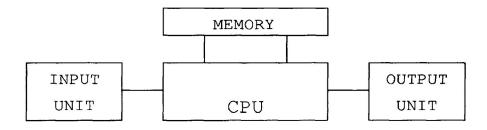

A block diagram of a digital computer is shown in Fig. 1.1. In this diagram there are four basic units, the input unit, central processing unit (CPU), main memory and output unit.

The input unit enables operator to feed in the information data and instructions to the computer. The output unit allows the results of computing to be sent outside. Both input and output unit are equipments that interface with outside. CPU, which consists of control unit and arithmetic unit, is the heart of

Fig.1.1 A bock diagram of a digital compute

computer. CPU controls flows of data and instructions between different parts of computer and processes these data such that computer can accomplish various functions. Because the rate of data transfer of the input unit is generally slow compared to the processing speed of CPU. It is necessary to hold the data and instructions in a place for immediate use which allows fast access to the stored data. This storage place is called main memory.

During operations, CPU directs the input information data to memory and reads them out as needed and applies arithmetic operations such as addition, subtraction, multiplication and division to the information data, and then, after being processed, the immediate results or final results are returned to the memory by CPU for preparation for output.

It can be seen that large amount of data communications between subsystems takes place in computer. Among these communications, the data traffic between CPU and main memory is of the highest rate. For example, for a high speed computer it may be of the order of 100 million bits every second<sup>[1,1]</sup>. A large computer memory stores more data and allows data communication between memory and CPU to be faster. Therefore a large main memory is essential for high speed computer systems.

#### High density memories and their problems

As a result of the greater need for storage capacity and speed, computer memories are becoming high density and high speed. This increased memory density has generally been achieved through

a reduction of storage cell size. Nowadays the memory chips containing lM-bit are quite common. Table 1.1 [1.2] gives a view of the progress of densities of semiconductor DRAMs (Dynamic RAM, which is one type of the semiconductor memories. In chapter two various other semiconductor memories will be discussed). It shows that DRAM size is being quadrupled in about every two to four years in the past 20 years.

However, extremely small cell size and complexity of VLSI circuitry are more vulnerable to manufacturing failures and various interferences, especially alpha-particle radiation etc. This has largely increased the probability of failures in semiconductor memories. This in turn has increased error rates in computer systems and obstructed the progress of even higher density and higher speed memories.

The errors in semiconductor memories can be basically divided into two types: hard errors and soft errors. A hard error occurs when a memory location of hardware becomes permanently defective. It is an irreversible error caused by connection failures like internally shorted or open leads. Soft errors are temporary and random in time and locations. They may occur during one particular memory cycle time but disappear in the next cycle. The soft errors result from system noise, power surges, atmospheric interference and alpha-particle radiation<sup>[1.3]</sup>.

Table 1.1 Storage geometry parameters in RAM

| memory size | storage area | cell area         |      |

|-------------|--------------|-------------------|------|

| (bits)      | (cm²)        | (μ <sup>2</sup> ) | year |

| 4K          | 0.07         | 1764              | 1973 |

| 16K         | 0.1          | 800               | 1976 |

| 64K         | 0.15         | 216               | 1978 |

| 256K        | 0.3          | 96                | 1982 |

| 1M          | 0.2          | 20                | 1984 |

| 4M          | 0.3          | 9                 | 1986 |

| 16M         | 0.3          | 1.5               | 1987 |

| 64M         | 0.6          | 0.7               |      |

#### Some schemes for increasing the reliability of memory system

It is important that the memory system enables to detect and correct errors as and when they occur. Otherwise the errors will lead to incorrect computation or even serious malfunction of the system operations.

There have been several approaches to reduce or overcome the consequences of errors in computer memories. Some of them are discussed as follows:

a) Memory Organizations Scheme [1.4, 1.5, 1.6]

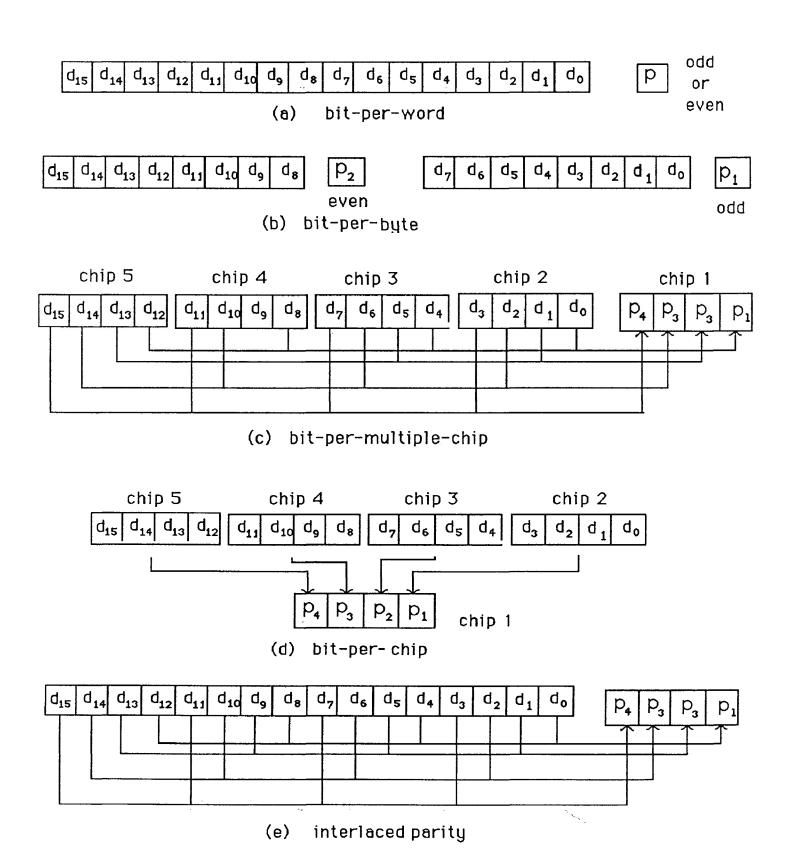

For some hard errors, proper memory organizations can be used to limit the number of errors within a memory word or to disperse errors into single error per word so that simple error correcting scheme is used effectively. For example, one-bit-per-chip organization is one of such designs. In this organization every bit of a word is stored in a different memory chip. A word of n bits then is stored in n chips in the memory. As a result, when a whole chip in the memory fails, it can affect, at most, only one bit of the word.

b) Hardware Redundancy Scheme [1.7]

In this scheme, some amount of spare hardware components or memory cells are provided in memory chips during its fabrication. Whenever a memory cell is found permanently defective, the spare cell is automatically switched in to replace the defective ones. This scheme greatly increases the system reliability but causes a low efficiency in storage area usage.

c) Hardware Maintenance Strategy[1.8]

In a system environment, another option for memory reliability is the system maintenance strategy. This strategy allows memory to accumulate certain correctable failures in memory until they reach a threshold which is intolerable to the computer memory. Then the faulty memory chips are physically replaced. Such a substitution strategy is scheduled periodically during service time of computer.

d) Error Control Coding (ECC) Scheme [1.1, 1.9, 1.10, 1.11]

All methods mentioned above are valid only for hard errors. By adding some redundancy bits to information data, the scheme of ECC enables to combat both hard and soft errors occurring in memory words. By using the encoding and decoding logic, the ECC scheme enable to detect and even to correct errors as they occurred.

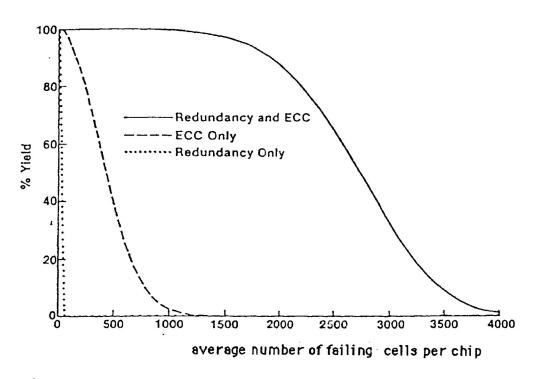

Because of its high efficiency, ECC along with some other techniques mentioned above produces a versatile and robust scheme to improve the reliability of semiconductor memories. Therefore they are becoming quite common features in modern high performance computer systems.

#### 1.2 Coding for computer memories

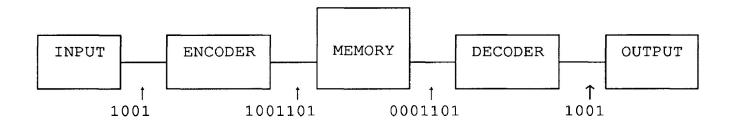

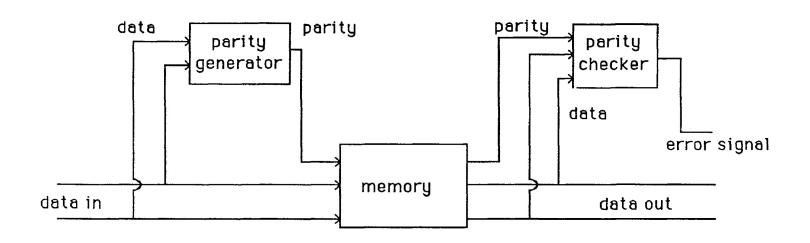

As an example, a simple illustration is shown in Figure 1.2 to explain the concept of memory with ECC technique.

Let us assume that the possible information data from input

Fig.1.2 Simple illustration of a memory system with EDC scheme  $\,$

(to be stored in the memory) are 1001. Instead of being stored in memory directly, the data is firstly sent to the encoder where, according to certain coding rules, some redundancy digits 101 are formed and added to the information data 1001. This process is called encoding and the new data which contain information digits and redundancy digits are called encoded word or codeword while the redundancy digits 101 are usually called parity check bits or check bits. Then the encoded data are sent to memory and stored there as 1001101.

Due to some faults in the memory, the codeword may be corrupted to an erroneous word. For example, suppose at the first position of the codeword, 1 is changed to 0 such that the actual codeword stored in the memory becomes 0001101 which differs from the original codeword.

However, when the codeword is read out from the memory, the decoder will make it sure that the information portion of the codeword is 0001. Following the same rule as in the encoder, the decoder will regenerate new check bits, say 100, and compare them with the old check bits 101. If there is no differences between them, the codeword from the memory is accepted as correct. Otherwise error(s) is detected. By comparing the differences, the decoder will also be able to locate the position of the error and then correct it. As a result, after decoder, the original information data 1001 is recovered and sent to its destination.

By proper design, ECC coding enables to detect and correct either single error or multiple errors in a codeword [1.11].

Generally, most coding schemes do not require very complicated computations and implementations. Therefore it has found wide use in computer memories to improve the performance and reliability.

In early computers, for example, the IBM/650, UNIVAC and the Whirlwind computers, the simplest ECC schemes, single error detecting codes were used to enhance memory system reliability[1.11]. These codes added a single parity bit to the information data bits for error detection only. Today many different ECC codes are implemented in computer industry worldwide. The most common codes are Hamming codes [1.10], modified Hamming codes [1.12] and unidirectional error correcting codes[1.13, 1.14, 1.15]. Some VLSI chips which support modified Hamming codes are commercially available (e.q. SN54/74LS630) [1.16]. These chips are used externally to the memory while designing computer systems. In other ECC systems error correcting codes are implemented on memory chips [1.17].

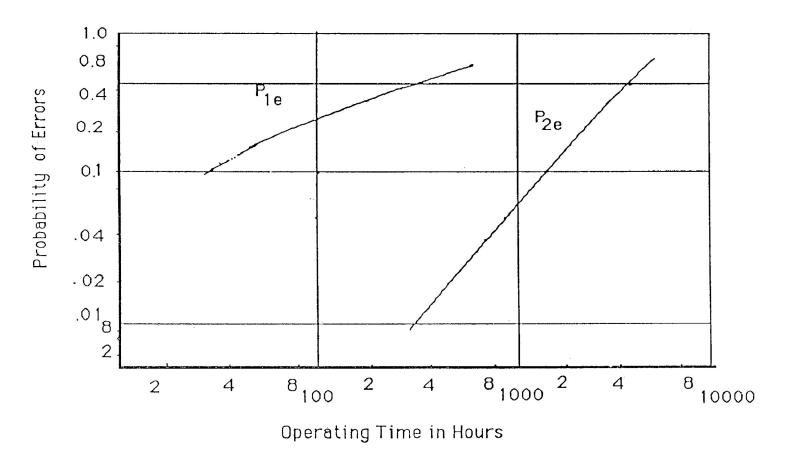

Use of ECC enables modern semiconductor memory to maintain the advantage of low cost, low power, high density and high speed while still achieving acceptable level of memory reliability. Figure 1.3  $^{[1.18]}$  provides a comparison between memories with ECC and without ECC with respect to the operating hours under certain error probability. In the figure,  $P_{1e}$  represents the error probability for the memory without ECC and  $P_{2e}$  for the memory with ECC. As can be seen, a 32-bit, 64k word memory without ECC  $P_{1e}$  will reach 50% in 350 hours of operation. While for the memory with ECC, which can correct any single error within the 32-bit word, at the same error probability the operating time is extended up to 4500 hours.

Pie: The probability of errors of the memory without ECC

$P_{2e}$ : The probability of errors of the memory with ECC

Note: Only memory failures are considered here.

Fig. 1.3 Probability of errors for 32-bit, 64K word memory<sup>[18]</sup>

#### 1.3 Summary

Main memory systems are of significance for computer's performance and reliability. Due to its fast development of VLSI and computer applications, semiconductor memories are becoming larger (in capacity) and faster. Meanwhile the extremely high density memory products suffer from various errors including hard errors and soft errors. To minimize the consequence of these errors, several schemes are practically implemented in main memory systems.

Among those schemes mentioned above, ECC is one of the most effective techniques. ECC is the art of adding redundancy effectively so that most messages, if corrupted, can be detected or recovered correctly. Combined with some other schemes, ECC coding has shown dramatic improvements in computer memory reliability.

Throughout the chapters of this thesis, based on considerations mentioned above, several ECC codes for computer memories are discussed. The main attention will be concentrated on semiconductor main memories. In the following, when memories are mentioned, they refer to semiconductor main memories.

#### References

- 1.1 T. R. N. Rao, E. Fujiwara, "Error-control Coding for Computer

Systems" Prentice-Hall Inc., 1989

- 1.2 Pinaki Mazumder, Janak K. Patel, "Parallel Testing for Pattern-Sensitive Faults in Semiconductor Random-Access

Memories" IEEE Transactions on Computers, No. 3, March

1989 pp 394

- 1.3 Suneel Rajpal, John. Mick, "Fast Error-correcting ICs Aid Large Memory System" Electronic Design, Feb. 1987, pp 123-126

- 1.4 Richard E. Matick "Computer Storage & Technology" A Wiley & Sons 1977

- 1.5 S. Middelhock, P. Gorge, P. Deker, "Physics of Computer

Memory Devices" Academic Press, 1976

- 1.6 Chitoor V. Srinivsan, "Code for Error Correction in Highspeed Memory Systems--Part I: Correction of Cell Defects in

Integrated Memories" IEEE Transaction on Computers, vol. c20, No. 8, Aug. 1971, pp 882-888

- 1.7 Ramachanda P. Kunda, Bharat Deep Rathi, "Improving Memory Subsystem Availability Using BIST" IEEE International

- Conference on Computer Aided Design, ICCAD-87, Digest of Technical Papers, 1987, pp 340-343

- 1.8 D. C. Bossen, M. Y. Hsiao, "A System Solution to the Memory Soft Error Problem" IBM Journal of Research and Development, vol. 24, No. 3, May 1980, pp 390-397

- 1.9 Chen, C.L, Hsiao, M.Y "Error-correcting Code for Semiconductor Memories Application: a State-of-the-art Review"

IBM J. Res. Develop., vol. 28, No. 2, Mar. 1984, pp 124-134

- 1.10 W. Wesley Peterson, E. J. Welson, JR. <u>Error Correcting Codes</u>

MIT press 1986

- 1.11 Bary W. Johnson, "Design and Analysis of Fault Tolerant

Digital System" Addison Wesley, 1989

- 1.12 M. Y. Hsiao, "A Class of Optimal Minimum Odd-weight-column SEC-DED Codes" IBM J. Res. and Develop. 14, (July 1970) pp 395-401

- 1.13 Serban D. Constantin, T. R. N. Rao, "On the Theory of Asymmetric Error Correcting Codes" Information and Control 40, 20-36 (1979) pp 20-35

- 1.14 Bella Bose, Thammavaram R. N. Rao, "Theory of Unidirectional Error correcting/detecting Codes" IEEE Transactions on

Computers, vol. c-31, No. 6, June 1982, pp 521-530

- 1.15 Dhiraj K. Pradhan, "A New Class of Error-correcting /detecting Codes for Fault-tolerant Computer Applications"

IEEE Transactions on Computers, vol. c-29, No. 6, June 1980, pp 471-481

- 1.16 Dale Hunt, Thomas J. Tyson, "Error Detection and Correction

Using SN54/74LS630 or SN54/74LS631" Microprocessors and

Microsystems, vol. 13, No. 7, Sept. 1989, pp 473-480

- 1.17 Howard L. Kalter, "A 50-ns 16-Mb DRAM with a 10-ns Data Rate and On-Chip ECC" IEEE Journal of Solid-State Circuits, No. 5, Oct. 1990, pp 1118-1127

- 1.18 Len Levine, Ware Meyers, "Semiconductor Memory Reliability with Error Detecting and Correcting Codes", Computers,

October 1976, pp 43-49

#### CHAPTER TWO SEMICONDUCTOR MEMORIES

In computer systems there are two types of memories. Main memory and secondary storage. By main memory it refers to the memory that is built-in along with the computer CPU. Main memory offers very fast access speed so that computer can take the advantage of the high processing speed of CPU.

In modern computers, semiconductor devices are widely used as main memories. Implementation of VLSI (Very Large Scale Integration ) technology has allowed many fold increase in the memory capacity within a compact size.

Main memory can be classified as Read-Only-Memory (ROM) and Random-Access-Memory (RAM). RAM memories allow the user (or CPU) to read data or instructions into it, read them out and also allow to change the data stored in the memory on demand. While ROM memory only allows CPU to read and use the information it has stored but not change them.

When enormous quantities of data are to be stored, a secondary storage is required. Secondary storage is external storage equipment, which provide very large storage capacity but needs more access time. Secondary storages store data relatively longer or even permanently. When needed, the data stored in the secondary storage have to be transferred to the main memory so that CPU can access them directly. Commonly used secondary storage devices are usually made of tapes, floppy disks and magnetic drums.

For both memories, the trends are towards extremely high

capacity and speed.

The basic unit of the memory which can store and retrieve a binary bit, 0' or 1', is called storage cell. Modern semiconductor techniques make it possible that hundred of thousands storage cells are integrated in a tiny silicon chip. Many such chips are organized together to form a whole computer memory. One of the main advantage of semiconductor memory is its high density and low cost.

It is beyond the scope of this thesis to describe either physics or fabrications of semiconductor memory and its cells. However, in order to have a better understanding of error control coding for semiconductor memories, in this chapter, we provide a brief review of semiconductor memories in principle. At First, in section 2.1, semiconductor storage cells are discussed. discussion includes ROM memory cells, RAM memory cells and DRAM Then in section 2.2, three types of organizations for All practical memories are computer memories are presented. organized in these forms with some small variations. In section 2.3, the mechanisms of semiconductor memory errors are analyzed. Different types of errors are also classified in this section so that for different type of errors the corresponding error control codes can be selected and employed.

## 2.1 Memory Cells

## a) Read only memory cells

In a computer, many operations are carried out more than once

without changing the content. This fact makes fixed memory or so called read only memory (ROM) very useful. ROM are constantly used in computer for character generation, bootstrap programs and look-up tables  ${\rm etc}^{\{2,1\}}$ .

A ROM consists of a matrix of addressable cells. Several types of ROM cells are implemented in practice.

### i) ROM diode cell[2.2]

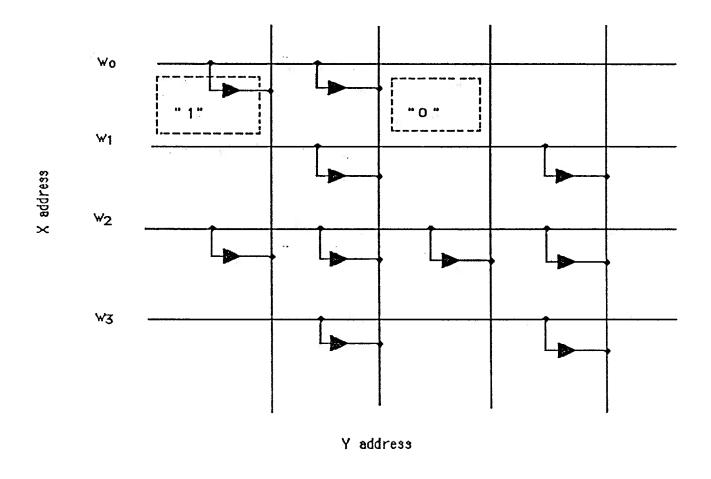

Fig.2.1 shows a diode memory array. The information bits 1' and 0' stored in cells are represented by the presence or absence of diode between x and y lines (the x and y lines are also called word line and bit line). The reading operation is very simple. When a 1' information stored in a cell (in which the diode is connected to x and y lines) is to be read out, a constant current is applied to the x line connected to the cell while the associated y line holds a low voltage so that the diode conducts and the corresponding output provides a low current. Otherwise if a 0' is stored in the cell, where the diode is absent, the constant current from x line will flow through the output directly. Therefore the information 1' and 0' is distinguished by a low current and a constant current in the output. In this example suppose the first x line W<sub>0</sub> and all four y lines are selected, then a word 1100 is read out.

It can be seen that to address a particular cell, the associated x and y selection lines have to be coincident.

Fig. 2.1 ROM Diode Cells

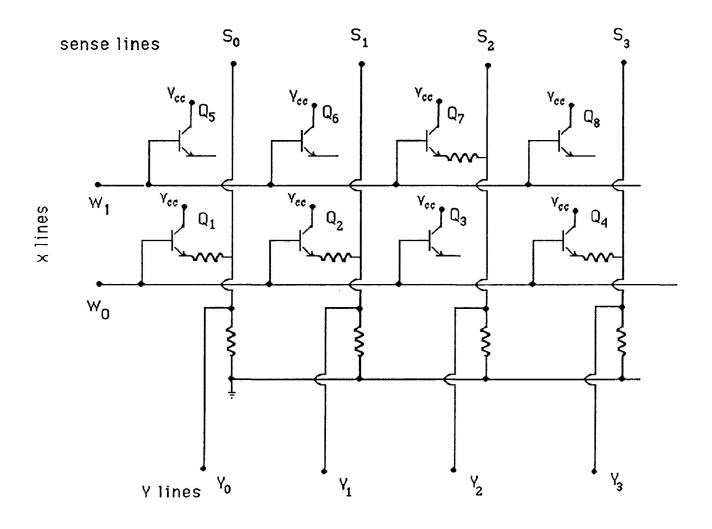

Fig. 2.2 Bipolar ROM Memory Cells

## ii) ROM bipolar transistor cell[2.3]

Bipolar transistor can be used in ROM in very nearly the same way as in diode memory. A typical circuit of a bipolar cell is shown in Fig.2.2. Two types of cells for 1' and 0' can be distinguished . In the 1' cell, the emitter of the transistor is connected to y line while in 0' cell the emitter of the transistor is disconnected from y line. Suppose the x-line  $W_1$  in the figure is driven high. This would turn on all transistors connected to it. Current would then flow through the transistors, through their emitter resistors and through the resistors at the bottom of the A voltage drops across the sense line resistor sense lines. indicates a binary information 1', such as  $Q_7$  in the figure. While in the 0' cells (i.e.,  $Q_5$ ,  $Q_6$ , and  $Q_8$ ), since there is no such a emitter current at all, there would be no voltage changed at the corresponding sense line, hence the 0' is sensed. A word 0010 is then read out.

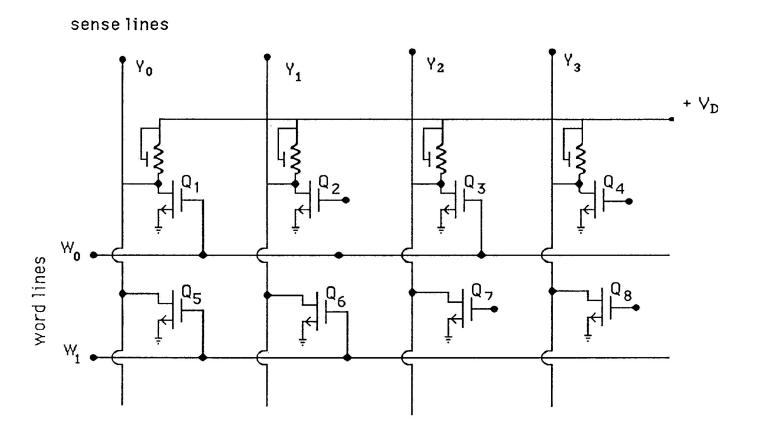

# iii) MOS ROM cell[2.1]

MOS (Metal-Oxide-Semiconductor) technology is ideal for ROM due to its high density. A typical MOS ROM cell is shown in Fig. 2.3. The 1' and 0' cells are distinguished by connecting or disconnecting the gate of FET to the word line. For example when a positive pulse is applied on line  $W_0$ , current will flow up through  $Q_1$  (and  $Q_3$ ) and FET load to  $+V_{DD}$  line. The voltage across the load drops the  $y_0$  and  $y_2$ . As a result, a 0' is read out. Since  $Q_2$  (and  $Q_4$ ) is inactive, there is no voltage drop on  $y_1$  (and  $y_3$ ), it will stay high , indicating a 1' being read out. Thus a word

Fig. 2.3 Mos ROM Memory Cell

0101 is sensed.

#### b) Random access memory cells

Random Access Memory (RAM) allows not only to read out the content it stores but also to change (write) the content of the memory on demand.

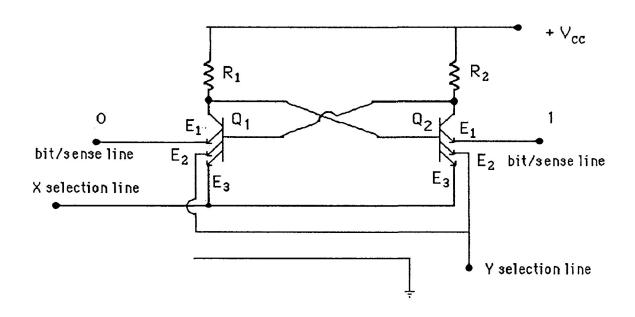

### i) Bipolar memory cell [2.1]

Fig.2.4 illustrates the circuitry of a TTL (Transistor-Transistor-logic) memory cell.  $Q_1$  and  $Q_2$  form a bistable flip-flop. The x and y lines are for selection or address of cells. The bit/sense line pair are for writing and reading, respectively. Write and read operations are described as follows.

Store a 0' To store a 0' in a cell, the corresponding x and y lines are driven high to address the cell. Then the write circuit place a low condition on  $E_1$  of  $Q_1$ . This turns  $Q_1$  on and  $Q_2$  off regardless the previous state of the flip-flop. When the write pulse is gone, the flip-flop remains the state  $(Q_1$  on and  $Q_2$  off) unchanged. With the x and y lines back to normal (ground), the emitters  $E_2$  and  $E_3$  on  $Q_1$  provide a path for emitter current. The current flowing in  $Q_1$  is now from  $E_2$  and  $E_3$  to ground rather than from  $E_1$ . Once the digit 0' is stored, it is locked in the cell. The memory state can only be changed by grounding the write sense line on the off transistor. This change can only be made when the select lines are high.

Store a 1' If a 1' is to be stored, the x and y select lines

Fig. 2.4 Bipolar RAM Memory Cell

for the cell are driven high. The write circuit shorts  $E_1$  on  $Q_2$  to ground. The forward bias suddenly turns  $Q_2$  on and the flip-flop action turns  $Q_1$  off (regardless the previous state of the flip-flop). Then the state ( $Q_1$  off and  $Q_2$  on) is kept until a next write operation comes.

Sense To read the content of the memory we simply drive the x and y lines high. If  $Q_1$  is on and  $Q_2$  off which means a 0' is stored in the cell,  $Q_1$  will conduct through the resistor of sense amplifier. There will be no  $Q_2$  current flowing in the sense amplifier connected to  $E_1$  on  $Q_2$ , therefore there is no output from the 1' sense amplifier. If the content of the cell is 1', then only 1' sense amplifier has output and 0' sense amplifier keeps unchanged.

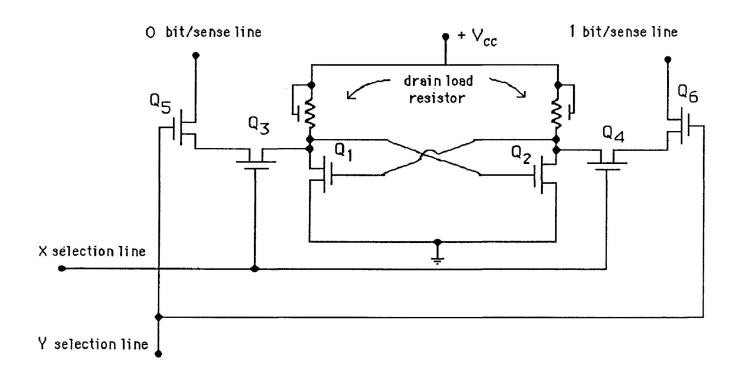

# ii) MOSFET memory cell [2.1]

A basic MOS RAM memory cell is shown in Fig. 2.5.  $Q_1$  and  $Q_2$  constitute the bistable flip-flop. The drain load resistor is found by series MOSFETs. Many variations to the basic circuit are possible, but the principle of the operations are similar. The operations of writing and reading are described as follows.

Write the memory To enter a digit into the memory cell, x and y address lines have to be applied  $+V_{dd}$ . If a 0' is to be stored, the 0' bit line is placed to ground while the 1 bit line is held high. As a result,  $Q_1$  will be turn on and  $Q_2$  off. If a 1' is to be stored, the 1' bit line goes to ground and 0' bit line holds high so that  $Q_1$  is off and  $Q_2$  on.

Read the memory To read the condition of the cell, the x and y

Fig. 2.5 MOS ROM Memory Cell

address lines are switched from ground to  $+V_{DD}$ . This high voltage will turn on  $Q_3$ ,  $Q_4$ ,  $Q_5$  and  $Q_6$ . These transistors act now as closed switches such that the bit lines are both at  $+V_{DD}$ . However only the line connected to the 'on' flip-flop will conduct. Suppose  $Q_1$  is on and  $Q_2$  off. In this case, current can flow from ground up through  $Q_1$ ,  $Q_3$ ,  $Q_5$  to 0' bit line. The current in this line is then sensed and amplified. The output is recognized as a 0' in the memory. Meanwhile for the 1' bit line, there is no current at all as  $Q_2$  is off.

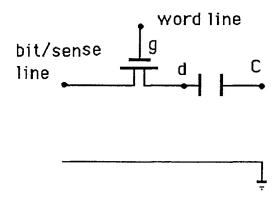

## c) Dynamic RAM memory cell[2.4]

The RAM memory cells discussed above are all static memory cells. That is, the state or condition of the cell would remain unchanged until another write operation applies on the cell. To hold two stable states for storing information '1 and 0', the static RAM cell needs at least 2 transistors or MOSFETs. In the following we introduce a kind of dynamic memory cells. It contains only one transistor hence a higher density fabrication can be achieved.

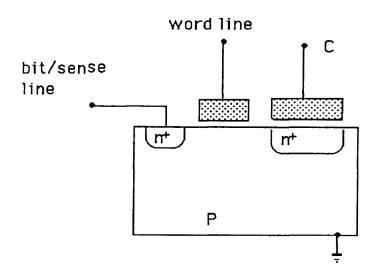

A simple scheme of the single transistor cell is shown in Fig. 2.6 (a). The capacitor  $C_s$  is the storage capacitance and the MOSFET transistor acts as a switch. The capacitor  $C_s$  can be made in the same technology with that of the transistor. The cell structure in integrated technology is shown in Fig. 2.6 (b). In both circuits bit line and sense line share a same line called

(a) Single Transistor DRAM Cell in Separated Devices

(b) Integrated Structure

Fig. 2. 6 Single-Transistor DRAM Cell

Fig. 2.7 Read and Write Operations

bit/sense line. The electrode C is always applied at a voltage  $+V_0$ . The information will be stored in the capacitor by presence and absence of negative charges in the capacitor. The read and write operations are described as follows.

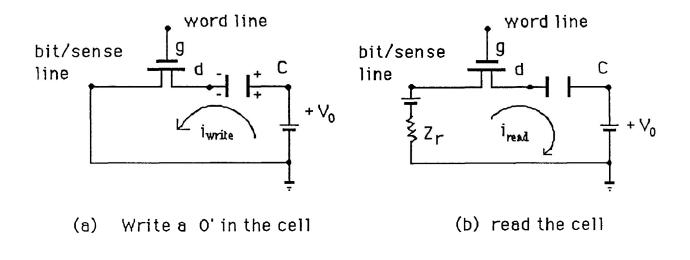

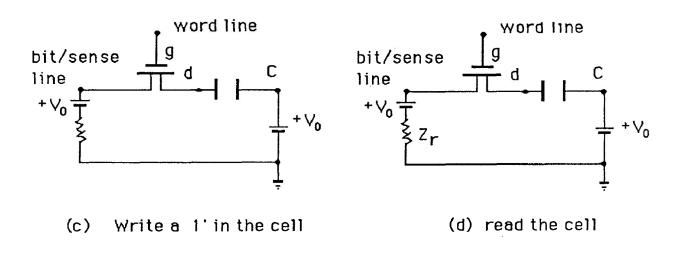

Write and read a 0' When a 0' is to be written the cell, the word line is pulsed high and the bit/sense line connected to ground as shown in Fig. 2.7 (a). The dc voltage  $V_0$  charges the capacitor  $C_s$  with current  $i_{\rm write}$ . As a result, the capacitor is charged with negative charges which represents a 0' being stored in the cell. When read the cell, the word line is pulsed high and the sense/bit line is connected to a voltage of  $V_0$  through the sense amplifier impedance  $Z_r$ . The equivalent circuit is shown in Fig. 2.7 (b). The current  $i_{\rm read}$  will create a small signal across  $Z_r$ , thus the 0' is sensed. We can see that the current  $i_{\rm read}$  will discharge the 0' information stored in  $C_s$  during the reading operation. Therefore the system has to be able to rewrite the information repeatedly or refresh the cell periodically.

2

Write and read a 1' When write a 1', the word line is pulsed high and bit/sense line is connected to  $+V_0$  as shown in Fig. 2.7 (c). Since there is no current flowing in the capacitor circuit, there would be no charges being stored in the capacitor. This indicates that a 1' has been stored in the cell. When read the cell, the word line is driven high and the sense/bit line is connected to  $V_0$  through the sense amplifier impedance  $Z_r$ . The equivalent circuit is shown in Fig. 2.7 (d).

Since there is no current flowing in the circuit, there would be no voltage across the  $\mathbf{Z}_{\rm r}.$  Thus the information 1' is sensed.

# 2.2 Memory Organizations [2.4]

There are three basic classes of memory organizations. They are the two, three, and two and half dimensional organizations (represented by 2D, 3D and 2-1/2D). The 2D and 3D types require a basic storage cell with two and three functional terminals, respectively. The 2-1/2D can use either types of cells. In practice, there would be some variations to these basic organization forms but the principle is the same. In some applications several schemes are combined to meet different needs. In the following we only discuss the three basic organizations which are useful for our purpose.

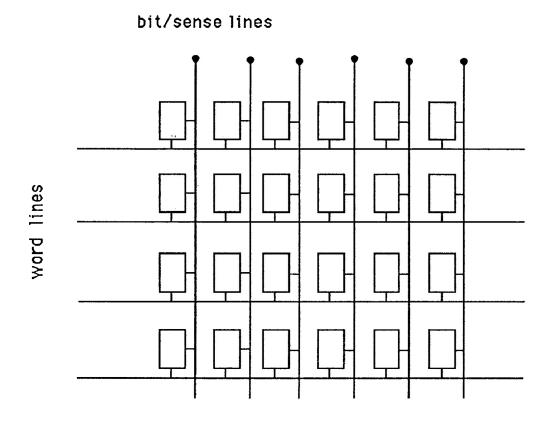

# 1 2D-memory organization

The simplest practical memory is organized as 2D memory. Fig. 2.8 shows a block diagram of the scheme. All the memory cells are arranged in the form of a matrix. The cells in the same row are connected to a so-called word line. The cells in the same column are connected to a bit line. Any cell can be accessed randomly by the coincidence of a word line and a bit line. In the read and write operations, when a word line is selected, all cells associated with the word line will be available to be accessed. Actually, all these bit lines are accessed simultaneously.

Fig. 2.8 2D Organized Memory

To write a word which consists of several bits in the memory, a word address is firstly required from the CPU. According to the address, a appropriate word line is energized. At the same time, the content of the word which comes from the data register arrives at bit lines. This causes the memory cell to be set to 1' state. If a bit line signal is absent, the cell then remains in the 0' state. To read a word from the memory, the desired word line is addressed and the content of each cell connected to the word line will appear on the corresponding bit line. Then through the sense amplifiers, all the bits of the word are sensed simultaneously.

## 2 3D-memory organization

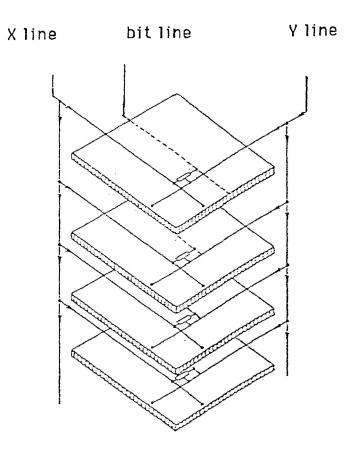

There are two basic types of 3D storage. The series and parallel connections for the selection line. In semiconductor memories parallel version is more favourable. We only consider parallel 3D storage. Fig.2.9 is a illustration of 3D parallel organization. The x and y selection lines are connected in parallel between planes, the bit lines are connected in series on a plane. Every plane is of the same structure and contains the same number of cells.

The basic operations require the use of an x line, a y line and bit line for writing, and an x line, a y line, and a sense line for reading. For example, in a flip-flop memory, a coincidence of the x and y lines, and 1' signal on the 1' bit lines cause a 1' to be written in a corresponding cells and a coincidence of x and y

Fig. 2.9 3D Organized Memory

lines, and 0' signal on the 0' bit lines will store 0's in the corresponding memory cell. For reading, energizing the x and y lines makes all the intersection cells ready to be sensed on the sense lines. In this scheme it can be seen that when a pair of x and y line are selected all the cells in the vertical direction are activated. All these cells each from different plane form a word. Thus the number of cells in each plane is equal to the number of the word that the memory contains. The number of the planes is equal to the number of the bits per word.

# 3 2-1/2D memory organization

Almost all the main memories today are of 2-1/2D organization. Both two and three terminal storage cells can be used in 2-1/2D memory, therefore there are two fundamental forms of 2-1/2D for each of the cells respectively.

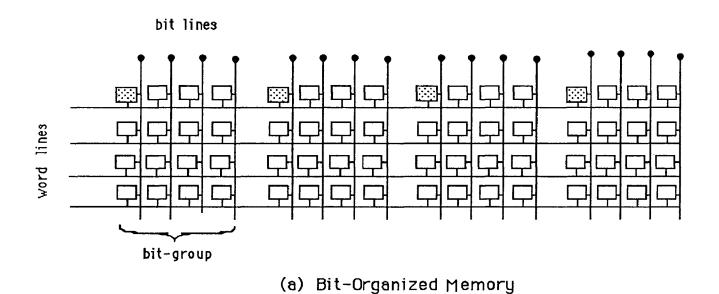

In all main memories the number of word is greatly exceeds the number of bits per word. This fact causes a difficulty that the word address circuitry would be very large and therefore need a long word addressing delay. To overcome the problem, we need to reduce the number of word lines without reducing the number of words which the memory contains. That is, one word line would energize more than one words. Fig. 2.10 (a) and (b) illustrate the principle of such organized memory matrices using two terminal storage cells.

Each row of the memory matrix is now divided into four bit\_groups (can be any number of bit-groups in a row in practice). When a word line is selected, four bit-groups are half activated.

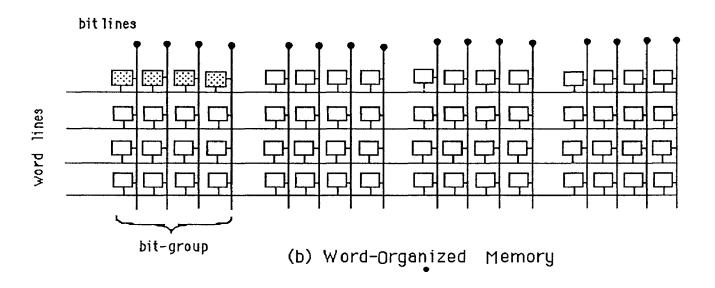

Fig. 2.10 2-1/2D Organization Using Two Terminal Storage Cells

In Fig. 2.10 (a), a word consists of four bits, each bit comes from different bit-group. This is a Bit-organized 2-1/2D memory organization. In Fig. 2.10 (b), a word consists of the bits that come from a single bit-group. Hence it is a word-organized 2-1/2D memory organization. Since two terminal cells are used in this organization, the bit line and sense line are the same line called bit/sense line.

To write a 1' into the memory, a word line and appropriate bit line have to be coincident. If there is no signal on the bit line, the cell remains in the 0' state. To read the memory, there is no coincidence required. When a word line is selected, the contents of all cells connected to the word line appear on the corresponding sense/bit lines (four words are available to be read in Fig. 2.10). But only the desired sense lines are switched to the sense amplifiers.

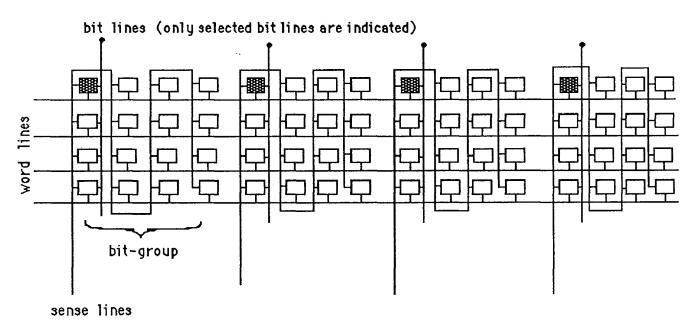

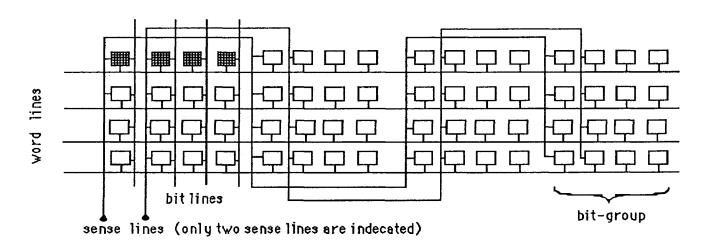

For three terminal cells, there are also two configurations for the 2-1/2D organization. They are bit-organized and word-organized organizations. The simplified illustrations are shown in Fig. 2.11 (a) and (b), respectively. Since three terminal cells are used, the bit lines and sense lines are separated. In the figures, the connection of sense line are shown (for simplicity, only two sense lines are illustrated, the other two sense lines can be connected in a similar way). The word lines and bit line remain identical to those for two terminal cells as shown in Fig. 2.10. The difference between Fig. 2.10 and Fig 2.11 is that in the latter, the reading operation also requires a coincidence of a word

(a) Bit-Organized Memory

(b) Word-Organized Memory

Fig. 2.11 2-1/2D Organization Using Three Terminal Storage Cells

line and appropriate bit lines. This is because, for example, in Fig 2.11 (a), on the first sense line there are as many as 16 cells available to be read, but only the shadowed one is desired. The coincidence can be used to specify the desired cell from many cells associated with the same sense line. LSI (Large Scale Integrated) semiconductor technology makes it possible to integrate many cells on a tiny chip so that the memory capacity can be increased dramatically. In our organizations shown in Fig. 2.10 and Fig. 2.11, all bit-groups in vertical direction can be fabricated on a single chip respectively. Thus the memory showed in Fig.2.11 is made up four chips with each chip of 16 cells. Modern VLSI can make 64k cells or more on a single chip. The high density chips not only significantly increase the capacity of the main memory but also greatly reduce the joints and connections between cells, therefore reduce the potential circuitry faulty. On the other hand, the maintenance of the memory on the level of chips becomes much easier than that of on the level of individual cells. When chips are used in the memory discussed above in Fig. 2.11 (a) and (b), they are usually called bit-per-chip and word-per-chip organization, respectively. There are also byte-per-chip organized memory in practice.

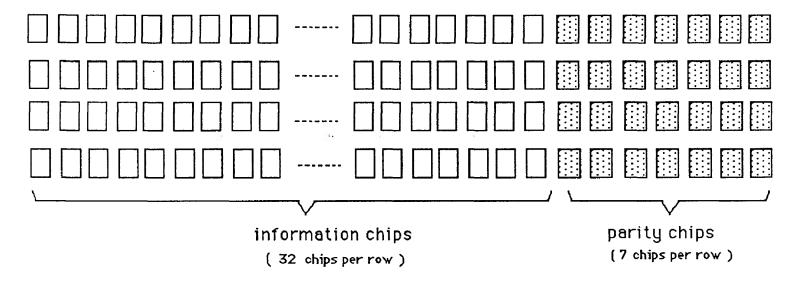

### An example of chip organized 2-1/2D memory organization

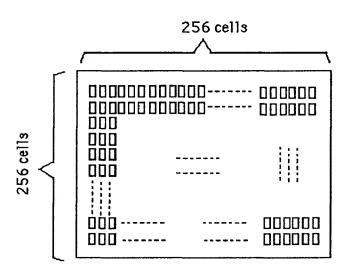

A typical chip organized memory board with 1M-byte sold for VAX computers is shown in Fig. 2.12 (a) [2.5, 2.6]. Each chip is organized internally as 256 X 256 square matrix of bits. This 64K chip has 65536 single-bit locations as shown in Fig. 2.12 (b). The

(a) 1M-byte memory organization

(b) Structure of chip

Fig. 2.12 1M-Byte Memory

memory board is organized as 4 x 39 matrix of chips. The first 32 chips in each row are used for storing information bits, and the remaining 7 chips in the row are for parity check bits (we will discuss the function of these parity check bits in the next chapters latter on). Every word consists of 39 bits, each bit is stored in a different chip in one row. Therefore this is a bit-per-chip organized memory.

According to the organization, we can simply calculate the parameters of the memory as follows:

Number of words in the memory  $(N_w) = 256 \times 256 \times 4 = 256K$  words

Number of bits in the memory  $(N_b) = N_w \times 39 = 10 M$  bits Number of bytes in the memory  $(N_B) = N_b / 8 = 1 M$  bytes Number of bits per word (word size  $W_s$ ) = 39 bits

It can be seen that in practice the number of words and word lines are very large. The selection of a word or a cell is therefore somehow complicated. In memory system the appropriate selection is done by a so-called address decoder. The concept of the address decoder was eliminated in the above discussions.

#### 2.3 Errors in Semiconductor Memories

Due to the defective cells, failed connections between selection lines, bit/sense lines and various interferences, there exist faults in semiconductor memories. Particularly when memory cells trend to be extremely small and the chips extremely dense, the defects increase significantly. As a result, some bit(s), when

they are read out from the storage cells, would be different from those which has been stored. In this case, we say error(s) occurring in the word. The presence of these errors greatly decreases the reliability of the computer memory.

There are several types of errors. Some of them are permanent in position and nature, the others are temporary and random. These errors are classified as hard and soft errors. On the other hand, Some errors are symmetric in error directions (the errors can be either 1'-0' and 0'-1'), and others are asymmetric errors (only one 1'-0' or 0'-1' is possible, but not both). In this section we will briefly discuss the errors and their mechanisms, including hard errors, soft errors and unidirectional errors.

#### Hard errors

If the error in any position of a word is permanent in nature, then it is called a hard error <sup>[2.7]</sup>. One of the properties of hard errors is that once it has happened at some locations the output of this location is permanently stuck at 1' or 0' state regardless of what was written in. Defective cells, internally failed connections between selection lines, such as short and open leads, are most likely sources of the hard errors. Several kinds of hard failures have been reported<sup>[2.5]</sup>. A single cell failure, for example, can occur as a hard error. There are also multiple errors caused by row failure, column failure, row-column failure and even a whole chip failure. However by proper memory organizations, the error patterns can be limited to single errors in every memory

word.

Hard errors are random, permanent, and irreversible. They can occur during the fabrication or latter on in the service time. In practice some schemes are used to deal with the hard errors in semiconductor memories. Such as on-line testing and switching to spares, replacing the defective chips etc. With the improvement of VLSI technology, the rate of hard errors has been decreased dramatically.

By the improvement of VLSI techniques and proper memory organizations, for example, one-bit-per-chip organization, the hard errors in computer memory appear usually as single errors.

#### Erasures

A hard error has a fixed position, therefore once it has been detected, the position is then known in next memory operation cycles. Thus in the next read operation, we know if the bit is correct or not. This type of errors is called erasures. With erasures we define a symbol in a word with known location but with unknown value<sup>[2.6]</sup>. Clearly a hard error is random in position while an erasure's position is known.

#### Soft errors

If the error is of a transient type, then it is called soft error. Soft errors are caused by system noise, power surges and alpha-particles radiation. Compared with hard errors, soft errors are random, temporary and reversible. In the next memory cycle the

faulty bit does not show any greater chance of being in error than that of other bits in the memory. Therefore the schemes mentioned above for hard errors are not effective to soft errors.

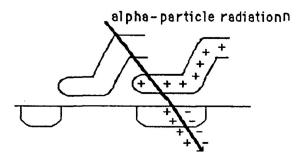

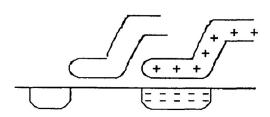

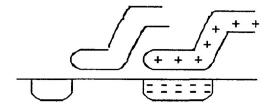

Experimental evidence indicates that most (more than 90 percent) soft errors seen in devices from several manufactures are due to alpha-particle radiation from packaging materials. In the following, we will give a brief discussion about the mechanism of alpha-particle inducing soft errors in DRAM memories [2.8, 2.9].

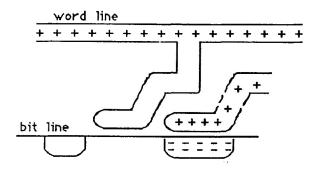

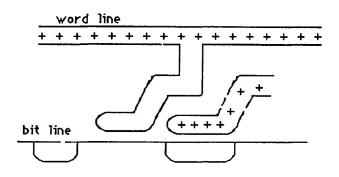

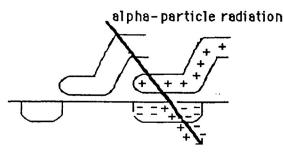

In a integrated DRAM storage cell, the presence and absence of the negative charges in the capacitor represents the 0' and 1' state respectively (in N-channel the minority carriers are electrons). If the negative charges stored in the capacitor are discharged or the no-charged capacitor acquires enough electrons by rather than an ordinary memory operation, the 0' state might change to 1' state or vice versa, then the stored bit would be erroneous. We will see that this is the way that alpha-particles cause errors.

An alpha-particle is emitted by radioactive decay of Uranium and Thorium which are present in packaging materials. When an alpha-particle penetrates semiconductor memory devices, it can create enough electron-hole pairs near a storage node. These electrons and holes diffuse through the bulk silicon. For those which reach the edge of storage region (depletion region), the electrons are swept into depletion region while the holes ohmically move through the substrate. If the normal state of the capacitor is in the no charged state (1' state), the depletion region is said 'empty'. In this situation, when an alpha-particle generates

enough electrons and holes near the depletion region, the swept electrons will be collected in the region such that the empty region is filled with the electrons which represent a 0' state. Thus an alpha-particle causes an 1'-to-0' error. On the other hand, if the normal state of the capacitor is in the charged state (0' state) originally, the depletion region is initially full of electrons. In this situation when some generated electrons are swept into the depletion region, the 'full' state will not be changed, hence the cell remains the 0' state without being affected by the alpha-particle (holes can not been swept into the depletion region because holes do not move without electron's moving). Therefore alpha-particles only disturb the 'empty' state of the Figure 2-13 shows graphically the mechanism of the capacitor. alpha-particle inducing soft errors.

Further research also shows that alpha-particles have other properties which is critical to the soft errors as following

- a) alpha-particle travels in nearly straight line

- b) the scatter in range is small

- c) alpha-particle emits at discrete energies

- d) alpha-particle emission is nuclear event and is unaffected by temperature, pressure, etc.

Alpha-particle affects not only DRAM memories but also some high speed bipolar memories<sup>[2.10]</sup>. When an alpha-particle hit the cell, it induces short transient current between the junctions of devices and circuit elements. These current flows through the collector of an N-P-N transistor to the substrate cause a potential

(a) 'O' state is represented by 'full well'

(a') '1' state is represented by 'empty well'

(b) alpha-particle penertrating and disturbing the 'O' state

(b') alpha-particle penertrating and disturbing the '1' state

(c) 'full well' is still in 'O' state without being affected by alpha-particle

(c') 'empty well' is changed to full by alpha-particle and '1' state is changed to '0' state

Fig. 2-13 Mechanisms of soft error induced by alpha-particle

dip at the collector. If that happens to be the collector of OFF transistor, it may cause a state changing. As a result, the state of the flip-flop is changed. Thus an error occurs because of the alpha-particle.

According to the discussion it can be seen that the distribution of the soft errors in semiconductor memories show up as single, random, and temporary errors.

### Unidirectional errors

If all errors in a memory are of either 1'-to-0', or 0'-to-1' type, but not both, then the errors are called asymmetric errors. If all errors in a particular word are of either 1'-to-0', or 0'-to-1' type, but not both, then the errors are called unidirectional errors. The most likely faults in some of the recently developed LSI/VLSI ROM and RAM memories cause unidirectional errors<sup>[2.11, 2.12]</sup>. Such as the faults that affect address decoder, word lines, power supply, and stuck-fault in a sense bus, etc<sup>[2.13]</sup>.

- i) Address decoder: Single and multiple faults in address decoder may result in either no access or multiple access. No access yields an all-0-word read out from the memory and multiple access cause the OR of the several word to be read out. In both cases the resulting errors are unidirectional errors.

- ii) Word line: An open word line may cause all bits in the word beyond the point of failure to be stuck at 0'. On the other hand, two word lines shorted together will form an OR function beyond the point where they shorted.

iii) Power supply: A failure in the power supply usually results in a unidirectional error.

# 2.4 Summary

We have discussed semiconductor storage cells, Memory organizations and mechanisms of various errors. An important concept is that in modern computers almost all main memories are made of LSI/VLSI chips. Thousands of cells fabricated on a single chips makes it possible to form very large capacity memories. Any cell failure on a chip will cause the chip to be failed. Any type of chip failure will cause errors. The common type of chip failure is single-cell failure caused by alpha-particle radiation. However there are also several other types of chip failures caused by hardware defects. These failures may cause multiple errors in the memory as well.

By proper memory organization design, for example, a bit-perchip organized memory, it is able to disperse the multiple errors

into different words such that when a chip is in failure, no

matter what kind of failure, it only affects a single bit in a

word. Thus in most cases the single bit error in a word is the

dominating situation (comparing with memories of magnetic tapes and

disks, in which, the usual errors are of random and burst

distribution caused by defects, dust particles and magnetic head

noises etc). Therefore for a semiconductor computer memory system

the single error detecting and correcting ability is of particular

significance.

#### References

- 2.1 O.R. Lawrence "Computer Technology" McGraw-Hill Ryerson Limited, 1984

- 2.2 S. Middelhock, P.K. George, P.D. Dekker "Physics of Memory Devices" Academic Press Inc. 1976

- 2.3 Walter A. Triebel, Alfred E. Chu "<u>Handbook of Semiconductor</u> and <u>Bubble Memories</u>" Prentice-Hall, Inc., Englewood Cliffs, NJ 07623, 1982

- 2.4 Richard E. Matick "Computer Storage & Technology" Wiley-Inter science Publication John Wiley & sons, 1977

- 2.5 Mario Blaum, Rodney Goodman, and Robert Mceliece "The Reliability of Single-Error Protected Computer Memories" IEEE Transactions on Computer No. 1, Jan. 1988 pp 114-119

- 2.6 Carl-Erik W. Sundberg "Erasure and Error Decoding for Semiconductor Memories" IEEE Transactions on Computers vol.c-27 No.8, August 1978, pp 696-705

- 2.7 T. R. N. Rao E. Fujiwara "<u>Error-control Coding for Computer</u>

<u>Systems</u>" Prentice-Hall Inc 1989

- 2.8 Timothy. May "Alpha-particle-induced Soft Error in Dynamic Memories" IEEE Transaction on Electron Devices, vol. ed-2, No. 1, Gin. 1979 pp 2-9

- 2.9 Robert J. McEliece " The Reliability of Computer Memory"

Scientific American Vol. 252. No. 1, Gin. 1985, pp 88-92

- 2.10 Denndy. Tang, Ching-Te Chuang "A Circuit Concept for Reducing Soft Error in High-speed Memory Cells" IEEE of solid-state circuits, Vol. 23, No. 1, Feb. 1988, pp 201-203

- 2.11 Dimitris Nikolo "Theory and Design of t-error Correcting d-Error Detecting (d>t) and All Unidirectional Error Detecting Codes" IEEE Transaction on Computers 40, No. 2, Feb 1991, pp 132-141

- 2.12 Serban D. Constantin and T. R. N. Rao "On the Theory of Asymmetric Error Correcting Codes" Information and Control 40, (1979), pp 200-235

- 2.13 D. K. Prandhan, J. J. Stiffler "Error-correcting and Self-Checking Circuits" IEEE Computer, March 1980, pp 37-37

#### CHAPTER THREE LINEAR CODES

In this chapter we review the basic concepts of linear codes and introduce Hamming codes and BCH codes. The detailed discussions can be found in any text book on the coding theory. Some of them are listed in the end of the chapter.

# 3.1 Basic concepts of linear codes

We suppose that a message word which is to be stored in memory has a form of  $\mathbf{u} = u_0 u_1 \dots u_{k-1}$ . This is a k-tuple. For binary information (we only consider binary information in this chapter) the maximum number of message words is  $2^k$ . By adding some redundant bits to the message word, we convert the k-tuple u to a n-tuple  $\mathbf{x}$  (=  $x_0x_1...x_{n-1}$ ). This process of converting is called encoding. The new n-tuple is accordantly called a codeword. encoding is performed in a encoder. Every message word can be uniquely encoded into a codeword. All the codewords form a codeword set called code C (there are  $2^k$  codewords in C). If we define the n-tuples as a vector space  $\mathbf{V}_n$ , then there are  $2^n$ -tuple vectors in the space. The code C is a subspace of the vector space This code is also denoted as an (n, k) code.  $\mathbf{V}_{n}$  .

In a computer memory with coding, the message word  ${\bf u}$  which is from a CPU data register is firstly encoded into a codeword  ${\bf x}$ , and then the codeword is stored in the memory locations. Compared to the original message word of k bits, a codeword uses n bits to represent the same information. Thus r (= n - k) more bits are

Therefore a codeword needs more memory space to store the redundant bits. But we will see that these redundant bits make it possible to detect and correct errors when they occur in codewords. This way coding enables to improve the reliability of a memory with errors. As we have known, when a codeword is read out from memory, it may be different from what it was stored. Before the original message word  ${\bf u}$  is recovered from the codeword, it is necessary to ensure the read codeword is error free. The process of correctly recovering the message from a read codeword is called decoding. Use of the redundancy, a decoder first checks if the read codeword is a valid codeword. If it is, the read codeword is accepted as correct, and the message word  $\mathbf{u}$  is then extracted from the Otherwise the error(s) is said to be detected. codeword. The decoder can be designed to have ability of detecting, or correcting error(s) or both. Clearly, we hope using fewer redundant bits to detect and correct more errors in a codeword. The ratio of R = k/nis defined as the rate of the code. Redundancy coding is the study of using redundancy to detect and correct errors effectively.

As an example we consider a memory, in which the probability of an error occurrence is  $p=10^{-6}$ . We suppose a message word consists of four bits. In this memory any one or more than one erroneous bit(s) in a message word will spoil the message word and result in an erroneous word. Therefore the probability of reading a word that is in error in the memory is expressed as following

However if a (7, 4) code is applied to the memory, then every 4-bit message word is encoded to a 7-bit codeword. We suppose the

$$P_1 = \sum_{j=1}^4 {4 \choose j} p^j (1-p)^{4-j} = 4p + O(p^2) = 4x \cdot 10^{-6}$$

code is capable of correcting a single error occurring in the codeword. Thus any single bit error will no longer cause a erroneous word but any two or more than two bit errors do so. Therefore the probability of obtaining a erroneous codeword from the memory can be calculated as

$$p_2 = \sum_{j=2}^{7} {7 \choose j} p^{j} (1-p)^{7-j} = 21p^2 + O(p^3) = 21 \times 10^{-12}$$

It can be seen that coding uses more bits but provides significant improvement of reliability.

There are systematic and nonsystematic codes. For a systematic code C, the first k bits of a codeword are a copy of message bits and the last r = n - k bits are the redundancy called parity check bits. In computer memories systematic codes are widely used. This is because these codes have simple implementations.

# Generator matrix of code C

Since a code C is a subspace of  $\mathbf{V}_n$ , it is possible to find k linearly independent vectors  $\mathbf{g}_0$   $\mathbf{g}_1 \dots \mathbf{g}_{k-1}$  in C such that every codeword x in C is a combination of these k vectors. This can be generally expressed as

$$\mathbf{x} = \mathbf{u}_0 \mathbf{g}_0 + \mathbf{u}_1 \mathbf{g}_1 + \dots + \mathbf{u}_{k-1} \mathbf{g}_{k-1}$$

$$= \mathbf{u} \cdot \mathbf{G} \tag{3.1}$$

where  $\mathbf{u} = u_0 u_1 \dots u_{k-1}$ , and  $\mathbf{g}_i$ 's can be arranged as a matrix as

following

$$G = \begin{vmatrix} \mathcal{G}_{0} \\ \mathcal{G}_{1} \\ \vdots \\ \mathcal{G}_{k}-1 \end{vmatrix} = \begin{vmatrix} \mathcal{G}_{00} & \cdot & \cdot & \cdot & \mathcal{G}_{0,n-1} \\ \mathcal{G}_{1,0} & \cdot & \cdot & \cdot & \mathcal{G}_{1,n-1} \\ \vdots & \vdots & \ddots & \ddots & \vdots \\ \mathcal{G}_{k-1,0} & \cdot & \cdot & \cdot & \mathcal{G}_{k-1,n-1} \end{vmatrix}$$

$$(3.2)$$

Eq. (3.1) means that when the matrix of G is given, for any message word  $\mathbf{u} = u_0 u_1 \dots u_{k-1}$ , the corresponding codeword can be uniquely generated through the rows of the G matrix. Therefore the code C is the row space of the G matrix. For this reason the matrix G is called a generator matrix for code C.

A generator matrix G has the properties as following

- i) For a (n,k) code the generator Matrix G is a (k x n) matrix.

- ii) Every row of the G matrix is a codeword in C

- iii) Any k linearly independent codewords in C can be used to form

a G matrix.

- iv) Elementary row operations performed on the **G** gives different generator matrices which also generate C.

- v) One generator matrix may be more useful than another. For example, after some elementary row operations we can obtain a generator matrix which has the form as following

$$G = \begin{vmatrix} g_0 \\ g_1 \\ \vdots \\ g_{k-1} \end{vmatrix} = \begin{vmatrix} 1 & 0 & 0 & \dots & 0 & p_{00} & p_{01} & \dots & p_{0,n-k-1} \\ 0 & 1 & 0 & \dots & 0 & p_{10} & p_{11} & \dots & p_{1,n-k-1} \\ \vdots & \vdots \\ 0 & 0 & 0 & \dots & 1 & p_{k-1,0} & p_{k-1,1} & \dots & p_{k-1,n-k-1} \end{vmatrix} = |I_k \cdot P|$$

(3.3)

where  $\mathbf{P}$  is a  $(k \times r)$  matrix of 0's and 1's, and  $\mathbf{I}_k$  is a  $(k \times k)$  unit matrix. This is a generator matrix for systematic codes (note that row operations alone may not always result in a systematic form. Sometimes column permutation may be also required to obtain a systematic form<sup>[3,1]</sup>).

**Example.** A generator matrix G for a (7, 4) systematic code is given as following

$$G = \begin{vmatrix} g_0 \\ g_1 \\ g_2 \\ g_3 \end{vmatrix} = \begin{vmatrix} 1 & 0 & 0 & 0 & 1 & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 0 & 1 & 1 & 1 \\ 0 & 0 & 0 & 1 & 1 & 0 & 1 \end{vmatrix}$$

(3.4)

If the given message word is u = 1101, according to Eq. (3.1) the corresponding codeword is calculated as

$$\mathbf{x} = 1 \cdot \mathbf{g}_0 + 1 \cdot \mathbf{g}_1 + 0 \cdot \mathbf{g}_2 + 1 \cdot \mathbf{g}_3$$

= (1000110) + (0100011) + (0000000) + (0001101)

= (1101 000)

The first four bits are message bits and the last three bit are the parity check bits. All  $2^k = 2^4 = 16$  codewords generated same way are given in Table 3.1.

# Parity check matrix of code C

In decoding, the first thing is to check the validity of a codeword read from the memory.

Since G matrix is a  $(k \times n)$  matrix with k linearly independent

Table 3.1 A (7,4) code

| message word | code word |

|--------------|-----------|

| 0000         | 0000 000  |

| 0001         | 0001 101  |

| 0010         | 0010 111  |

| 0011         | 0011 010  |

| 0100         | 0100 011  |

| 0101         | 0101 110  |

| 0110         | 0100 100  |

| 0111         | 0111 001  |

| 1000         | 1000 110  |

| 1001         | 1001 011  |

| 1010         | 1010 001  |

| 1011         | 1011 100  |

| 1100         | 1100 101  |

| 1101         | 1101 000  |

| 1110         | 1110 010  |

| 1111         | 1111 111  |

|              |           |

rows, there exists an  $(r \times n)$  matrix  $\mathbf{H}$  with r linearly independent rows such that any vector in the row space of G is orthogonal to the rows of the  $\mathbf{H}$  matrix. Or in other words, any codeword  $\mathbf{x}$  in G is orthogonal to the rows of the  $\mathbf{H}$  matrix. These relationships can be expressed in Eq. (3.5a) and (3.5b)

$$\mathbf{G} \ \mathbf{H}^{T} = 0$$

(3.5a)

$\mathbf{x} \ \mathbf{H}^{T} = 0$  (3.5b)

Such a **H** matrix can be used to verify the validity of a codeword in C. A codeword is a valid codeword if and only if it satisfies Eq. (3.5b), otherwise the codeword is in error. This **H** matrix is called the parity check matrix.

Given a generator matrix G shown in Eq. (3.2), the parity check matrix for a systematic code can be derived as

$$H = |P^{T}I_{r}| = \begin{vmatrix} p_{00} & p_{10} & \dots & p_{k-1,0} & 1 & 0 & 0 & \dots & 0 \\ p_{01} & p_{11} & \dots & p_{k-1,1} & 0 & 1 & 0 & \dots & 0 \\ \vdots & \vdots & \ddots & \vdots & \vdots & \ddots & \vdots & \vdots \\ p_{0,r-1} & p_{1,r-1} & \dots & p_{k-1,r-1} & 0 & 0 & 0 & \dots & 1 \end{vmatrix}$$

(3.6)

The first k columns in the **H** matrix are corresponding to the message bits and the last r columns to the parity check bits.

The H matrix has following properties:

- i ) A H matrix for an (n, k) code is a (r, n) matrix.

- ii) Any valid codeword in C is orthogonal to the rows of the H matrix. That is

$$\mathbf{x} \ \mathbf{H}^{\mathrm{T}} = 0 \tag{3.7}$$

According this property, we conclude that for any codeword x

and  $\mathbf{y}$  in C,  $(\mathbf{x}\mathbf{H}^T + \mathbf{y}\mathbf{H}^T) = (\mathbf{x} + \mathbf{y})\mathbf{H}^T = 0$ . This means, in a linear code C, the sum of any two codewords is still a codeword in C.

iii) An **H** matrix also defines the code C. In fact, the **H** matrix is more convenient to describe a code than the generator matrix does.

### Syndrome of a codeword

For a codeword x, if Eq. (3.7) is not satisfied, error(s) is said to be detected. But Eq. (3.7) does not provide any information about the position of the error(s), so correction can not be performed. To do so, a so called syndrome of a codeword is required.

Let us suppose that the codeword stored in the memory is  $\mathbf{x} = \mathbf{x}_0 \mathbf{x}_1 \dots \mathbf{x}_{n-1}$ , and the codeword read from the memory is  $\mathbf{d} = \mathbf{d}_0 \ \mathbf{d}_1 \ \dots \ \mathbf{d}_{n-1}$ . Due to the errors in the memory,  $\mathbf{d}$  may differ from  $\mathbf{x}$  in one or more bit positions. That is

$$\mathbf{d} = \mathbf{x} + \mathbf{e} \tag{3.8}$$

where  $\mathbf{e}$ , is an n-tuple called the error vector or error pattern. It has 0's in those positions where  $\mathbf{d}$  and  $\mathbf{x}$  agree and 1's in those positions where  $\mathbf{d}$  and  $\mathbf{x}$  disagree. In other words, the 1's in  $\mathbf{e}$  mark the position where error have occurred.

When  ${\bf d}$  is read from the memory, the decoder uses the  ${\bf H}$  matrix to calculate an r-tuple vector  ${\bf S}$ :

$$\mathbf{S} = \mathbf{d}.\mathbf{H}^{\mathrm{T}} = \mathbf{x}.\mathbf{H}^{\mathrm{T}} + \mathbf{e}.\mathbf{H}^{\mathrm{T}}$$

$$= \mathbf{e}.\mathbf{H}^{\mathrm{T}} = (s_0 \ s_1...s_{n-k-1}) \tag{3.9}$$

This is called the syndrome of  $\mathbf{d}$ . If  $\mathbf{S} = 0$ , then  $\mathbf{d}$  is a valid

codeword. If  $\mathbf{S}$  <> 0, then d is an invalid codeword, thus error(s) are detected. Furthermore, for different error patterns  $\mathbf{e}$ , the syndrome  $\mathbf{S} = (s_0 \ s_1 \dots s_{n-k-1})$  has different values. Therefore the syndrome can be used to determine the error patterns. Once the error pattern is specified, the correction of the codeword is achieved by bitwise XOR operations on  $\mathbf{d}$  and  $\mathbf{e}$ , namely, the correct codeword is obtained from  $(\mathbf{d} + \mathbf{e})$ . There are  $2^r$  unique syndromes for an (n, k) code, hence a linear (n, k) code is capable of correcting up to  $2^r$  error patterns.

As an example, we consider a (7, 4) code generated by Eq. (3.4). Eq. (3.10) is the **H** matrix of the code which is derived from Eq. (3.4) and Eq. (3.6)

$$H = \begin{bmatrix} 1 & 0 & 1 & 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 \\ 0 & 1 & 1 & 1 & 0 & 0 & 1 \end{bmatrix}$$

(3.10)

Suppose a codeword which was stored in the memory is  $\mathbf{x} = 1000110$ , and the read codeword is  $\mathbf{d} = 1000111$ , in which the last bit position is in error. So the error pattern is  $\mathbf{e} = 0000001$ . According to Eq.(3.9), the syndrome of the read codeword  $\mathbf{d}$  can calculated as

$$S = d \cdot H^{T} = \begin{vmatrix} 1 & 0 & 0 & 0 & 1 & 1 & 1 \\ 1 & 0 & 1 & 1 \\ 1 & 0 & 0 & 1 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 \end{vmatrix} = (0 \ 0 \ 1)$$

(3.11)

or use the error pattern

$$S = \mathbf{e} \cdot H^{T} = \begin{vmatrix} 00000001 & 1 & 1 \\ 1 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{vmatrix} = (0 \ 0 \ 1)$$

(3.12)

Of cause, before the syndrome has been obtained the decoder does not know the error pattern, only Eq.(3.11) is performed in the decoder. Once the syndrome (001) is obtained, the error pattern  $\mathbf{e} = 0000001$  is specified. In the same way the other seven single-bit error patterns and their syndromes can be calculated and are shown in Table 3.2.

Unfortunately, the syndrome calculated from Eq. (3.9) does not specify an unique error pattern. For example, both 0000001 and 1010000 error patterns result in a syndrome 001. In Table 3.2 we have also provided two-bit error patterns which are sharing the same syndrome. They are denoted as error-pattern(I) and error-pattern(II), respectively. In fact, for a any codeword d, there are as many as  $2^k$  error patterns that satisfy the Eq. (3.9). Only one of them is the real error pattern<sup>[3.2]</sup>. Therefore when a syndrome is obtained from Eq. (3.11), the decoder has to determine which error pattern is the real one. Strictly speaking, this is very difficult. Fortunately in computer memories, in which the 1

Table 3.2 Syndrome and error patterns

| syndrome | error pattern I | error pattern II |

|----------|-----------------|------------------|

| 001      | 0000001         | 1010000          |

| 010      | 0000010         | 0100001          |

| 100      | 0000100         | 0110000          |

| 101      | 0001000         | 0010010          |

| 111      | 0010000         | 1000001          |

| 011      | 0100000         | 1001000          |

| 110      | 1000000         | 0000110          |

error pattern I: all possible single errors.

error pattern II: some combinations of double errors.

-error and 0-error occur with the same probability, single error is dominant. Most probable error patterns are assumed to be ones that has the smallest number of 1's shown up in the column of error-pattern(I) in Table  $3.2^{[3.3]}$ . Otherwise multiple error correcting codes are required.

## The capacity of error detection and correction

In coding we have another problem. If there are several errors occurring in a codeword, the codeword may be changed into another valid codeword in C rather than into an invalid codeword. In this case, neither the H matrix or the syndrome is impotent.

To reduce the occurrence of such decoding errors, it requires as many as possible bit positions in which the two codewords differ such that few errors are not able to change a valid codeword into another valid codeword. This idea can be accurately described by parameters of Hamming weight, Hamming distance and the minimum distance of a code.

The Hamming weight of a codeword or a vector x, denoted W(x), is the number of 1's in x.

The Hamming distance between two codewords x and y, denoted d(x,y), is the Hamming weight of (x-y). It also equal to the number of the positions in which the two codewords differ. That is,

$$d(x, y) = W(x - y) = W(y - x)$$

(3.13)

The minimum distance of a code, denoted  $d_{\text{min}}$  is the minimum Hamming distance between all pairs of codewords in the code.

Clearly, the bigger the minimum distance of a code, the more errors are tolerant to change a valid codeword to another. Therefore the capability of error detection and error correction of a code is associated with the minimum distance of the code. A code of minimum distance  $d_{\min}$  is able to detect  $(d_{\min} - 1)$  errors or correct t =<  $[(d_{\min} - 1)/2]$  errors in a codeword, where [Z] is the integer part of Z.

To create a code with required minimum distance  $d_{\min}$ , we have following statement: A linear code with minimum distance  $d_{\min}$  has a **H** matrix such that any  $(d_{\min} - 1)$  or fewer columns of the **H** matrix are linear independent <sup>[3,4]</sup>. This property can be used to construct linear codes of minimum distance  $d_{\min}$ . In chapter four we will use this property to construct the modified Hamming codes.

# 3.2 Hamming codes<sup>[3.1]</sup>

In this section we will construct a very interesting class of single error correcting (SEC) codes. This codes are known as Hamming codes. Since the Hamming codes have capability of correcting single error in a codeword, the Minimum Hamming distance of the codes are at least  $d_{\min} >= 3$ . According to the relationship between  $d_{\min}$  and the H matrix, the H matrix satisfies: i) no column of the matrix is a zero vector, ii) every column vector is distinct, that is the sum of any two columns in the H matrix is not

a zero vector, iii) for systematic codes, the left most r columns form an  $(r \times r)$  unit matrix (a Hamming code is not necessary a systematic code). Thus, for a given integer r, we can construct a  $(r \times 2^r)$  H matrix of a Hamming code by using all r-tuples except the zero vector to be the columns of the H matrix. Therefor a hamming code has following parameters:

code length  $n = 2^r - 1$  message word length  $k = 2^r - r - 1$  parity bit number r = n - k minimum distance  $d_{min} = 3$  error correcting t = 1

A typical Hamming code is a (15, 11) code with distance-3. The **H** matrix of the code is given as follows

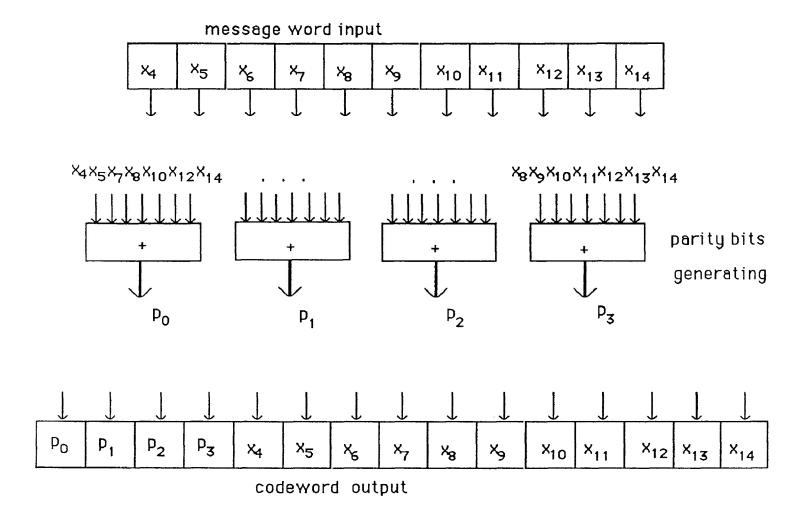

A codeword in the (15, 11) code has a form of  $\mathbf{x} = p_0p_1p_2p_3x_4x_5x_6x_7x_8x_9x_{10}x_{11}x_{12}x_{13}x_{14}$ , where  $p_i$  are parity bits and  $x_i$  are message bits. The parity bit are calculated through the parity check equations

$p_{0} = x_{4}x_{5}x_{7}x_{8}x_{10}x_{12}x_{14}$   $p_{1} = x_{4}x_{6}x_{7}x_{9}x_{10}x_{13}x_{14}$   $p_{2} = x_{5}x_{6}x_{7}x_{11}x_{12}x_{13}x_{14}$   $p_{3} = x_{8}x_{9}x_{10}x_{11}x_{12}x_{13}x_{14}$ (3.15)

The encoder for the code is then accordingly formed in

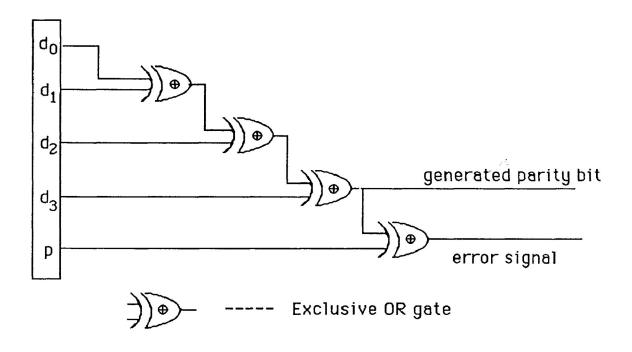

Fig. 3.1.

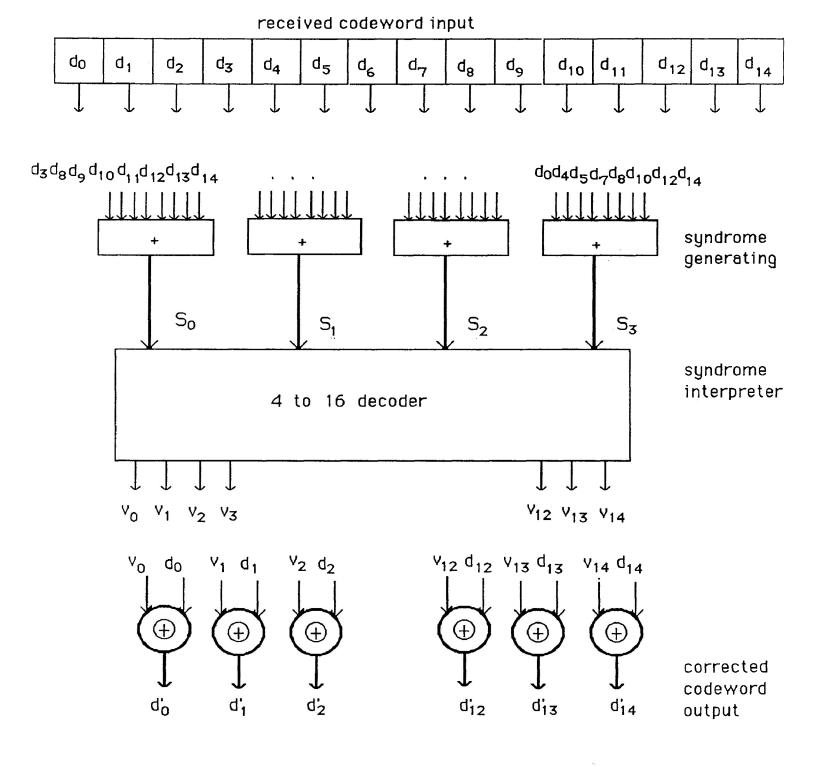

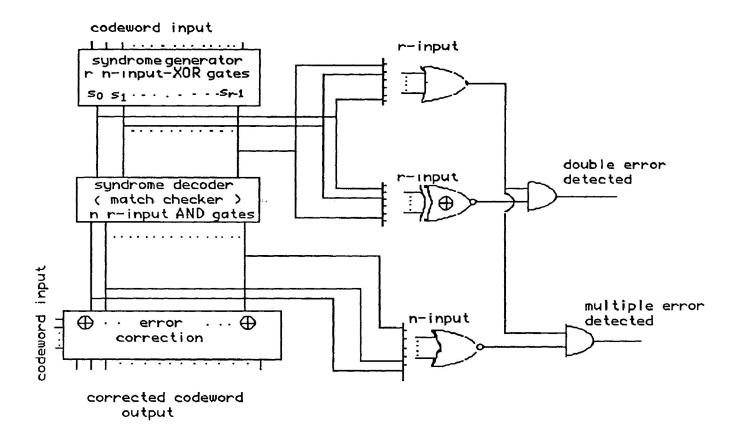

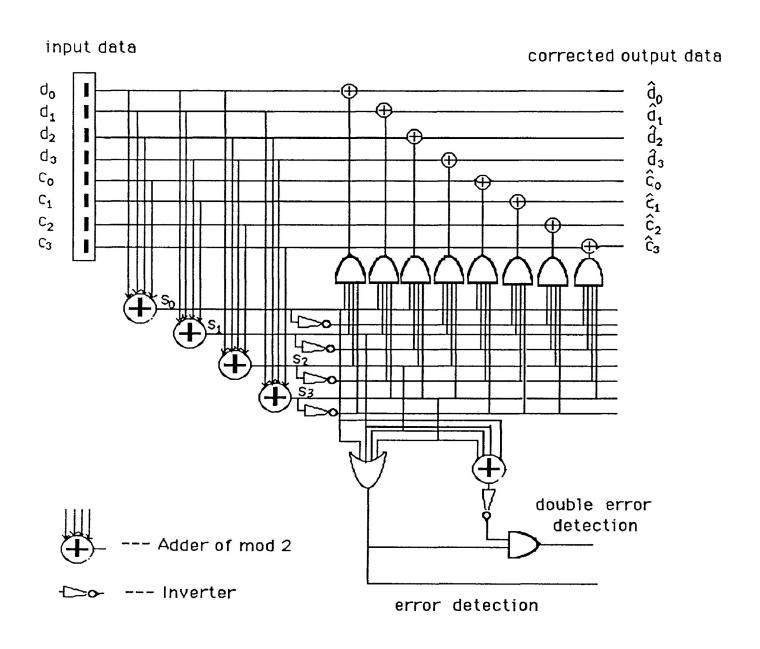

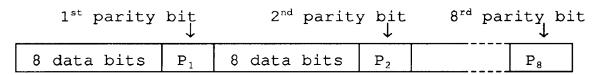

The decoding of a read codeword