# Modeling of PWM Boost Converters for Continuous and Discontinuous Inductor Current Modes

By Jie Qiu

Supervised by Dr. Krishnamoorthy Natarajan

December, 2005

A Thesis submitted in partial fulfillment of the requirements of the Msc. Eng. Degree in

Control Engineering

Faculty of Engineering

Lakehead University

Thunder Bay, Ontario

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-15640-7 Our file Notre référence ISBN: 978-0-494-15640-7

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### Abstract

Owing to the relatively more complicated nature of the boost converter with non-ideal elements and operating in continuous and discontinuous inductor current modes, a parsimonious large signal and small signal model for this converter, with and without feedback, has been lacking. In this work, a zero order hold equivalent discrete time model of the boost converter for computing its small signal frequency response and large signal and small signal closed loop behavior is developed and experimentally confirmed. The Newton-Raphson technique is used to accelerate the computation of the frequency response from the developed discrete time model. The use of the discrete time model in combination with the Newton-Raphson method in predicting the steady-state ripple behavior of the converter is also studied. With the intention of future robust control studies on the boost converter in discontinuous inductor current mode, an initial evaluation of the frequency response predicted by the discrete time model at different operating points is presented.

i

# Acknowledgment

Dr. K. Natarajan's extreme help and guidance made this work possible. I sincerely appreciate his help and support.

# Contents

| 1 | Intr | oducti  | on                                                             | 1  |

|---|------|---------|----------------------------------------------------------------|----|

|   | 1.1  | The ov  | verview of literature                                          | 1  |

|   | 1.2  | Thesis  | outline                                                        | 2  |

|   | 1.3  | Switch  | mode DC-DC converters                                          | 3  |

|   | 1.4  | Step-u  | p (boost) converter                                            | 3  |

|   | 1.5  | Contro  | ol of boost converter                                          | 3  |

|   | 1.6  | Modes   | of operation                                                   | 4  |

| 2 | Mod  | dels of | the boost converter                                            | 7  |

|   | 2.1  | Differe | ential equations of a boost converter                          | 7  |

|   | 2.2  | Discre  | te-time model                                                  | 11 |

|   |      | 2.2.1   | Discrete time model                                            | 11 |

|   |      | 2.2.2   | Calculations of $F_2$ , $G_2$ and $F_3$                        | 12 |

|   |      | 2.2.3   | Equation for $\phi$                                            | 14 |

|   |      | 2.2.4   | Newton-Raphson method to compute $\phi$                        | 16 |

|   | 2.3  | C-code  | e based simulation model                                       | 17 |

|   |      | 2.3.1   | Open-loop boost converter operation                            | 18 |

|   |      | 2.3.2   | Closed-loop boost converter operation                          | 18 |

|   | 2.4  | Conclu  | asion                                                          | 19 |

| 3 | Stea | ady-sta | ate behavior and frequency-response analysis of the boost con- | -  |

|   | vert | er                                                                     | 20 |

|---|------|------------------------------------------------------------------------|----|

|   | 3.1  | Steady-state behavior and ripple                                       | 20 |

|   |      | 3.1.1 Continuous inductor current mode                                 | 21 |

|   |      | 3.1.2 Discontinuous inductor current mode                              | 22 |

|   | 3.2  | C-code based simulation and experimental frequency-response            | 26 |

|   |      | 3.2.1 Equivalent series resistance (ESR) of capacitor                  | 28 |

|   | 3.3  | Frequency-response of the discrete-time model                          | 29 |

|   | 3.4  | Zero-order hold                                                        | 30 |

|   |      | 3.4.1 Transfer function of the zero-order hold                         | 31 |

|   |      | 3.4.2 Frequency-response of the sampled signal                         | 31 |

|   |      | 3.4.3 Zero-order hold compensation                                     | 33 |

|   | 3.5  | ZOH compensated frequency-response of the discrete time model          | 33 |

|   | 3.6  | Small signal behavior of the boost converter                           | 36 |

|   | 3.7  | Newton-Raphson technique to accelerate the computation speed of the    |    |

|   |      | frequency-response                                                     | 37 |

|   | 3.8  | Conclusion                                                             | 40 |

| 4 | Clos | sed-loop behavior analysis                                             | 42 |

|   | 4.1  | C-code based simulation and experimental closed-loop output-response . | 42 |

|   | 4.2  | Closed-loop output-response of the discrete-time model                 | 45 |

|   | 4.3  | Nonlinear behavior of the boost converter                              | 45 |

|   |      | 4.3.1 Linear behavior                                                  | 46 |

|   |      | 4.3.2 Small signal model                                               | 46 |

|   | 4.4  | Conclusion                                                             | 50 |

| 5 | Diff | erent operating point                                                  | 51 |

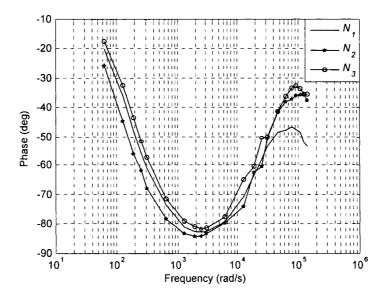

|   | 5.1  | Small signal frequency-response                                        | 53 |

|   | 5.2  | Closed-loop output-response                                            | 53 |

| 6 | Futu | ure work and conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>56</b> |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 6.1  | Robust control design using a frequency response technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56        |

|   | 6.2  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58        |

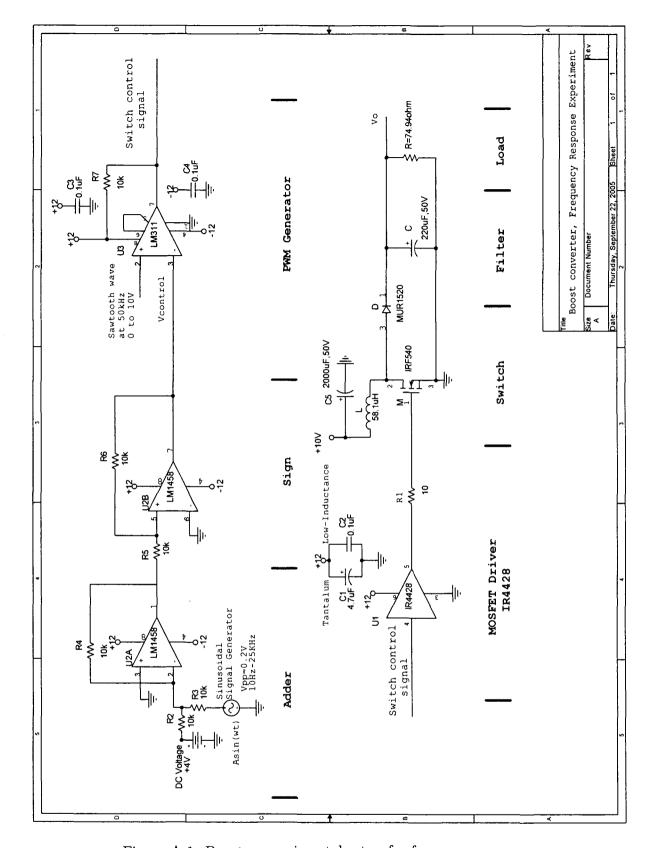

| A | Free | quency-response experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62        |

|   | A.1  | Calculation of parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62        |

|   | A.2  | Inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 63        |

|   | A.3  | Load resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64        |

|   | A.4  | Circuit notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64        |

|   |      | A.4.1 Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64        |

|   |      | A.4.2 Input power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65        |

|   |      | A.4.3 Gate resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65        |

|   |      | A.4.4 Bypassing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65        |

|   |      | A.4.5 Power dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65        |

|   | A.5  | Data collection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66        |

|   |      | A.5.1 Magnitude calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66        |

|   |      | A.5.2 Phase shift calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66        |

|   | A.6  | Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67        |

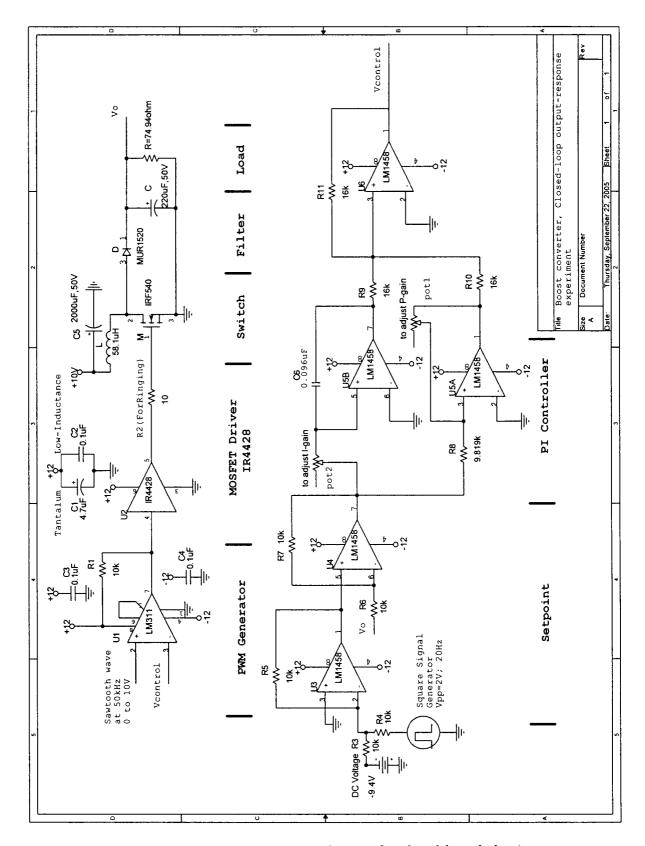

| В | Clos | sed-loop experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 69        |

|   | B.1  | Subtraction circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69        |

|   | B.2  | Controller circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69        |

|   | ъ.   | The state of the s | =-        |

# List of Figures

| 1-1 | Boost converter                                                            | 4  |

|-----|----------------------------------------------------------------------------|----|

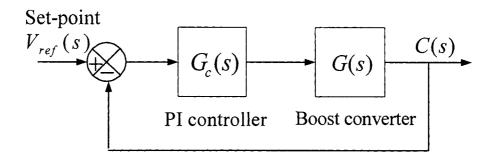

| 1-2 | Controller circuit of a boost converter                                    | 5  |

| 1-3 | Inductor voltage and current                                               | 5  |

| 2-1 | Boost converter circuit                                                    | 8  |

| 2-2 | Three topological modes of the boost converter operating in discontinuous- |    |

|     | conduction mode                                                            | 9  |

| 2-3 | Inductor current and $\phi$ in continuous-conduction mode                  | 12 |

| 2-4 | Inductor current and $\phi$ in discontinuous-conduction mode               | 13 |

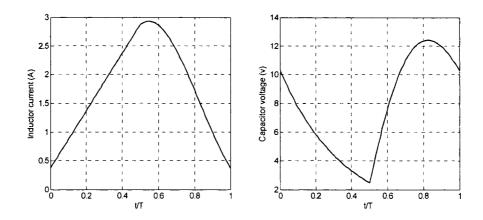

| 3-1 | Steady-state periodic waveform for boost converter of [17]                 | 22 |

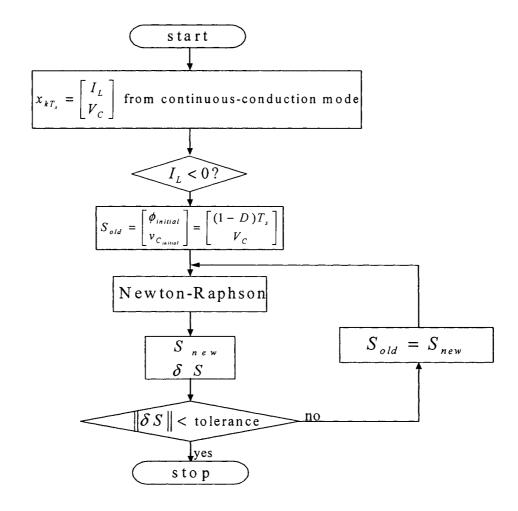

| 3-2 | Newton-Raphson technique to compute steady-state operating point           | 24 |

| 3-3 | Steady-state ripple with DC bias removed for discrete-time model and       |    |

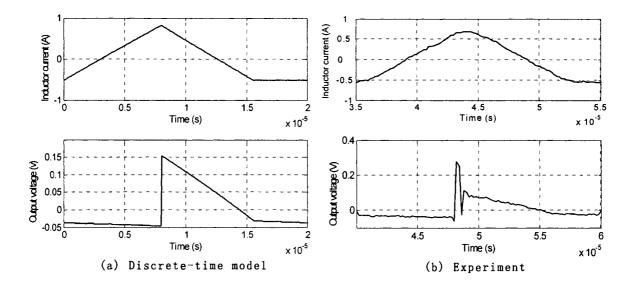

|     | experiment                                                                 | 26 |

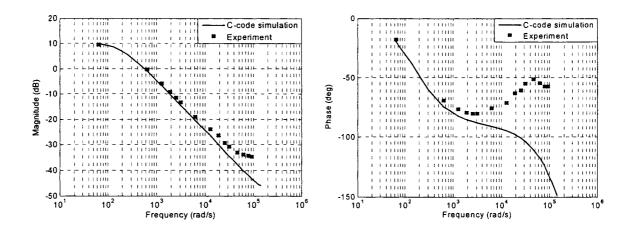

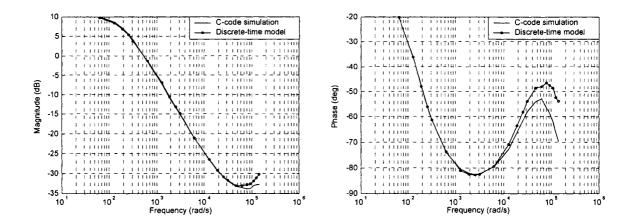

| 3-4 | Magnitude and phase frequency-responses with $r_c=0$                       | 27 |

| 3-5 | Magnitude and phase frequency-responses with $r_c=0.15\Omega$              | 28 |

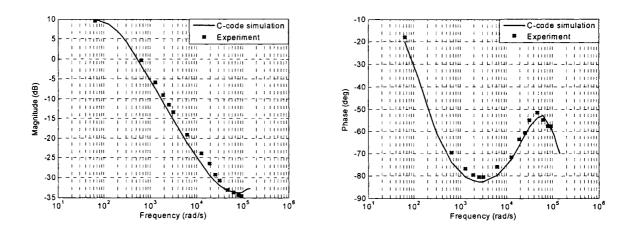

| 3-6 | Magnitude and phase of frequency-responses                                 | 30 |

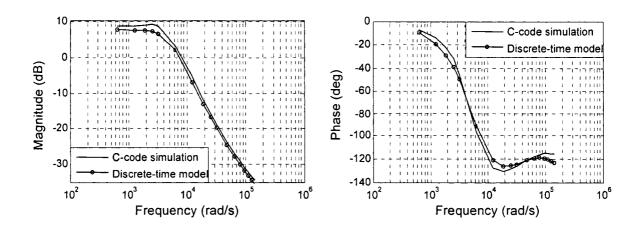

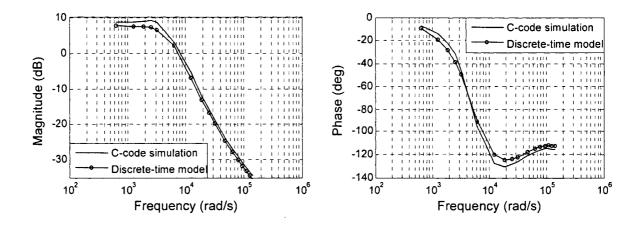

| 3-7 | Compensated magnitude and phase of frequency-responses                     | 34 |

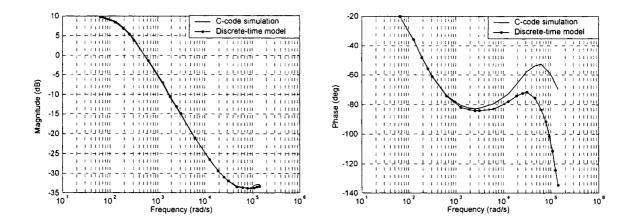

| 3-8 | Magnitude and phase of frequency-responses before ZOH compensation         |    |

|     | with $f_s = 400 \mathrm{kHz}$                                              | 35 |

| 3-9 | Magnitude and phase of frequency-responses after ZOH compensation with     |    |

|     | $f_s = 400 \mathrm{kHz}$                                                   | 35 |

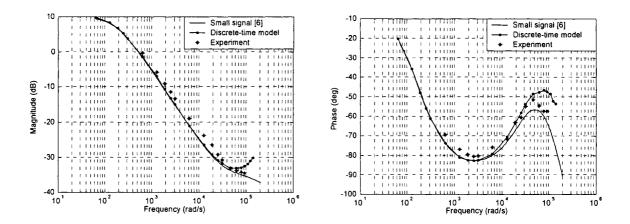

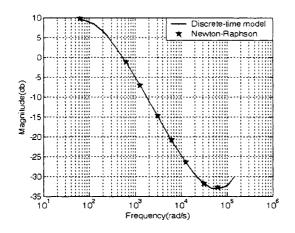

| 3-10 | Magnitude and phase of small signal frequency-response for discrete-time        | 36 |

|------|---------------------------------------------------------------------------------|----|

| 0.11 | model and experiment                                                            | ЭC |

| 3-11 | Newton-Raphson method to accelerate the computation of the frequency-           |    |

|      | response                                                                        | 38 |

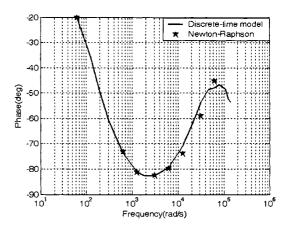

| 4-1  | Closed-loop output-responses with $B=1\mathrm{V.}$ (a) C-code based simulation. |    |

|      | (b) Experiment                                                                  | 43 |

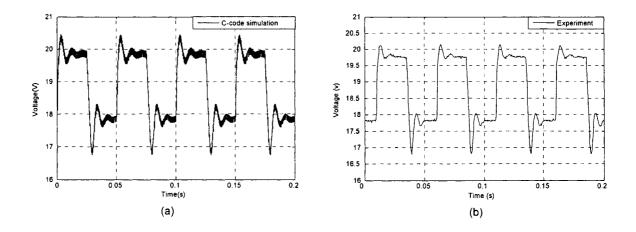

| 4-2  | Closed-loop output-responses with $B=1\mathrm{V.}$ (a) Discrete-time model (in- |    |

|      | stantaneous values of output). (b) Discrete-time model (average values of       |    |

|      | output). (c) Experiment                                                         | 44 |

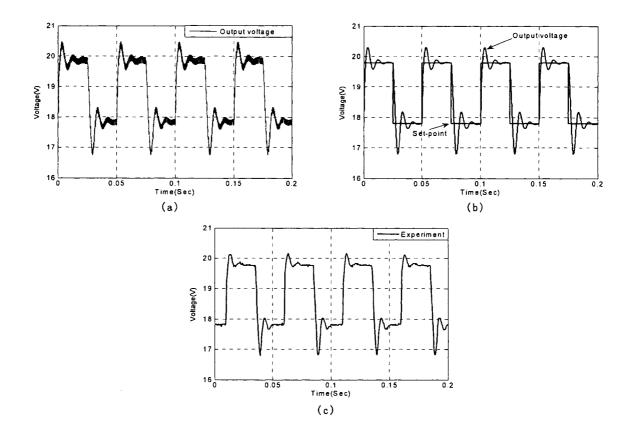

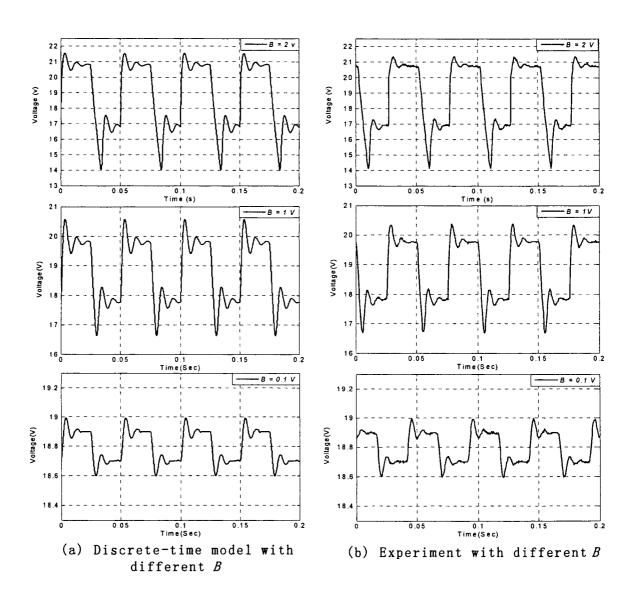

| 4-3  | Closed-loop output-responses for discrete-time model and experiment with        |    |

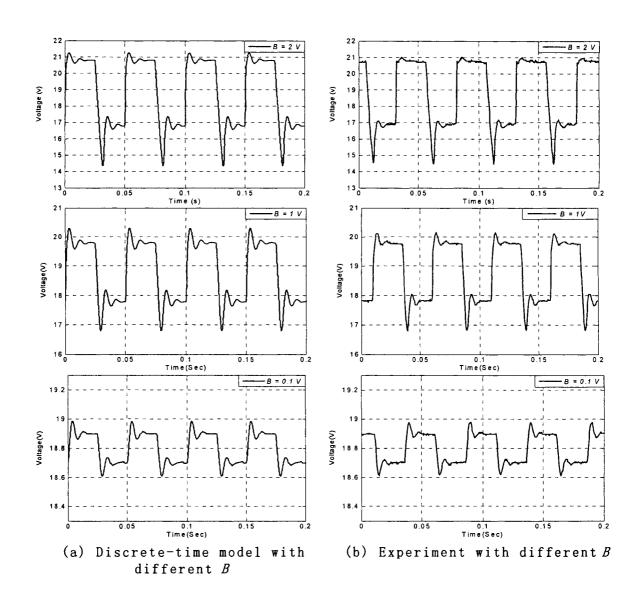

|      | different values of $B$                                                         | 47 |

| 4-4  | Control block                                                                   | 48 |

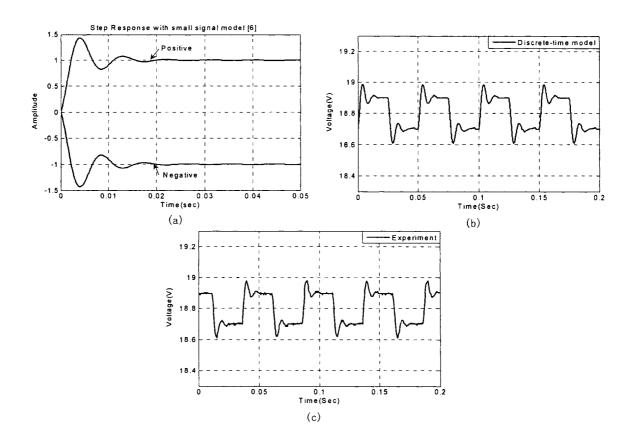

| 4-5  | Closed-loop responses with $B=0.1\mathrm{V}$ (a) Small signal model [6]. (b)    |    |

|      | Discrete-time model. (c) Experiment                                             | 49 |

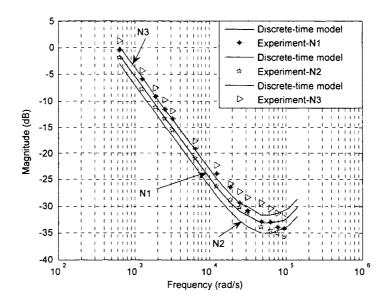

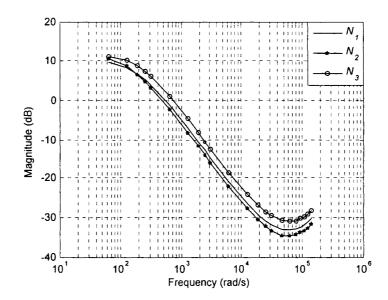

| 5-1  | Magnitude response for discrete-time model and experiment with three            |    |

|      | different operating points                                                      | 52 |

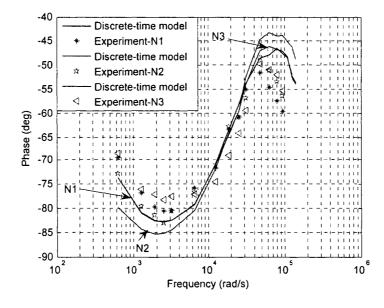

| 5-2  | Phase response for discrete-time model and experiment with three different      |    |

|      | operating points.                                                               | 52 |

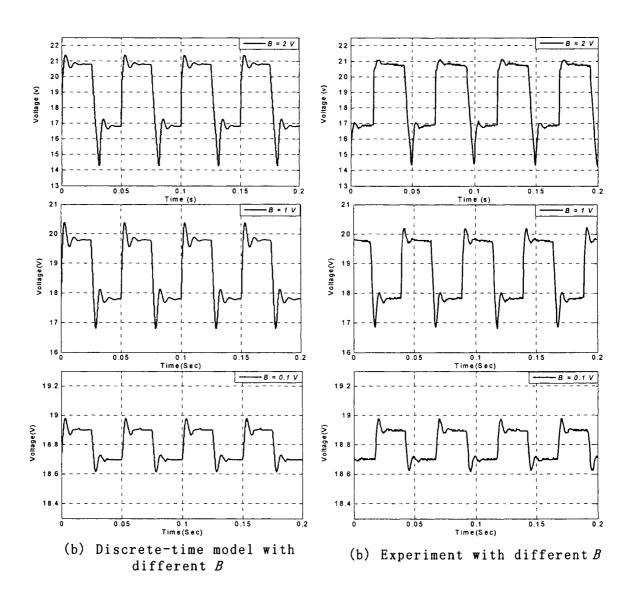

| 5-3  | Closed-loop output-responses for discrete-time model and experiment with        |    |

|      | operating point $N2$                                                            | 54 |

| 5-4  | Closed-loop output-responses for discrete-time model and experiment with        |    |

|      | operating point $N3$                                                            | 55 |

| 6-1  | Magnitude response for discrete-time model with three different operating       |    |

|      | points                                                                          | 57 |

| 6-2  | Phase response for discrete-time model with three different operating points.   | 57 |

| Λ 1  | Roost experimental setup for frequency response                                 | 69 |

| B-1 | Boost - ex | perimental | setup | for | closed-loop | behavior |  |  |  |  |  |  | , | 7 |

|-----|------------|------------|-------|-----|-------------|----------|--|--|--|--|--|--|---|---|

|     |            |            |       |     |             |          |  |  |  |  |  |  |   |   |

# List of Tables

| 3-1  | Direct frequency-response from the discrete-time model              | 39 |

|------|---------------------------------------------------------------------|----|

| 3-2  | Newton-Raphson method of computing the frequency-response           | 39 |

| 3-3  | Newton-Raphson method of computing the frequency-response           |    |

|      | with different tolerance value                                      | 39 |

| 3-4  | Newton-Raphson method of computing the frequency-response           |    |

|      | with different initial value of DC steady-state                     | 40 |

|      |                                                                     |    |

| 4-1  | Percent overshoot and settling time comparison with nonlinear       |    |

|      | behavior                                                            | 45 |

| 4-2  | Percent overshoot and settling time comparison with linear          |    |

|      | behavior                                                            | 50 |

|      |                                                                     |    |

|      |                                                                     |    |

| 5-1  | Different operating points with constant duty cycle $D \dots \dots$ | 51 |

|      |                                                                     |    |

| 6-1  | Different operating points with constant output voltage $V_0$       | 56 |

| A -1 |                                                                     | 60 |

| A-1  | Parameters of the boost converter                                   | 63 |

| A-2  | Efficiency of this experimental boost converter                     | 67 |

# Chapter 1

## Introduction

#### 1.1 The overview of literature

Various linear time-invariant models for boost converters in continuous inductor current mode of operation such as state-space averaged models [1], [2] and the PWM switch model [3] have been developed and they yield similar results. When the boost converter operates in continuous and discontinuous inductor current operation modes, owing to the relatively more complicated nature of the boost converter with non-ideal elements, a parsimonious large signal and small signal model for this converter, with and without feedback, has been lacking. Firstly, linear time-invariant small signal state-space averaged model [4] and the PWM switch model [5] with ideal elements were developed and it was observed that [5] yields results which are different from those given by the method of [4]. The fundamental difference between the two methods is that state-space averaged model predicts that the discontinuous current state does not contribute to the order of the average model while the PWM switch model predicts otherwise. Later, a small-signal circuit model of DC-DC PWM boost converters operating in discontinuous inductor current mode [6] was derived by using the energy conservation approach [7], [8] to consider some of the non-ideal effects and [6] verified the results in [5]. For robust controller design purpose, the converter closed loop behavior is often governed by the presence of both

continuous and discontinuous inductor current modes. Consequently a model which can handle both continuous and discontinuous inductor current modes easily is needed. In this thesis, a zero-order hold (ZOH) equivalent discrete time model of the boost converter for computing its small signal frequency response and closed loop behavior for both large and small signals is derived and experimentally confirmed. In this model, non-ideal effects can be easily taken into account in continuous and discontinuous inductor current modes. Earlier work done by [9] indicates that this approach can handle both continuous and discontinuous inductor current modes in the buck converter. In discontinuous inductor current mode, the use of the discrete time model in combination with a two variable Newton-Raphson technique with analytical Jacobian in predicting steady-state behavior is also studied. For robust controller design, ZOH modeling of state-space descriptions has the potential of developing frequency response characteristics which are obtained from the developed model of this thesis.

#### 1.2 Thesis outline

The organization of the thesis is as follows. Chapter 1 provides an introduction to the basic concept of the boost converter. In Chapter 2 two kinds of models are introduced. The models include C-code based simulation model and a discrete-time model, which is a ZOH model of the boost converter for both continuous and discontinuous modes of operation. In Chapter 3 the behavior of the models of Chapter 2 are observed, compared and experimentally verified in terms of steady-state and small signal frequency response. An alternative faster method using Newton-Raphson technique to accelerate the computation of frequency response from the developed discrete-time model is introduced. In Chapter 4, this discrete-time model is used to predict large signal and small signal behavior when the converter is working in closed-loop with an analog PI controller. Experimental results of such large signal behavior are presented and compared to results predicted from this discrete-time model of Chapter 2. In Chapter 5, on the basis of Chapters 3 and 4, the

behavior of the discrete-time model over different operating points is also obtained and experimentally confirmed. Chapter 6 suggests future work and concludes the thesis.

#### 1.3 Switch mode DC-DC converters

Switch mode DC-DC power converters afford an efficient means of transforming power at one DC voltage to another desired DC voltage. The basic DC-DC conversion function is achieved by controlling the switch on and off durations with constant switching frequency. Compared with linear power supply, it has greater efficiency.

#### 1.4 Step-up (boost) converter

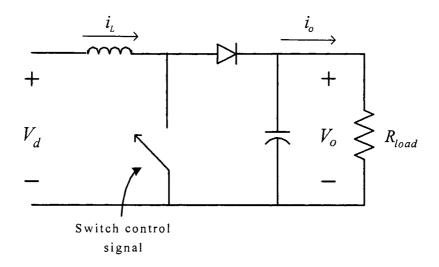

As the name implies, a boost converter produces an average output voltage  $V_o$  always greater than the DC input voltage  $V_d$ . Fig. 1-1 shows an ideal boost converter circuit. When the switch is on, the diode is reversed biased, thus isolating the output stage. The input supplies energy to the inductor. When the switch is off, the output stage receives energy from the inductor as well as from the input. The output filter essentially guarantees a relatively low ripple voltage on the load.

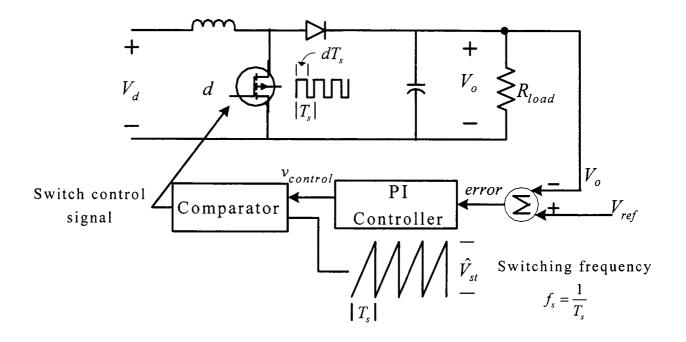

#### 1.5 Control of boost converter

The output voltages  $V_o$  of DC power supplies are regulated to be within a specified tolerance band (e.g.,  $\pm 1\%$  around its nominal value) in response to changes in the output load  $R_{load}$  and input line voltage  $V_d$ . This is accomplished by using a negative-feedback control system, shown in Fig. 1-2. One of the methods for controlling the output voltage, called Pulse-width modulation (PWM) switching, employs switching at a constant switching frequency and adjusting the on duration of the switch in order to ensure  $V_o = V_{ref}$ .

Figure 1-1: Boost converter

Duty cycle of the switch control signal is generated by comparing a control voltage signal  $v_{control}$  which is the output of the PI controller with a repetitive saw-tooth waveform of amplitude  $\hat{V}_{st}$  as shown in Fig. 1-2. The frequency  $f_s(=\frac{1}{T_s})$  and amplitude  $\hat{V}_{st}$  of the saw-tooth waveform are constant. In terms of  $v_{control}$  and the amplitude of the saw-tooth waveform  $\hat{V}_{st}$  in Fig. 1-2, the duty cycle of the switch control signal can be expressed as

$$d = \frac{v_{control}}{\widehat{V}_{st}} \tag{1.1}$$

#### 1.6 Modes of operation

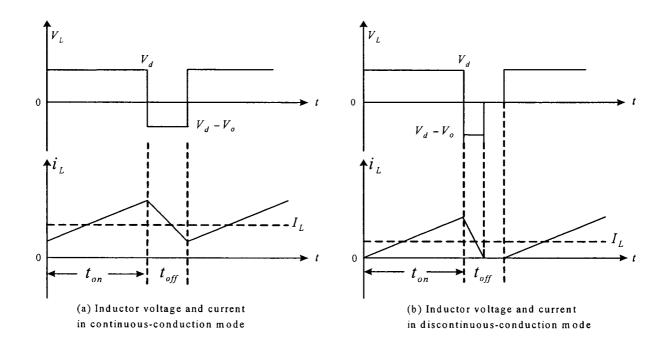

The operation of this converter can be divided into two modes according to ideal inductor current waveform. If the inductor current never falls to zero over a switching period, the converter is said to be working in  $continuous - conduction \ mode$  of operation as in Fig. 1-3.(a). If the inductor current becomes zero for a portion in the switch off  $(t_{off})$  period as in Fig. 1-3.(b), then the converter is working in  $discontinuous - conduction \ mode$ . At

Figure 1-2: Controller circuit of a boost converter

Figure 1-3: Inductor voltage and current

the boundary between continuous and discontinuous mode, inductor current goes to zero exactly at the end of  $t_{off}$ . At this boundary, in the boost converter with ideal elements, the average inductor current is [1]

$$I_{LB} = \frac{1}{2} \frac{V_d}{L} t_{on} = \frac{T_s V_o}{2L} d(1 - d)$$

(1.2)

Recognizing that in a boost converter the inductor current and the input current are the same  $(i_d = i_L)$  and using above equation, we find that average output current at the boundary condition is

$$I_{oB} = \frac{T_s V_o}{2L} d(1 - d)^2 \tag{1.3}$$

and  $I_{oB}$  has its maximum value at  $d = \frac{1}{3} = 0.333$  given by,

$$I_{oB, \text{max}} = \frac{2}{27} \frac{T_s V_o}{L} = 0.074 \frac{T_s V_o}{L} \tag{1.4}$$

Therefore, if the average load current drops below  $I_{oB}$  (and, hence, the average inductor current below  $I_{LB}$ ), the inductor current will enter discontinuous-conduction mode else it is in continuous-conduction mode for the ideal boost converter.

# Chapter 2

### Models of the boost converter

In this chapter, a new discrete time model of the non-ideal boost converter for computing its standalone behavior in terms of steady-state and small signal frequency-response is developed. In Section 2.1, the basic differential equations of the boost converter are derived. The models discussed in following sections are all based on these equations.

#### 2.1 Differential equations of a boost converter

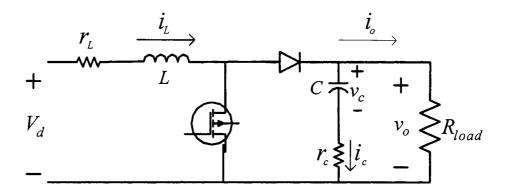

Fig. 2-1 shows the topology of the boost converter. The non-ideal elements of the converter are modeled as  $r_L$  for the inductor resistance and  $r_c$  for the capacitor equivalent series resistance (ESR). Furthermore, to more accurately model the system, the switch and diode are not considered as ideal components.

The non-ideal effects (conduction losses) induced by the switch and diode are taken into account as follows:

- 1) The MOSFET in the ON state is modeled by a linear resistance  $r_{DS}$  and in the OFF state by an infinite resistance.

- 2) The diode in the ON state is modeled by a linear voltage drop  $V_F$  and a resistance  $r_F$ . The diode in the OFF state is modeled as an infinite resistance.

Implicit switching losses induced by the switch and diode can also be modeled by

Figure 2-1: Boost converter circuit

adjusting the values of the non-ideal elements as above. It is assumed that when the switch is on, the diode is off and when the switch is off, the diode is on.

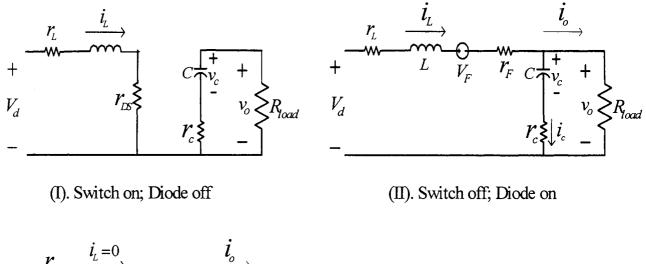

There are two topological modes for continuous conduction mode and three for discontinuous conduction mode. Fig. 2-2 shows the three topological modes of the boost converter operating in the discontinuous-conduction mode. The first two topological modes shown in Fig. 2-2 illustrate the modes in the continuous-conduction mode. The following equations can be derived based on Fig. 2-2,

For (I):

$$-V_d + (r_L + r_{DS})i_L(t) + L\frac{di_L(t)}{dt} = 0$$

(2.1)

$$-v_c(t) - C\frac{dv_c(t)}{dt}r_c + v_o(t) = 0$$

(2.2)

$$v_o(t) = -R_{load}C\frac{dv_c(t)}{dt}$$

(2.3)

$$-V_d + (r_L + r_F)i_L(t) + L\frac{di_L(t)}{dt} + V_F + v_o(t) = 0$$

(2.4)

(III). Switch off; Diode off

Figure 2-2: Three topological modes of the boost converter operating in discontinuous-conduction mode

$$-v_c(t) - C\frac{dv_c(t)}{dt}r_c + v_o(t) = 0$$

(2.5)

$$v_o(t) = R_{load} \left( i_L(t) - C \frac{dv_c(t)}{dt} \right)$$

(2.6)

For (III):

$$i_L(t) = 0 (2.7)$$

$$-v_c(t) - C\frac{dv_c(t)}{dt}r_c + v_o(t) = 0$$

(2.8)

$$v_o(t) = -R_{load}C\frac{dv_c(t)}{dt}$$

(2.9)

where  $i_L$  is the inductor current,  $v_c$  is the capacitor voltage and  $v_o$  is the voltage across the load. For the boost converter topology shown in Fig. 2-1, the differential equations governing the converter for modes I and II are written in matrix form as:

$$\begin{bmatrix} \frac{di_L(t)}{dt} \\ \frac{dv_c(t)}{dt} \end{bmatrix} = A(S) \begin{bmatrix} i_L(t) \\ v_c(t) \end{bmatrix} + B(S); \qquad v_o(t) = C(S) \begin{bmatrix} i_L(t) \\ v_c(t) \end{bmatrix}$$

(2.10)

where S,  $(\bar{S})$  is an integer variable which is 1, (0) if the switch is on and 0, (1) if the switch is off. The matrices A(S), B(S), C(S) are given by:

$$A(S) = \begin{bmatrix} -\frac{r_L + Sr_{DS} + \bar{S}r_F}{L} - \bar{S}\frac{R_{load}r_c}{L(r_c + R_{load})} & -\bar{S}\frac{R_{load}}{L(r_c + R_{load})} \\ \bar{S}\frac{R_{load}}{C(r_c + R_{load})} & -\frac{1}{C(r_c + R_{load})} \end{bmatrix}$$

(2.11)

$$B(S) = \begin{bmatrix} \frac{V_d - \bar{S}V_F}{L} \\ 0 \end{bmatrix}; \qquad C(S) = \begin{bmatrix} \bar{S}\frac{R_{load}r_c}{r_c + R_{load}} & \frac{R_{load}}{r_c + R_{load}} \end{bmatrix}$$

(2.12)

During discontinuous-conduction mode of operation, for  $i_L = 0$ , both switch and diode are off and (2.10) reduces to

$$\frac{dv_c(t)}{dt} = -\frac{1}{C(r_c + R_{load})}v_c(t)$$

(2.13)

The output equation, for this case, remains the same as in (2.10) with  $i_L(t) = 0$ .

#### 2.2 Discrete-time model

A new ZOH discrete-time model developed in this thesis is introduced here. Small-signal model [6] assumes that the perturbations are very small and converter always works in discontinuous-conduction mode or continuous-conduction mode. However for large perturbations on nominal operating point, converter will not operate in discontinuous mode only but will exhibit both continuous and discontinuous modes of operation. So the discrete-time model is developed based on both modes of operation and predicts the behavior of the converter (with and without feedback) in both modes.

#### 2.2.1 Discrete time model

In the development of the discrete-time model, the following assumptions are made:

The duty cycle d ( $0 \le d \le 1$ ) of the switch can be affected only once every switching period  $T_s$  and the switching frequency is higher than the resonant frequency of the main inductor and capacitor of the circuit. Since in practice the switching periods are being pushed to smaller values, this assumption is reasonable to make for modeling purposes.

At intervals of switching period the evolution of the state vector  $x = \begin{bmatrix} i_L(t) & v_c(t) \end{bmatrix}$  for all three modes of Fig. 2-2 is described by:

$$x_{(k+d_k)T_s} = F_1 x_{kT_s} + G_1$$

during switch on:  $d_k T_s$  (2.14)

$$x_{(k+1)T_s} = F_3 F_2 x_{(k+d_k)T_s} + F_3 G_2$$

during switch off:  $(1 - d_k)T_s$  (2.15)

where  $F_1$ ,  $F_2$ ,  $F_3$ , the state transition matrices, and  $G_1$ ,  $G_2$  are obtained as per:

$$F_1 = e^{A(1)d_k T_s}$$

$G_1 = (F_1 - I)A(1)^{-1}B(1)$  (2.16)

Figure 2-3: Inductor current and  $\phi$  in continuous-conduction mode

$$F_2 = e^{A(0)(1-d_k)T_s}$$

if  $\phi_k \ge (1-d_k)T_s$  (2.17)

$$F_2 = e^{A(0)\phi_k}$$

if  $\phi_k < (1 - d_k)T_s$  (2.18)

$$G_2 = (F_2 - I)A(0)^{-1}B(0)$$

(2.19)

$$F_3 = I \qquad \text{if} \quad \phi_k \ge (1 - d_k) T_s \tag{2.20}$$

$$F_3 = \begin{bmatrix} 1 & 0 \\ 0 & e^{a_{22}((1-d_k)T_s - \Phi_k)} \end{bmatrix} \quad \text{if} \quad \phi_k < (1-d_k)T_s$$

(2.21)

where k is an integer that indexes the switching periods. In (2.21),  $a_{22}$  is the element in the second row and second column in the A(S) matrix given in (2.11, 2.13) and  $\phi_k$  is the time duration taken by inductor current  $i_L$  to become zero after the switch is opened at time  $(k + d_k)T_s$ . If  $\phi_k < (1 - d_k)T_s$ , then the converter is in discontinuous-conduction mode else it is in continuous-conduction mode.

The terms,  $F_2$ ,  $G_2$ ,  $F_3$ , and  $\phi_k$  will be explained and derived in the next section.

#### **2.2.2** Calculations of $F_2$ , $G_2$ and $F_3$

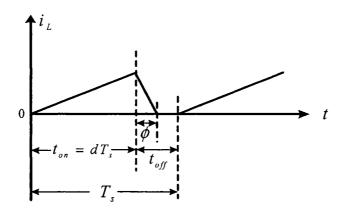

As seen from Figs. 2-3 and 2-4, two states in the  $t_{off}$  interval can be distinguished: one when inductor current flows ( $i_L > 0$ , diode is on) up to the end of the switching period and one when inductor current goes to zero before the end of the switching period

Figure 2-4: Inductor current and  $\phi$  in discontinuous-conduction mode

$(i_L = 0, diode is off).$

As seen in Fig. 2-3, if  $\phi \geq t_{off}$ , which means the inductor current flows during  $t_{off}$ , the converter is working in continuous-conduction mode. Thus,  $F_2$  and  $F_3$  in (2.15) are obtained as (2.17) and (2.20).

However, Fig. 2-4 illustrates the situation for  $\phi < t_{off}$ . When the inductor current is zero for some duration in the  $t_{off}$  interval, the boost converter is working in discontinuous-conduction mode. In this case, during the  $\phi_k$  interval, when  $i_L > 0$ ,  $F_2$ ,  $G_2$  in (2.15) are calculated as,

$$F_2 = e^{A(0)\phi_k}$$

$$G_2 = (F_2 - I)A(0)^{-1}B(0)$$

For the remaining part of the  $t_{off}$  interval, which is  $(1 - d_k)T_s - \phi_k$ , the equations for  $i_L = 0$  are applied and  $F_3$  in (2.15) is calculated as,

$$F_3 = e^{A((1-d_k)T_s - \phi_k)} (2.22)$$

With (2.7) holding in this interval and switch and diode off, the matrix (2.11) reduces to

$$A = \begin{bmatrix} 0 & 0 \\ 0 & -\frac{1}{C(r_c + R_{load})} \end{bmatrix}$$

(2.23)

Substituting (2.23) in (2.22), gives

$$F_3 = \begin{bmatrix} 1 & 0 \\ 0 & e^{a_{22}((1-d_k)T_s - \phi_k)} \end{bmatrix}$$

where  $a_{22} = -\frac{1}{C(r_c + R_{load})}$ . Thus (2.14), (2.15) in discontinuous-conduction mode are obtained as:

$$x_{(k+d_k)T_s} = F_1 x_{kT_s} + G_1 (2.24)$$

$$x_{(k+d_k)T_s+\phi_k} = F_2 x_{(k+d_k)T_s} + G_2 \tag{2.25}$$

$$x_{(k+1)T_s} = F_3 x_{(k+d_k)T_s + \phi_k} \tag{2.26}$$

Substituting  $x_{(k+d_k)T_s}$  from (2.24) into (2.25) and  $x_{(k+d_k)T_s+\phi_k}$  from (2.25) into (2.26),

$$x_{(k+1)T_s} = F_3 F_2 F_1 x_{kT_s} + F_3 F_2 G_1 + F_3 G_2$$

(2.27)

#### **2.2.3** Equation for $\phi$

Fig. 2-4 shows that while the  $t_{on}$  interval  $(dT_s)$  is a known quantity (at least for open-loop case), the  $\phi$  interval is as yet unknown and depends in general on both the length of the  $t_{on}$  interval and other circuit parameters, and how deep in discontinuous or continuous conduction mode the converter is operating. Hence, determining this unknown quantity  $\phi$  becomes an exigent problem. Unlike [9] however, the equation solving for  $\phi$  is implicit and can be derived using the eigenvalue and corresponding eigenvector matrix of A(0). Multiplying (2.25) by a matrix  $C = \begin{bmatrix} 1 & 0 \end{bmatrix}$  to obtain the inductor current which goes

to zero at the end of the  $\phi$  interval, the following equation is obtained:

$$Cx_{(k+d_k)T_s+\phi_k} = \begin{bmatrix} 1 & 0 \end{bmatrix} \begin{bmatrix} i_{L_{(k+d_k)T_s+\phi_k}} \\ v_{c_{(k+d_k)T_s+\phi_k}} \end{bmatrix} = i_{L_{(k+d_k)T_s+\phi_k}} = 0$$

Substituting (2.18, 2.19) in above equation, gives

$$Ce^{A(0)\phi_k}x_{(k+d_k)T_s} + C(e^{A(0)\phi_k} - I)A(0)^{-1}B(0) = 0$$

(2.28)

Using the eigenvector and eigenvalue decomposition of A(0) with T denoting the eigenvector matrix and  $\Lambda$ denoting the diagonal eigenvalue matrix, the following equation is obtained,

$$A(0)T = T\Lambda$$

from which

$$A(0) = T\Lambda T^{-1}$$

matrix exponential  $e^{A(0)\phi_k}$  is now given by [10]:

$$e^{A(0)\phi_k} = Te^{\Lambda\phi_k}T^{-1}$$

then (2.28) becomes

$$(CT)e^{\Lambda\phi_k}(T^{-1}x_{(k+d_k)T_s}) + (CT)e^{\Lambda\phi_k}\Lambda^{-1}T^{-1}B(0) - (CT)\Lambda^{-1}T^{-1}B(0) = 0$$

(2.29)

If the eigenvalues of A(0) are  $\lambda_1$ ,  $\lambda_2$ , (2.29) can be simplified as follows:

$$(CT)\begin{bmatrix} e^{\lambda_1\phi_k} & 0 \\ 0 & e^{\lambda_2\phi_k} \end{bmatrix} \begin{bmatrix} T^{-1}x_{(k+d_k)T_s} + \Lambda^{-1}T^{-1}B(0) \end{bmatrix} = (CT)\Lambda^{-1}T^{-1}B(0) \Longrightarrow$$

$$\left(\begin{array}{ccc} t_{11} & t_{12} \end{array}\right) \left[\begin{array}{ccc} e^{\lambda_{1}\phi_{k}} & 0 \\ 0 & e^{\lambda_{2}\phi_{k}} \end{array}\right] \left[\begin{array}{ccc} \frac{t_{22}}{\Delta} i_{L_{(k+d_{k})T_{s}}} - \frac{t_{12}}{\Delta} v_{c_{(k+d_{k})T_{s}}} + B_{11}(0) \frac{t_{22}}{\lambda_{1}\Delta} \\ - \frac{t_{21}}{\Delta} i_{L_{(k+d_{k})T_{s}}} + \frac{t_{11}}{\Delta} v_{c_{(k+d_{k})T_{s}}} - B_{11}(0) \frac{t_{21}}{\lambda_{2}\Delta} \end{array}\right]$$

$$= \left(\begin{array}{ccc} t_{11} & t_{12} \end{array}\right) \left[\begin{array}{ccc} B_{11}(0) \frac{t_{22}}{\lambda_{1}\Delta} \\ - B_{11}(0) \frac{t_{21}}{\lambda_{2}\Delta} \end{array}\right] \Longrightarrow$$

$$\begin{array}{c} \left(\begin{array}{c} t_{11} & t_{12} \end{array}\right) \left[\begin{array}{c} e^{\lambda_{1}\phi_{k}} (\frac{t_{22}}{\Delta}i_{L_{(k+d_{k})T_{s}}} - \frac{t_{12}}{\Delta}v_{c_{(k+d_{k})T_{s}}} + B_{11}(0)\frac{t_{22}}{\lambda_{1}\Delta}) \\ e^{\lambda_{2}\phi_{k}} (-\frac{t_{21}}{\Delta}i_{L_{(k+d_{k})T_{s}}} + \frac{t_{11}}{\Delta}v_{c_{(k+d_{k})T_{s}}} - B_{11}(0)\frac{t_{21}}{\lambda_{2}\Delta}) \end{array}\right] \\ = B_{11}(0) \left[\frac{t_{11}t_{22}}{\lambda_{1}\Delta} - \frac{t_{12}t_{21}}{\lambda_{2}\Delta}\right] \Longrightarrow \end{array}$$

$$\alpha_1 e^{\lambda_1 \phi_k} + \alpha_2 e^{\lambda_2 \phi_k} = \alpha_3 \tag{2.30}$$

where

$$\alpha_1 = t_{11} \left( \frac{t_{22}}{\lambda_1} B_{11}(0) + t_{22} i_{L_{(k+d_k)T_s}} - t_{12} v_{c_{(k+d_k)T_s}} \right)$$

(2.31)

$$\alpha_2 = -t_{12} \left( \frac{t_{21}}{\lambda_2} B_{11}(0) + t_{21} i_{L_{(k+d_k)T_s}} - t_{11} v_{c_{(k+d_k)T_s}} \right)$$

(2.32)

$$\alpha_3 = B_{11}(0)\left(\frac{t_{11}t_{22}}{\lambda_1} - \frac{t_{12}t_{21}}{\lambda_2}\right) \tag{2.33}$$

In (2.31,2.32,2.33),  $t_{ij}$  are the elements of the eigenvector matrix T of A(0) and  $i_{L_{(k+d_k)T_s}}$ ,  $v_{c_{(k+d_k)T_s}}$  are the inductor current and capacitor voltage when the switch is opened and are obtainable from (2.24).

#### 2.2.4 Newton-Raphson method to compute $\phi$

It can be seen from (2.30) that  $\phi_k$  involves an exponential function and depends on previous state variables. To solve this equation, one of the most widely used methods of all root-locating formulas, the Newton-Raphson method from the Taylor series expansion [11] is used. This method is quadratically convergent. The root estimate is based on a