# Boosting Performance of Transactional Memory through Transactional Read Tracking and Set Associative Locks

By

Amir Ghanbari Bavarsad

A Thesis submitted in partial fulfillment of the requirements of

The Msc. Eng. Degree in

**Electrical and Computer Engineering**

Faculty of Engineering

Lakehead University

Thunder Bay, Ontario

ProQuest Number: 10611955

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10611955

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

# All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346 Thunder Bay, Ontario, Canada April 2013

#### **ABSTRACT**

Multi-core processors have become so prevalent in server, desktop, and even embedded systems that they are considered the norm for modern computing systems. The trend is likely toward many-core processors with many more than just 2, 4, or 8 cores per CPU. To benefit from the increasing number of cores per chip, application developers have to develop parallel programs [1]. Traditional lock-based programming is too difficult and error prone for most of programmers and is the domain of experts. Deadlock, race, and other synchronization bugs are some of the challenges of lock-based programming. To make parallel programming mainstream, it is necessary to adapt parallel programming by the majority of programmers and not just experts, and thus simplifying parallel programming has become an important challenge.

Transactional Memory (TM) is a promising programming model for managing concurrent accesses to the shared memory locations. Transactional memory allows a programmer to specify a section of a code to be "transactional", and the underlying system guarantees atomic execution of the code. This simplifies parallel programming and reduces the possibility of synchronization bugs.

This thesis develops several software- and hardware-based techniques to improve performance of existing transactional memory systems. The first technique is Transactional Read Tracking (TRT). TRT is a software-based approach that employs a locking mechanism for transactional read and write operations. The performance of TRT depends on memory access patterns of applications. In some cases, TRT falls behind the baseline scheme. To further improve performance of TRT, we introduce two hybrid methods that dynamically switches between TRT and the baseline scheme based on applications' behavior.

The second optimization technique is Set Associative Lock (SAL). Memory locations are mapped to a lock table in order to synchronize accesses to the shared memory locations. Direct mapped lock tables usually result in collision which leads to false aborts. In SAL, we increase associativity of the lock table to reduce false abort. While SAL improves performance in most of the applications, in some cases, it increases execution time due to overhead of lock tables in software. To cope with this problem, we propose Hardware-SAL (HW-SAL) which moves the set associative lock table to the hardware. As such, true power of set associativity will be harnessed without sacrificing performance.

## **ACKNOWLEDGEMENTS**

I would first like to thank my advisor Professor Ehsan Atoofian for taking me on as a student in the fall of 2011 and provided funding for my research. His hands off advising style was a perfect fit that allowed me to pursue what I found interesting.

I could not have succeeded without the support of my family and friends. Thanks to my parents for supporting my decision to pursue this degree. Also I would like to thank my lab-mates with which I had interesting discussions, whether it was related to research or if it was just something to pass the time.

# **TABLE OF CONTENTS**

| ABSTRAC     | Гiii                                   |

|-------------|----------------------------------------|

| ACKNOWI     | LEDGEMENTSiv                           |

| TABLE OF    | CONTENTSv                              |

| LIST OF FIG | GURESviii                              |

| LIST OF TA  | ABLESx                                 |

| Chapter 1   | Introduction                           |

| 1.1 Ch      | allenges in Programming for CMPs       |

| 1.1.1       | Fine-grained Locking                   |

| 1.1.2       | Coarse-grained Locking                 |

| 1.2 Tra     | nsactional Memory                      |

| 1.3 The     | esis Contributions                     |

| 1.3.1       | Transactional Read Tracking (TRT)      |

| 1.3.2       | Hardware Set Associative Lock (HW-SAL) |

| 1.4 The     | esis Organization                      |

| Chapter 2   | Background and Related Work            |

| 2.1 Mu      | ltiprocessor Architectures             |

| 2.2 Cha     | Illenges in Parallel Programming       |

| 2.3 Ato     | mic Primitives9                        |

| 2.3.1       | Compare and Swap9                      |

| 2.3.2       | Load-locked, Store-conditional         |

| 2.4 Trai    | nsactional Memory (TM)                 |

| 2.5 Rela    | ated Work                              |

| 2.5.1       | Transactional Locking II (TL2)         |

| 2.5.2       | Programming with TL2                   |

| 2.5     | 3.3  | Benchmarks                                         | . 23 |

|---------|------|----------------------------------------------------|------|

| 2.6     | Sui  | mmary                                              | . 23 |

| Chapter | 3    | Transactional Read Tracking                        | . 24 |

| 3.1     | Mo   | otivation                                          | . 24 |

| 3.2     | Tra  | insactional Read Tracking                          | . 25 |

| 3.2     | .1   | Proof of Correctness:                              | . 26 |

| 3.3     | Per  | formance of TRT                                    | . 28 |

| 3.4     | rw   | Conflict Based GV4-TRT (RGVT)                      | . 29 |

| 3.4     | .1   | Read-Write Conflict                                | . 30 |

| 3.4     | .2   | Performance of RGVT                                | . 30 |

| 3.5     | Per  | ceptron GV4-TRT (PGVT)                             | . 32 |

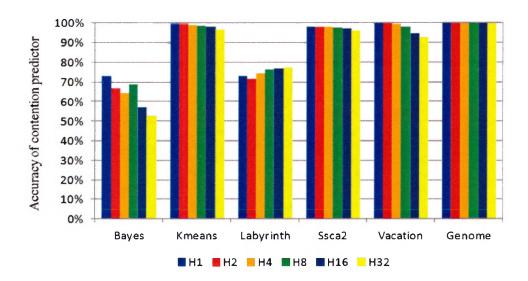

| 3.5     | .1   | Accuracy of contention predictors                  | . 35 |

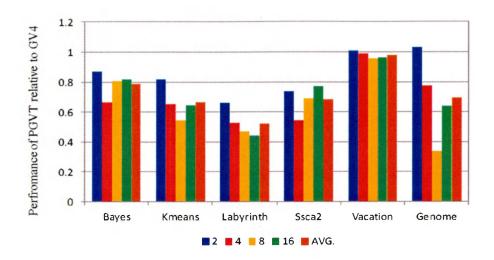

| 3.5     | .2   | Performance of PGVT                                | . 36 |

| 3.6     | Sur  | nmary                                              | . 37 |

| Chapter | 4    | Hardware Support for Set Associative Lock (HW-SAL) | . 39 |

| 4.1     | Mo   | tivation                                           | . 39 |

| 4.2     | Ger  | m5 Simulator                                       | 40   |

| 4.3     | Set  | Associative Locks                                  | 41   |

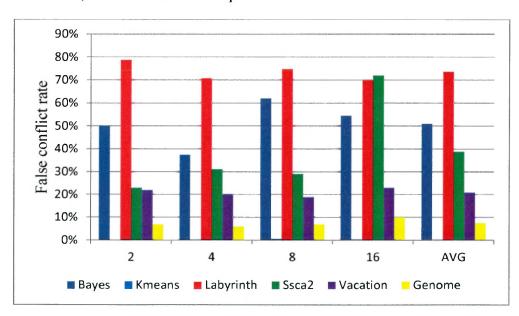

| 4.3.    | .1   | Frequency of False Conflicts                       | 42   |

| 4.3.    | 2    | SW-SAL                                             | 43   |

| 4.3.    | 3    | SW-SAL Performance                                 | 45   |

| 4.4     | Har  | dware SAL (HW-SAL)                                 | 47   |

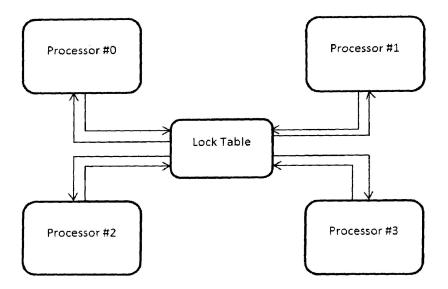

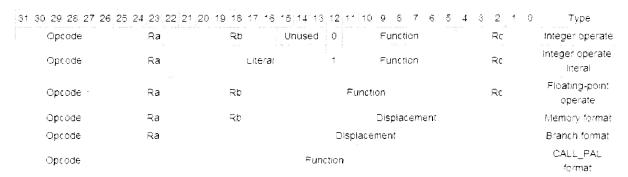

| 4.4.    | 1    | ISA Augmentation                                   | 48   |

| 4.4.    | 2    | HW-SAL in Gem5                                     | 50   |

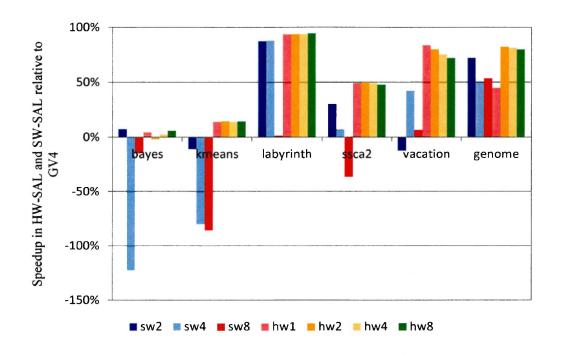

| 4.5     | Dorf | Formance Evaluation                                | 50   |

| 4.6 S      | Summary      | 53 |

|------------|--------------|----|

| Chapter 5  | Conclusions  | 54 |

| 5.1 F      | Future Work  | 55 |

| Appendix A | A            | 56 |

| Appendix I | В            | 71 |

| Chapter 6  | Bibliography | 76 |

# LIST OF FIGURES

| Figure 1.1 (a) Fine-grained and (b) coarse-grained lock-version of Sieve of Eratosthenes | 3    |

|------------------------------------------------------------------------------------------|------|

| Figure 1.2 TM-version of Sieve of Eratosthenes.                                          | 4    |

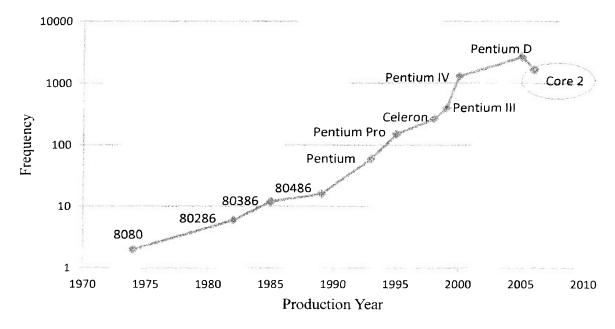

| Figure 2.1 Clock frequency of different Intel processors over the years.                 | 8    |

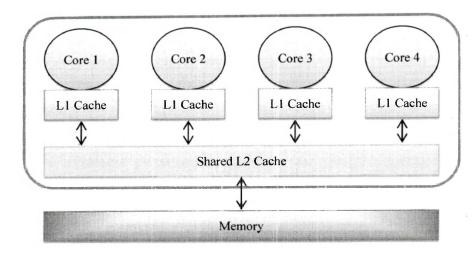

| Figure 2.2 Architecture of a CMP.                                                        | 9    |

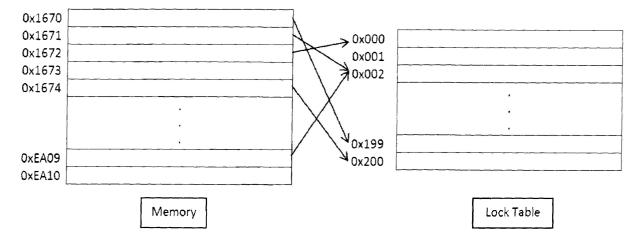

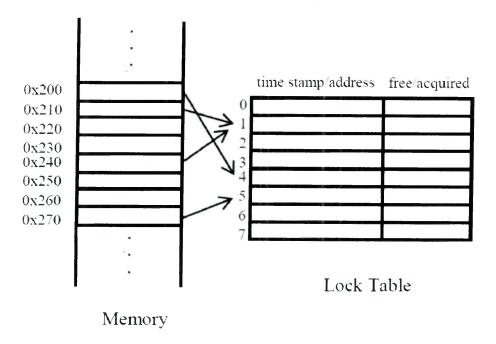

| Figure 2.3 Lock table in TL2                                                             | 18   |

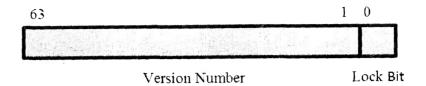

| Figure 2.4 Structure of an entry of the lock table.                                      | 19   |

| Figure 2.5 Pseudo code for Eager GV4.                                                    | 19   |

| Figure 2.6 Pseudo code for Lazy GV4.                                                     | 20   |

| Figure 2.7 A sample code using transactional memory for implementation of a counter      | 22   |

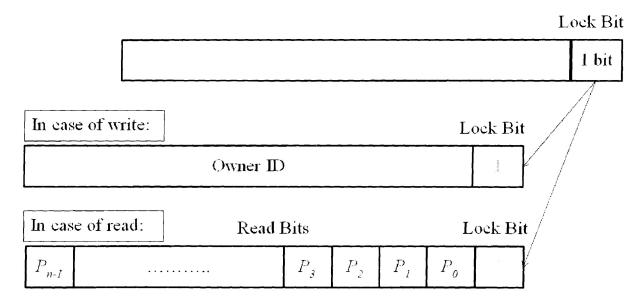

| Figure 3.1 Structure of a single lock entry in TRT.                                      | 25   |

| Figure 3.2 Pseudo code for TRT.                                                          | 27   |

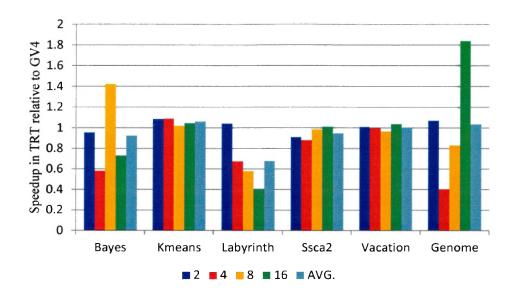

| Figure 3.3 Speedup in TRT relative to GV4.                                               | 29   |

| Figure 3.4 Part of Genome program from STAMP v0.9.10 benchmark suite.                    | 29   |

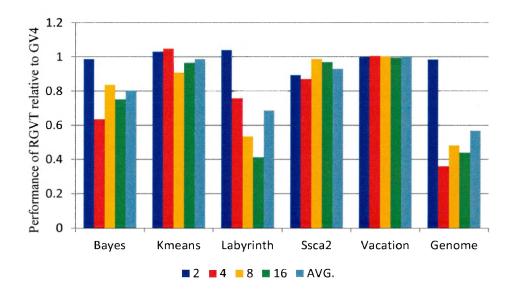

| Figure 3.5 Performance of RGVT using rwConflict.                                         | 31   |

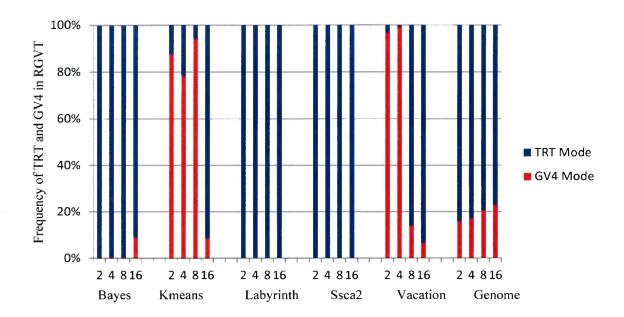

| Figure 3.6 Frequency of GV4 and TRT in RGVT.                                             | 32   |

| Figure 3.7 Weight vector and input vector in a perceptron                                | 33   |

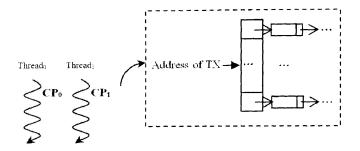

| Figure 3.8 A program with two threads and two local contention predictors                | 34   |

| Figure 3.9 Adaptive algorithm.                                                           | 34   |

| Figure 3.10 Lookup and update in a perceptron predictor                                  | 35   |

| Figure 3.11 Accuracy of contention predictors with variable history lengths              | 36   |

| Figure 3.12 Performance of PGVT relative to GV4.                                         | 37   |

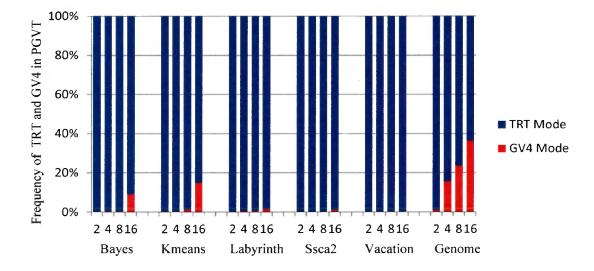

| Figure 3.13 Frequency of GV4 and TRT in PGVT                                             | . 37 |

| Figure 4.1 Memory address space is mapped to a lock table in TL2.                        | . 41 |

| Figure 4.2 False conflicts in STAMP benchmarks                                           | . 42 |

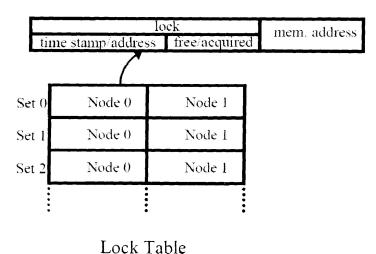

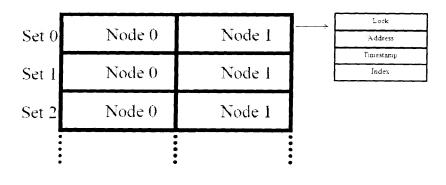

| Figure 4.3 Structure of the lock table in a 2-way SAL                                    | . 44 |

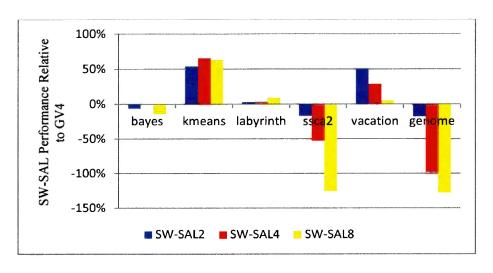

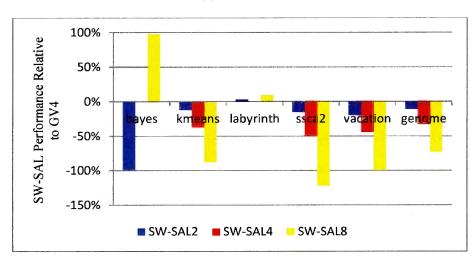

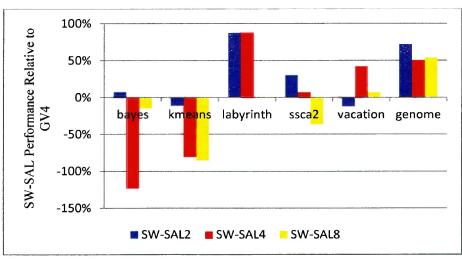

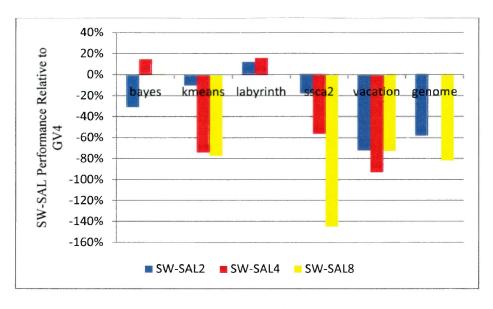

| Figure 4.4 Performance improvements in SW-SAL relative to the baseline scheme            | . 47 |

| Figure 4.5 Structure of the lock table in HW-SAL.                                        | . 48 |

| Figure 4.6 A HW-SAL with four cores.                                                     | . 49 |

| Figure 4.7 Instruction format in Alpha architecture                                      | 10   |

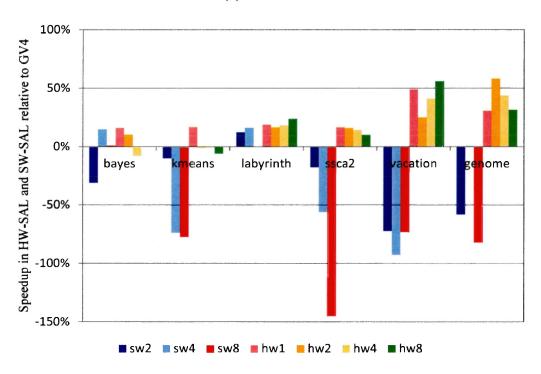

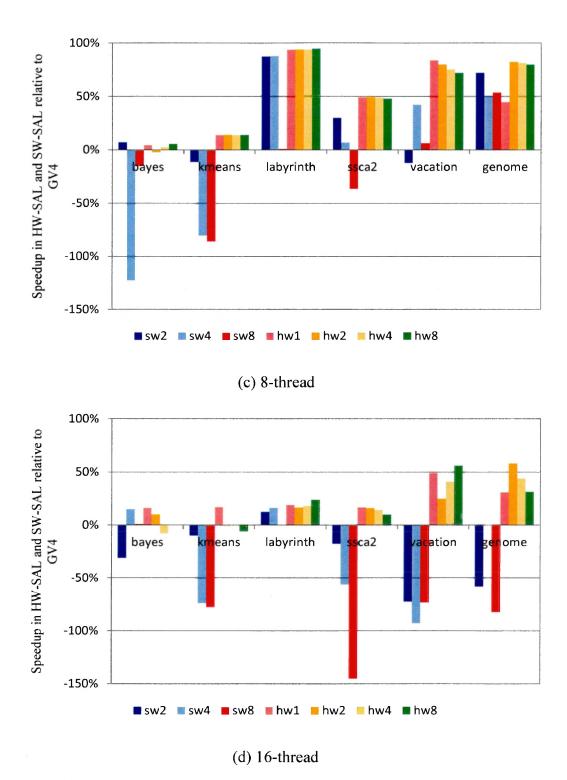

| Figure 4.8 | SW-SAL | and HW-SAL | speedup. | (a) | 2-thread. | (b) | 4-thread. | (c) | 8-thread. | (d) | 16-  |

|------------|--------|------------|----------|-----|-----------|-----|-----------|-----|-----------|-----|------|

| thread     |        |            |          |     |           |     |           |     |           |     | . 52 |

# LIST OF TABLES

| TABLE 3.1 Input arguments for STAMP benchmarks    | . 28 |

|---------------------------------------------------|------|

| TABLE 4.1 Configuration of the processors in Gem5 | . 45 |

# Chapter 1 Introduction

The computing industry has been trying to keep up with Moore's law [2] for almost half a century. Processors have become smaller and faster as Moore had predicted; however, limitations such as sub-threshold leakage [3] and other physical constrains in single-core processors [4] have forced manufacturers to shift their focus from designing complex single-core processors with higher frequency towards utilizing several simpler cores in a chip to boost performance and gain more processing power. As such, major chip manufacturers have shifted towards Chip Multiprocessors (CMPs) since 2000. A CMP provides several processing cores on the same die, increasing the total processing power. At the same time, the design complexity is reduced by using the same design for different cores. IBM was the first to release a commercial CMP: the POWER4 [5] which was followed by Intel [6] and AMD [7].

CMPs by IBM, Intel, AMD, and ARM made CMPs almost ubiquitous in most computing devices, ranging from workstations to mobile devices and tablets. One of the challenges in CMPs is that existing sequential programs are unable to utilize all the resources offered by CMPs, since the parallelism must be declared explicitly in the code and the legacy sequential programs were not designed with that concept in mind. This has led to creation of a demand for new programming methodologies to harness the ever-increasing computational power of CMPs.

## 1.1 Challenges in Programming for CMPs

Synchronization plays a pivotal role in parallel programming. Different threads of execution need to have a consistent view of the shared data; otherwise, the program would run into synchronization bugs such as deadlock, priority inversion and starvation [8]. Conventional parallel programming using locks allows a programmer to synchronize accesses to the shared data.

There are two types of locking mechanisms to ensure atomicity of parallel programs: Finegrained locking and coarse-grained locking. In the next section we present these two types of locks and provide examples.

## 1.1.1 Fine-grained Locking

In fine-grained locking, in order to synchronize accesses to an object, we split the object into independently synchronized components, ensuring that at any moment at most one thread accesses each of those components. The problem with fine-grained locking is its complexity.

Figure 1.1 (a) shows a program for parallel version of "Sieve of Eratosthenes" using fine-grained locks. Sieve of Eratosthenes is an algorithm that finds prime numbers up to a certain limit. In this example, the limit is set to 100. Each entry in array A[] corresponds to a number. By the end of the program, if an entry is true, the corresponding number is a prime number; otherwise, it is a composite number. The whole array is divided among processors. Each processor goes through its share of the array and determines whether the corresponding numbers are prime numbers or not. In fine-grained locking, each entry of the array has to be protected by a lock. Before accessing the entry, lock is acquired. After processing the entry, the lock is released.

#### 1.1.2 Coarse-grained Locking

In coarse-grained locking, we take a sequential implementation of an object, add a lock field, and ensure that each access to the shared object acquires and releases the lock. The problem with coarse-grained locking is its lack of scalability. Coarse-grained synchronization works well when concurrency level is low. However, if too many threads try to access the same object at the same time, then the object becomes a bottleneck, forcing threads to execute serially. Figure 1.1 (b) shows a program for parallel version of "Sieve of Eratosthenes" using coarse-grained locks. In coarse-grained locking, the critical section where the array is being accessed is protected by a single lock. Each thread needs to acquire the lock before it could access that part of the code. This reduces the concurrency, since only one thread could have exclusive access to the critical section at a time. On the other side, in fine-grained lock, each entry of the array is protected by a separate lock. As such, threads that access different entries of the array can run simultaneously. This increases concurrency level in the fine-grained lock programs.

The ever-increasing presence of CMPs in different areas of computing dictates the need for a system to provide a scalable, easy to program, and high performance mechanism for programmers in order to handle complexity of synchronization in their applications. This would make parallel programming mainstream, enabling average programmers write efficient and bug-

free parallel programs. One such method that provides all the aforementioned attributes in highly abstract level is Transactional Memory (TM).

```

//Let A be an array of Booleans initially set

//Let A be an array of Booleans initially set

//to true

//to true

bool A [100];

bool A [100];

mutex lock;

mutex locks[100];

void* thread programs(int threadID)

void* thread programs(int threadID)

for (int i = 0; i<10; i+=threadID)

for (int i = 0; i<10; i+=threadID)

if (A[i] == true)

mutex lock(lock);

if (A[i] == true)

for (int j = i^2; j < n; i+=i)

for (int j = i^2; j < n; j+=i)

mutex lock(lock[j]);

A[j] = false;

A[j] = false;

mutex unlock(lock[i]);

mutex unlock(lock);

(a) Fine-grained lock

(b) Coarse-grained lock

```

Figure 1.1 (a) Fine-grained and (b) coarse-grained lock-version of Sieve of Eratosthenes.

#### 1.2 Transactional Memory

Transactional memory (TM) [9] is a new parallel programming model which is viewed by many as a replacement for lock-based programming. In TM, programmers mark sections of programs that access shared data as transactions and the underlying system ensures correct execution of the programs. Non-conflicting transactions execute in parallel and those transactions that conflict are aborted and restarted without the programmer having to worry about issues such as deadlock. Transactions are atomic [9]: each transaction either commits or aborts (its effects are discarded). Transactions are linearizable [9]: each committing transaction takes effect instantaneously at some point between start and end of the transaction.

Figure 1.2 shows the TM version of Sieve of Eratosthenes. Contrary to the lock versions, in transactional memory version of the program, only the critical section is defined using TM BEGIN and TM END and the programmer does not need to deal with the complexity of

locks and synchronization. If two transactions access an element of the array simultaneously, then the underlying system aborts and restarts one of the two transactions. As such, a programmer does not need to deal with synchronization of threads.

```

//Let A be an array of Booleans initially set

//to true

bool A [100];

void* thread_programs(int threadID)

{

for (int i = 0; i<10; i+=threadID)

{

if (A[i] == true)

{

for (int j = i^2; j < n; j+=i)

{

TM_BEGIN();

A[j] = false;

TM_END();

}

}

}

}

```

Figure 1.2 TM-version of Sieve of Eratosthenes.

TM provides several semantics for the programmers in order to make the synchronization of the code more abstract. These semantics are as follow:

- 1. Critical sections represented by transactions are atomic; they either successfully complete or abort.

- 2. Transactions are isolated and outside of transactions cannot see interim updates,

- 3. Transactions are placed in the code and there is no need to protect them with data types such as locks in an explicit manner by the programmers.

Transactional memory theoretically allows a programmer to concentrate more on defining where the critical sections should be in a coarse grained manner, but not have to worry about scalability and atomicity. The underlying system would guarantee those properties.

Transactional memory comes with three variants: Hardware Transactional Memory (HTM) [10] [11], Software Transactional Memory (STM) [12] [13], or Hybrid Transactional Memory [14]. Hardware Transactional Memory (HTM) exploits transactional caches to hold speculative data, track ownership of shared data, and detect conflicts among transactions. While HTM makes transactional memory fast, it increases hardware complexity and is not flexible. In addition, both

HTM and hybrid approaches require new features in hardware which do not exist in current processors, i.e. transactional cache. STM, however, can use available features of current processors and comes with fewer intrinsic limitations imposed by hardware structures, such as buffer size and caches. The downside of STM is that it is not as fast as HTM.

All Transactional Memory systems should offer some sort of non-blocking behaviour. A non-blocking behaviour guarantees that the threads that are contending for a shared resource do not have their execution postponed indefinitely. There are several forms of non-blocking behaviour:

- Wait-freedom [15]: is the strongest non-blocking guarantee of progress. An algorithm is wait-free if every operation has a limit on the number of steps the algorithm will take before the operation completes. This property is critical for real-time systems as long as the performance cost is not too high.

- Lock-freedom [16]: allows individual threads to starve but guarantees the system-wide progress. An algorithm is considered lock-free when the threads run sufficiently long enough that at least one of them makes progress. All wait-free algorithms are lock-free.

- Obstruction-freedom [17]: is possibly the weakest natural non-blocking progress guarantee. An algorithm is obstruction-free if at any point, a single thread executed in isolation (i.e., with all obstructing threads suspended) for a limited number of steps will complete its operation. All lock-free algorithms are obstruction-free.

#### 1.3 Thesis Contributions

This thesis proposes two optimization techniques for STMs: Transactional Read Tracking (TRT) and Hardware Set Associative Lock (HW-SAL).

#### 1.3.1 Transactional Read Tracking (TRT)

Current state of the art STM uses a global clock as a timestamp in order to maintain consistency among transactions. This causes contention over the global clock and dramatically impedes scalability, especially when the number of concurrent threads increases. TRT employs a distributed method that alleviates the need for the global clock, and so improves scalability and performance.

Although an effective method, TRT proves to be slower than baseline scheme, depending on the data access patterns of the benchmarks. A natural question would be whether the different advantages of TRT and its counterpart could be combined to gain maximum speed up. We propose two adaptive methods that combine both techniques in order to avoid the shortcomings of each of the techniques and gain benefits of the two.

#### 1.3.2 Hardware Set Associative Lock (HW-SAL)

In most recent STM systems, memory addresses are mapped to a lock table using a hash functions. Hash collision is an intrinsic property of a direct mapped lock table which would cause false conflicts. False conflict happens when two memory locations are mapped to the same entry of the lock table. An STM considers false conflict as memory conflict; whereas there is no actual conflict. False conflict reduces the concurrency of the STM systems. One way to circumvent this problem is using a set associative lock table. Much like a set associative cache, each entry of the lock table consists of several nodes. When an address is mapped to an entry, all nodes are searched for the address. As such, the probability of false conflict is reduced. However, implementation of SAL in software results in overhead which degrades performance in some of the benchmarks especially when associativity of the lock table increases.

The final contribution of this thesis is hardware support for SAL. In this work, we propose to move the lock table from software to hardware which in turn makes the lookup process fast and improves performance of SAL. There is a single hardware unit which contains the lock table and each processor can access the table. A programmer uses a set of new instructions provided by processors to access the table.

#### 1.4 Thesis Organization

The rest of this thesis is organized as follows. In chapter 2, we explain the basic concepts of multiprocessor architecture and discuss transactional memory. We explain details of Transaction Locking II (TL2) as an example of state of the art STM. We also discuss related work in this chapter. In Chapter 3, we cover the motivation behind "Transactional Read Tracking" and explain details of implementations. Chapter 4 covers the "Set Associative Lock" and presents the "Hardware Support for SAL". Finally in chapter 5, we will offer the concluding remarks and future work for this thesis.

# Chapter 2 Background and Related Work

In this chapter, we discuss architecture of CMPs and explain TM systems. In section 2.1, we review multiprocessor architectures. In section 2.2, we review the challenges that exist in programming for CMPs. Section 2.3 presents a brief overview of primitives provided by multiprocessors for parallel programming. In section 2.4, we explain Transactional Memory as a promising programming model for multiprocessor architectures. In section 2.5, we provide an overview of the related work to this thesis. We also describe details of TL2 as a state of the art STM in this section. Finally, in section 2.6, we will conclude this chapter with discussion on challenges of existing STMs.

# 2.1 Multiprocessor Architectures

The computing industry has gone into a drastic change since the early 2000's. Before 2000, chip manufacturers dedicated all transistors on a chip to a single-core processor. In each generation, the performance of processors was improved by increasing clock frequency. However, overheating and sub-threshold leakage [3] limits clock frequency. Therefore, chip manufacturers have shifted their focus to "multicore" architectures, where multiple cores are integrated on the same die. Figure 2.1 depicts the shift from single-core processors to multicore processors. As the figure shows, the clock frequency of the single core processors has increased rapidly until early 2000. Then, the rate at which performance increased diminished. Starting in 2005, the clock frequency was slightly reduced. This time marks the advent of multiprocessors. The manufacturers designed simpler processors with more core units, to provide parallelism.

The introduction of chip multiprocessors has changed the way we develop software. In single-core processors, increasing clock frequency results in reduction in execution time of programs and so programs were executed faster without any effort by the programmers. However, this trend in CMPs results in slow-down of programs since clock frequency of CMPs is reduced due to power budget.

Figure 2.2 shows architecture of a CMP with four cores. Each core executes an independent thread. One way to boost performance of applications in CMPs is parallel programming. A parallel program is composed of several threads and the threads are executed concurrently on a

CMP's cores. It is up to a programmer to utilize processor cores and harness computational power of the underlying hardware.

# 2.2 Challenges in Parallel Programming

Parallel programming introduces new challenges to programmers. As mentioned in Chapter 1, thread synchronization is one of the main concerns in parallel programming. Conventional constructs for synchronization such as locks and monitors are complicated and error-prone. Common problems associated with the conventional locking techniques are:

- **Priority inversion** [8]: occurs when a lower priority process is pre-empted while holding a lock needed by a higher-priority process.

- Convoying [8]: occurs when a process holding a lock is rescheduled, perhaps by exhausting its scheduling quantum time, by a page fault, or by some other kind of interrupt. When such an interruption occurs, other processes capable of running maybe unable to progress.

- **Deadlock** [8]: can occur if processes attempt to lock the same set of objects in different orders. Deadlock avoidance can be awkward if processes must lock multiple data objects, particularly if the set of objects is not known in advance.

In the next section, we review atomic primitives used in conventional lock-based parallel programs.

Figure 2.1 Clock frequency of different Intel processors over the years.

Figure 2.2 Architecture of a CMP.

#### 2.3 Atomic Primitives

There has been extensive debate over the years on what primitives should be provided to support synchronization [18]. Some researchers have proposed that the user level synchronization operations, such as locks and barriers, should be supported at the machine level; meaning that the synchronization "algorithm" itself should be implemented in hardware [18]. As such, the system provides extensive hardware support which would make synchronization fast but not flexible. On the other side, software support would have the advantage of flexibility but it is slower than hardware primitives [18].

All practical synchronization operations rely on some sort of variation of atomic read-modify-write primitive. In this primitive, the value of a memory location is read, modified and written back atomically without intervening accesses to that location by other processors. Different synchronization algorithms can be built using this primitive. In the rest of this section, we discuss two variations of read-modify-write primitive.

#### 2.3.1 Compare and Swap

Compare and Swap (CAS) operation takes three arguments: an address "a" in memory, an expected value "e", and an updated value "v". It atomically executes the following steps:

• If the memory at address "a" contains the expected value "e", then write the new value "v" to that address and return the expected value, indicating successful CAS instruction.

• Otherwise leave the memory unchanged and return the value contained in the memory at address "a", indicating failure of CAS instruction.

IBM 370 [18] was one of the first architectures to support a sophisticated atomic instruction, the *compare-and-swap* instruction [18]. This instruction supports synchronization for parallel programming on uniprocessor or multiprocessor systems. The *compare-and-swap* (CAS) instruction is now supported in many modern architectures such as AMD, Intel, and Sun. On Intel and AMD architectures, it is called CMPXCHG (compare and exchange) [19], while on SPARC<sup>TM</sup> it is called CAS [20].

The CAS instruction has one pitfall. Perhaps the most common use of CAS is the following. An application reads the value "a" from a given memory address, and computes a new value "c" for that location. It intends to store "c", but only if the value "a" in the address has not been changed since it was read. One might think that applying a CAS with expected value "a" and updated value "c" would accomplish this goal. There is a problem: another thread could have overwritten the value "a" with another value "b", and later write "a" again to the address. The CAS operation will replace "a" with "c", but the application may not have done what it was intended to do (for example, if the address stores a pointer, the new value "a" may be the address of a recycled object). This problem is referred to as ABA problem [8].

#### 2.3.2 Load-locked, Store-conditional

Some multiprocessors provide a pair of instructions called load-locked and store-conditional [18] to implement atomic operations, instead of atomic read-modify-write instructions such as compare and swap. The first instruction is commonly called *load-locked* or *load-linked* (LL). It loads a memory location into a register. It may be followed by any number of arbitrary instructions that modify the value in the register. Then the instruction *store-conditional* (SC) is called. It writes the register back to the memory location if and only if no other processor has written to that memory location since this processor completed its LL.

The LL/SC instruction is supported by a number of modern architectures: Alpha AXP (ldl\_l/stl\_c) [21], IBM PowerPC (lwarx/stwcx) [5] MIPS ll/sc, and ARM (ldrex/strex) [22]. LL/SC does not suffer from the ABA problem, but in practice there are often severe restrictions on what a thread can do between a LL and the matching SC. A context switch, another LL, or another load or store instruction may cause the SC to fail.

# 2.4 Transactional Memory (TM)

Transactional Memory (TM) was proposed to simplify parallel programming and improve scalability of programs. Software Transactional Memory (STM) has been a convenient way of providing necessary constructs for transactional programming. STMs do not require any modifications in hardware and are available to the programmers through a runtime or compile-time library.

In TM systems, conflict and version management are the two important aspects of the system design. Conflict management deals with when conflicts are detected, how they are detected and which actions should be taken to address them. Version management deals with where and how the transactional data are kept.

There are two policies for conflict management: *Eager* and *Lazy*. In eager policy, a TM system constantly monitors the transactional execution; as soon as it detects a conflict, it decides which transaction should be aborted. In this method, since the conflicts are detected at the earliest possible time, the wasted work due to aborted transactions is minimized. On the other side, lazy conflict management defers detection of conflicts until the end of transactions. At that point, the transaction checks all memory locations that are read or written in the transactional section. If another transaction has changed one or more of these memory locations, conflict happens and one of the two transactions should be aborted. Lazy conflict management can lead to wasted work, since a transaction is only aborted at the end of its execution. However, Tomic et al. [23] observed that it can allow more parallelism than eager policy.

There are also two main classes of version management policies in TMs: eager and lazy. Eager policy keeps new (speculative) values in-place (in the memory hierarchy) and holds pre-transactional values somewhere else. Most of TMs buffer the old values in a different location in memory, using a software-managed log [24] [25]. On the other hand, lazy policy keeps the old values in the memory hierarchy and holds new values in a log. The new values become visible to other transactions only during commit.

In the next section, we review previous research work in TM.

#### 2.5 Related Work

The concept of Transactional Memory was first introduced by Herlihy and Moss [9]; the basic idea was to group shared-memory operations into atomic transactions. They changed cache coherence protocol in multiprocessors to support TM in hardware. A transactional cache accommodates speculative data generated by transactions. When a transaction successfully commits, the content of the transactional cache is written into the main memory. The transactional cache is able to snoop memory operations on the bus from other processors. As such, it can determine if another processor is trying to gain exclusive access to a cache line which is currently obtained by a local transaction; if so, the remote transaction would be aborted. This implies that the protocol is not non-blocking. Starvation is handled in software by backing off in the case of contention. The main disadvantage of this design is that it requires hardware modifications for eache coherency protocols.

Shavit and Touitou [26] proposed a lock-free STM. A notable difference from Herlihy is that they abort contending transactions, instead of recursively helping them; non-blocking behaviour is still guaranteed because aborted transactions help the transaction that aborted them before retrying. Their design only supports static transactions, in which the set of accessed memory locations is known in advance. However, this STM cannot support transactions that access memory locations that are allocated dynamically through operations such as malloc().

To alleviate the problem with static transactional programming, Moir [27] presents a lock-free and wait-free STM design which offers a dynamic transactional support, in contrast with Shavit and Touitou's static interface. The lock-free design divides the transactional memory into fixed-size blocks which form the unit of concurrency. A header array contains a word-size entry for each block in the memory, consisting of a block identifier and a version number. In their design, if two transactions conflict, then one of them aborts. In this scheme, transactions that do not access shared memory locations can execute simultaneously. The design also suffers from the same drawbacks as the conditionally wait-free MCAS [28] on which it builds: bookkeeping space is statically allocated for a fixed-size heap, and the read operation is potentially expensive. Also, the read-set of the transaction has to be validated in order to make sure that it has not been changed since the start of a transaction.

Herlihy et al. [29] have implemented an obstruction-free dynamically sized STM, meaning that memory blocks can be created and destroyed on the fly. Their implementation builds on a readily available form of the CAS primitive. A novel feature of their obstruction-free STM implementation is its use of modular contention managers to ensure progress in practice. Also, the design is disjoint-access-parallel [28]; meaning that processes that access disjoint sets of words in the shared memory, can progress concurrently as long as they do not interfere with each other. These features significantly decrease contentions in many multiprocessor applications.

Dice et al. [12] introduce Transactional Locking II, an STM based on commit-time locking and a novel global clock scheme for validation. Unlike all other STMs, TL2 fits seamlessly with any memory system life-cycle, including those using malloc()/free(). Also, unlike all other lock-based STMs it efficiently avoids periods of unsafe execution, that is, using its novel version-clock validation, user code is guaranteed to operate only on consistent memory states. It uses a table of Locks in order to maintain consistency of transactions. The overall performance improvement is notably higher compared to both lock-based and non-blocking STM systems. Due to aforementioned qualities of TL2, we use this system as a baseline for our optimization techniques.

Spear *et al.* [30] proposed global commit counter to reduce overhead of incremental validation. In invisible read policy, a reader detects read-write conflicts by incrementally validating open objects at the cost of quadratic number of objects. To reduce cost of validation, a global counter records the number of transactions that attempt to commit. When a transaction opens an object, the transaction skips incremental validation if the counter has not changed since the last time the reader checked its objects. As such, costly exhaustive validations can be avoided if transactional write operations happen rarely. However, this method does not distinguish access to different fields of an object and results in unnecessary serialization if transactions access disjoint memory locations.

Mannaeswamy and Govindarajan [31] studied cache behavior of STMs and showed that global clock misses are responsible for up to 38% of transactional misses in Stamp benchmark suite. They proposed a compiler optimization technique, which is called selective partition timestamp (SPTS), to reduce cost of the global clock. SPTS, partitions disjoint instances of data structures and assigns each partition to a separate pool. Each pool has its own local clock and data

structures within a pool compete for the local clock. As such, contention over the central global clock reduces. One of the restrictions of SPTS is that it decides on data structure partitions in compile-time and so needs to use a conservative approach to select candidate shared data structures for partitioning. As an example, if a data structure is passed to an external function, whose source code is not visible to the compiler, the compiler cannot apply SPTS to the data structure.

Riegel *et al.* [32] introduced a mechanism which uses real-time clocks to optimistically synchronize concurrent transactions. They also exploited externally synchronized clocks as the time base for better scalability. Their scheme requires external support and focuses on scalability of time base itself.

Avni and Shavit [13] introduced thread-local clock (TLC) technique to allow transactions to operate on consistent states without the global clock. In TLC, each thread has a local clock which is initialized to zero and is incremented by one at the start of every new transaction. There is also a thread local array that has an entry per thread recording timestamp of the thread. When a transaction commits it writes its thread id and timestamp into the associated lock. To validate read-set, all locks corresponding to the transactional read operations are checked to be unlocked. Then, the timestamp of each lock is checked to make sure that it is less than the associated thread j's entry in the thread local array. If the check fails then thread j's entry in the array is updated with the new timestamp. While TLC eliminates central global clock, it increases abort rate since the new timestamp of a committed transaction is not transferred to other transactions immediately. Instead, other transactions notice the new timestamp when their validations fail. As such, TLC may degrade performance despite of the fact that it eliminates the central clock. In addition, Avni and Shavit evaluated TLC with micro benchmarks which are not representative of real applications.

Atoofian [33] introduced "Set Associative Locks" (SAL) to reduce false aborts in STMs. In time-based STMs, different memory locations might be mapped to the same entry of the lock table. This creates false aborts and degrades performance. Atoofian proposed SAL which increases associativity of the lock table and reduces false aborts.

Many HTM implementations have been proposed since Herlihy and Moss introduced Transactional Memory. Ananian et al. [34] proposed UTM which was the first eager HTM

system that supports unbounded transactions. By placing transactional modifications across the memory hierarchy and storing metadata on the side, it is able to execute transactions of any size.

Hammond et al. [35] proposed a new shared memory model: Transactional memory Coherence and Consistency (TCC). TCC provides a model in which atomic transactions are always the basic unit of parallel work, communication, memory coherence, and memory reference consistency. TCC hardware combines all writes from each transaction region in a program into a single packet and broadcasts this packet to the permanent shared memory states atomically as a large block. This simplifies the coherence hardware because it reduces the need for small, low-latency messages and completely eliminates the need for conventional snoopy cache coherence protocols, as multiple speculatively written versions of a cache line may safely coexist within the system. Meanwhile, automatic, hardware-controlled rollback of speculative transactions resolves any correctness violations that may occur when several processors attempt to read and write the same data simultaneously. The cost of this simplified scheme is higher inter-processor bandwidth.

Chafi et al. [36] proposed Scalable TCC which presents a scalable TM implementation for directory-based distributed shared memory systems. This scheme is live lock free without the need for user-level intervention. The design is a scalable implementation of optimistic concurrency control that supports parallel commits with a two-phase commit protocol. It uses write-back caches and filters coherence messages. The scalable design is based on Transactional Coherence and Consistency (TCC), which supports continuous transactions and fault isolation.

Moore et al. [24] proposed LogTM in order to simplify the version management mechanism by keeping the pre-transactional state in a software-managed log; in case of an abort, the values in the software log will be written back to memory. Also using Read-Write cache bits [37] LogTM is able to eagerly detect conflicts. Yen et al. proposed LogTM-SE [25] in order to decouple the transactional state from caches by summarizing the memory accesses in signatures [38]. LogTM-SE uses signatures to summarize a transaction's read and write-sets and detects conflicts on coherence requests (eager conflict detection). Transactions update memory "in place" after saving the old values in a per-thread memory log (eager version management). Finally, a transaction commits locally by clearing its signature, resetting the log pointer, etc., while aborts must undo the log.

To accelerate the abort recovery and reduce the pressure on the write signature, FASTM [10] implements a hybrid version management mechanism. It takes advantage of the processor's cache hierarchy to provide fast abort recovery. FASTM uses a novel coherence protocol to buffer the transactional modifications in the first level cache and to keep the non-speculative values in the higher levels of the memory hierarchy. This mechanism allows fast abort recovery of transactions that do not overflow the first level cache. FASTM keeps the pre-transactional state in a software-managed log, which permits the eviction of speculative values and enables transparent execution even in the case of cache overflow.

DynTM [11] presents the first fully-flexible HTM system that permits the simultaneous execution of transactions using complementary version and conflict management strategies. DynTM utilizes a novel coherence protocol that allows tracking conflicts among eager and lazy transactions. Both the eager and the lazy execution modes of DynTM exhibit very high performance compared to modern HTM systems. Also, the DynTM lazy execution mode implements local commits, avoiding expensive commit arbitration. In addition, lazy transactions share the majority of hardware support with eager transactions, reducing cost of implementation substantially.

IBM zEC12 [39] is the first general purpose server which incorporates transactional memory. In zEC12, IBM used transactional memory to enable software to better support concurrent operations that use a shared set of data such as financial institutions processing transactions against the same set of accounts. zEC12 exploits up to 120 processing cores, supporting speeds of 5.5 GHz the highest clock speed CPU ever produced for commercial sale [40]. The architecture of the cores is a superscalar out-of-order pipeline with new instruction for transactional memory support.

BlueGene [41] is a supercomputing project that provides an ultra-scale technical computing platform to solve the most challenging problems facing engineers and scientists at faster, more energy efficient, and more reliable rates than ever before. Wang et al. [42] evaluated the performance of transactional memory applications on IBM's BlueGene/Q platform. They first provided a detailed description of the BG/Q HTM implementation and overhead. Then, they presented a thorough examination of parallel benchmarks for TM system on BG/Q. Also, they describe how the best-effort HTM support in BG/Q can be complemented with a software stack

that includes the kernel, the compiler, and the runtime system to deliver the simplicity of a TM programming model.

In this thesis, we use Transaction Locking II (TL2) [12] to evaluate our optimization techniques. It is important to note that although we use TL2 in this thesis, our optimization techniques are general and can be employed in any other time-based STMs [32] [43]. In the next section, we explain details of TL2.

#### 2.5.1 Transactional Locking II (TL2)

Time-based transactional memories exploit a time base to impose order among transactions and reason about consistency of transactional data. In this section, we focus on TL2 as a time-based STM.

TL2 employs a validation scheme, called GV4, which relies on a global clock. The global clock is implemented as a shared counter and is incremented when a transaction commits. In addition, GV4 exploits a table of locks to synchronize accesses to the shared memory locations. The memory addresses are mapped to the locks using a hash function. Figure 2.3 shows the structure of memory and how it is mapped to the lock table entries. Each entry of the lock table has two sections: lock-bit and version number. The size of each entry in the lock table is equal to the size of address on the host machine. The least significant bit (LSB) of the lock shows whether the lock is free or acquired. If the LSB is zero (free), the rest of the lock shows the time stamp of the last transaction that wrote to a memory location covered by the lock. If the LSB is one (acquired), the rest of the lock holds the address of the owner transaction. Since the lock is word-aligned, the LSB can safely represent the status of the lock (free or acquired). Figure 2.4 shows the structure of an entry of the lock table. When a transaction commits, it updates version number of all locks corresponding to the memory locations that were written by the transaction.

TL2 supports both Eager and Lazy conflict management policies. Figure 2.5 shows the pseudo code for key functions in Eager GV4. For Eager Policy the following set of operations are executed:

- At the start of a transactional section, TL2 samples the global clock and stores it in a thread local variable called *read-version* (rv).

- Then, it runs through a speculative execution and makes undo logs to restore state of the transaction in the event of failure. TL2 maintains two sets for each transaction: one

for transactional reads, called *read-set*, and the other one for transactional writes, called *write-set*. For each transactional read operation, TL2 checks consistency of the memory location to be read (line 3). TL2 compares *rv* and version field of the lock entry corresponding to the memory address. If *rv* is greater than or equal to the version field, then consistency check passes; otherwise, the consistency check fails since the memory address has been written by another transaction after current transaction has started. In addition, TL2 checks that the lock entry is free. If any of the aforementioned conditions are not met, the transaction aborts. In case of a write operation (line 9)Figure 2.6 TL2 tries to acquire the lock corresponding to that memory location at the same time. If lock acquisition is successful, the memory location will be updated immediately. If the lock is already acquired, the transaction aborts.

- At commit time (line 24), it increments the global version-clock using the atomic compare and swap (CAS) operation. Finally, TL2 goes through the *write-set* and releases acquired locks by writing the new value of the global clock in to the version field of the locks and clearing the lock bits.

- In case of abort (line 19), TL2 goes through the write-set and reverts all the changes made to the shared memory locations and releases all the locks it has acquired so far.

For read-only transactions, the process is much simpler; TL2 samples the global clock at the start of a transactional section and validates transactional read operations. For validation, TL2 checks that the read location's lock bit is clear and the timestamp in the lock field is less than the rv. If validation passes then the transaction commits; otherwise, the transaction aborts. Since there are no write operations, there is no need to increment the value of global clock.

Figure 2.3 Lock table in TL2.

Figure 2.4 Structure of an entry of the lock table.

```

TxLoad(addr) {

//if lock entry corresponding to addr is free

2

3

if (lock(addr) is free and readVersion >= lockVersion)

return (Mem[addr]);

4

5

} else

TxAbort();

6

7

}

8

9

TxStore (addr, value) {

If (lock(addr) is free ) {

10

11

Acquire(lock(addr));

12

Write value in to addr;

13

14

else {

15

TxAbort();

16

17

}

18

19

TxAbort() {

20

DropLocks();

21

RevertMemoryChanges();

22

23

24

TxCommit() {

25

DropLocks();

26

```

Figure 2.5 Pseudo code for Eager GV4.

Figure 2.6 depicts the pseudo code for Lazy GV4. In Lazy policy, the following sequence of actions is employed:

- At the start of a transactional section, TL2 samples the global clock and stores it in a thread local variable called *read-version (rv)*.

- Then, it runs the transaction speculatively. For each transactional read operation (line 1), TL2 checks consistency of the memory location to be read. TL2 compares rv with version field of the lock entry corresponding to the memory address. If rv is greater than or equal to the version field, then consistency check passes; otherwise, the

consistency check fails since the memory address has been written by another transaction after current transaction has started. In addition, TL2 checks that the lock entry is free. If any of the aforementioned conditions are not met, transaction aborts. In case of a write operation (line 9), TL2 stores the new value in a private memory and defers updating the shared memory locations to commit time.

- At commit time (line 22), TL2 acquires locks corresponding to its write-set. If lock

acquisition fails then the transaction aborts. When all locks have successfully been

acquired, then it makes the tentative changes to the memory permanent. Then, TL2

releases all the locks and increments the global version-clock using an atomic compare

and swap (CAS) operation.

- In case of abort (line 18), TL2 goes through the write-set and releases all the locks it has acquired so far.

Figure 2.6 depicts the pseudo code for main functions of GV4.

```

1

TxLoad(addr) {

2

//if lock entry corresponding to addr is free

3

if (lock(addr) is free and readVersion >= lockVersion)

4

return (Mem[addr]);

5

} else

6

TxAbort();

7

}

8

TxStore (addr, value) {

10

If (lock(addr) is free ) {

11

Add the value to write-set

12

}

13

else {

14

TxAbort();

15

16

}

17

18

TxAbort() {

19

DropLocks();

20

21

22

TxCommit() {

23

AcquireLockForWrite-Set():

24

MakeTentativeChangesPermanent();

25

DropLocks()

26 }

```

Figure 2.6 Pseudo code for Lazy GV4.

TL2 reduces cost of validation relative to those STMs that require rescanning of the read-set on every transactional load [30]. However, there are some disadvantages in TL2. The global clock creates contention since each transaction increments the clock in commit, which results in costly cache coherency invalidation traffic. Also there is an extreme condition where TL2 leads to unnecessary aborts. Consider the case where Thread 0 ( $T_0$ ) writes to a shared memory location and Thread 1 ( $T_1$ ) reads from it. Assume that  $T_0$  writes after  $T_1$  has started, but before  $T_1$  reads from the shared location. Since  $T_1$  samples the clock at the start of the transactional section, the version of shared memory location is more than rv. Therefore, validation fails and  $T_1$  aborts. However,  $T_0$  and  $T_1$  access the shared memory location at different timestamps and could have committed successfully. These unnecessary aborts waste processor resources and degrade performance.

## 2.5.2 Programming with TL2

TL2 provides several programming constructs for programmers to write transactional programs:

- 1) TM\_STARTUP (): Initializes transactional states and the internal buffers. It also initiates the lock table.

- 2) TM\_THREAD\_ENTER (): creates a new thread of execution. It also initializes the newly created thread and sets the internal state registers, read-set and write-set buffers to appropriate values. This is placed at the beginning of the parallel section of a program.

- 3) TM\_BEGIN (): Marks the beginning of a transaction. The thread saves a program's state at the start of the transactional section. If later, the transaction aborts, the state of the program is recovered.

- 4) TM\_SHARED\_READ (address): Loads shared memory value pointed by "address" into a temporary variable. This causes the memory address to be added to the read-set of the thread.

- 5) TM\_SHARED\_WRITE (address, value): Stores the "value" into the location in the shared memory pointed by "address". This causes the memory address to be added to the write-set of the thread. If eager policy is employed, the changes to the shared memory take place immediately. However, if lazy policy is employed, the changes to the shared memory are deferred until commit time.

- 6) TM\_END (): Marks the end of a transaction. The transaction either successfully commits and finished execution, or aborts and re-executes from TM BEGIN().

- 7) TM\_THREAD\_EXIT (): Deallocates memory for internal buffers of the thread. This is placed at the end of last parallel section of the code.

8) TM\_SHUTDOWN (): Called at the end of the program in order to release all the internal buffers and transactional states allocated to the transactional memory system.

```

1

#define NUM_OF_THREADS 8

long max count;

2

static int threads arg[MAX NUM OF THREADS];

3

4

void func count (void* argPtr);

long shared counter = 0; //the shared variable

5

6

int main (int arge, char* argv)

7

8

TM STARTUP (NUM OF THREADS);

9

thread start(func count, (void*)threads arg);

TM SHUTDOWN ();

10

11

return 0;

}

12

13

14

int func count()

15

16

long myId = thread getId();

long local counter = 0;

17

18

long tmp = 0;

TM THREAD ENTER ();

19

20

while (local_counter++ < max_count)

21

22

TM BEGIN();

23

tmp = (long)TM SHARED READ (shared counter);

24

TM SHARED WRITE (shared counter, tmp + 1);

25

TM END();

26

}//end of while

27

TM THREAD EXIT ();

```

Figure 2.7 A sample code using transactional memory for implementation of a counter.

Figure 2.7 shows a shared counter implemented in TM. The shared counter is incremented by each thread. When the value of the thread exceeds a limit, the program finishes. TM\_STARTUP creates the number of threads specified by the programmer (line 8) and initializes the internal data structures of TL2. Then, func\_count is passed to thread\_start() (line 9). func\_count() is a function which is executed by multiple threads concurrently. In this function, TM\_THREAD\_ENTER is called to initialize the internal state of each thread (line 19) and create the *read-set* and *write-set* for each of them. In line 22, TM\_BEGIN marks the beginning of the transactional section. In line 23, TM\_SHARED\_READ is used to read from shared\_counter. shared\_counter is a shared variable and is accessed by all transactions. So, it is necessary to protect this variable in the transactional section. In line 24, TM\_SHARED\_WRITE is called

which acquires the lock corresponding to shared\_counter. TM\_END (line 25) marks the end of transaction and causes TxCommit to be called. At the end of Transactional Section (line 27), TM\_THREAD\_EXIT() deallocates all data structures which were allocated by TM\_BEGIN. TM\_SHUTDOWN (line 10) is called at the end of the application, where all transactions terminate.

#### 2.5.3 Benchmarks

We use STAMP v0.9.10 benchmark suite [44] to evaluate our work. A brief description of the benchmarks used in our evaluations is as follows:

- **Bayes:** A Bayesian network (or a belief network) is a way of representing probability distributions for a set of variables in a concise and comprehensible graphical manner.

- **Kmeans:** K-means is a partition-based method and is arguably the most commonly used clustering technique. K-means represents a cluster by the mean value of all objects contained in it.

- **Labyrinth:** Given a maze, this benchmark finds the shortest-distance paths between pairs of starting and ending points.

- Ssca2: The Scalable Synthetic Compact Applications (Ssca2) benchmark is comprised of four kernels that operate on a large, directed, weighted multi-graph. STAMP focuses on Kernel 1, which constructs an efficient graph data structure using adjacency arrays and auxiliary arrays.

- **Vacation:** This benchmark implements a travel reservation system powered by a non-distributed database.

- **Genome:** This benchmark implements a gene sequencing program that reconstructs the gene sequence from segments of a larger gene.

#### 2.6 Summary

In this chapter, we presented background for TM systems and discussed related work. We explained details of TL2. TL2 utilizes a lock table and a novel global clock mechanism to provide the necessary functions for transactional memory. One of the limitations of the TL2 is global clock. Global clock is a central variable which is accessed by all transactions. As such, global clock restricts scalability of TL2 and increases overhead when the number of threads increases. In the next chapter, we propose TRT to alleviate the overhead of global clock and improve performance of TL2.

# Chapter 3 Transactional Read Tracking

In STMs, all transactions should have a consistent view of shared memory locations at all times [32]. Some STMs [30] use validation technique to avoid inconsistency in transactions. In this technique, STM rescans all previously read elements on every new transactional load. Validation is an expensive operation and increases overhead of the implementation and degrades performance especially in applications with frequent transactional reads [32]. An alternative approach is a global clock which is used as a timestamp for shared memory locations. While this method is simple to implement, it results in contention over the global clock, especially when transactions commit frequently. In this chapter, we introduce Transactional Read Tracking (TRT) which tracks transactional read and write operations without using a central data structure such as global clock. TRT removes the burden of the global clock and improves scalability of STMs.

The rest of this chapter is organized as follows. In section 3.1, we present the motivation behind this work. In section 3.2, we introduce TRT and explain different aspects of it. In section 3.3, the performance of TRT is reported. In section 3.4, we present a hybrid method to increase the speedup provided by the system. In section 3.5, we introduce yet another hybrid method to further increase the performance.

#### 3.1 Motivation

In time-based STMs, a transaction increments the clock when it commits. This results in broadcasting costly coherence invalidations over interconnection network and remote caches [45]. Therefore, global clock becomes a bottleneck when the number of concurrent transactions increases, even when there is no conflict among the transactions. *Transactional Read Tracking (TRT)* allows transactions to operate on consistent states without the need for a global notion of time. In TRT, each memory location is associated with a Lock. When a transaction reads a memory location, it sets a dedicated bit in the corresponding lock entry, indicating that the memory location has been read by a transaction. When a transaction writes into a memory location, it checks the read bits of the corresponding lock entry. If all read bits are zero and the lock has not been acquired, the write operation is successful and the thread continues; otherwise,

the thread has to abort. Hence, TRT maintains atomicity of transactions and validates transactional data without using a global clock.

# 3.2 Transactional Read Tracking

In this section, we explain details of TRT and discuss how TRT is implemented in software. Similar to GV4, TRT relies on locks to synchronize accesses to the shared memory locations. Figure 3.1 depicts the structure of a single lock entry in TRT. Each lock consists of a lock bit and a set of read bits. The lock bit indicates whether the corresponding memory location is locked by a transaction. When a transaction writes to a memory location it sets the corresponding lock bit. Read bit i corresponds to thread i and indicates whether thread i has read from the memory location. When thread i reads from a memory location it sets read bit i of the corresponding lock. The record of all transactional loads and stores is kept in two sets of logs: read-set and write-set.

Figure 3.1 Structure of a single lock entry in TRT.

In TRT, the following set of operations is performed when a writing transaction executes:

• Run transactional code: Execute the transactional code, meanwhile, each time a shared memory location is accessed, the lock entry associated with the memory location is checked. For transactional read operations, if the lock is free, the lock is sampled into the thread's local *read-set* and the corresponding read bit in the lock is set using atomic Compare and Swap (CAS) operation [18]; if the lock is already acquired by another transaction then the current transaction aborts. For transactional write

operations, if the corresponding lock is free and all read bits are clear, then the lock is acquired using CAS. If the lock is already acquired, then two transactions conflict over a shared memory location. The one which acquires the lock sooner is the winner and writes into the shared memory location. The other should abort and restart its transactional section. If a read bit is set, then the writing transaction aborts. This is necessary to guarantee atomicity of transactional sections.

- Commit: When a transaction reaches the commit step, its transactional data are valid. The transaction requires clearing the read bits in the lock entries corresponding to its read-set. In addition, lock entries corresponding to its write-set should be dropped by clearing the lock bits.

- **Abort:** If a transaction needs to be aborted, it should revert all changes that it has made to the shared memory locations. The thread goes through *write-set* and undoes all write operations and clears the lock bits. Also, the transaction should clear its read bits in the lock entries corresponding to its *read-set*.

Figure 3.2 presents the pseudo code for TRT. When a transaction reads from an address in memory (TxLoad()), the corresponding lock is examined to ensure that it has not been acquired by another transaction (line 2). Then, it sets the read bit *i* to indicate that a transaction in thread *i* has read from the address (line 3). When a transaction writes into a memory location (TxStore()), it checks the lock entry corresponding to input address (line 10). If no other transaction has read/written from/to the address, then the lock entry is acquired (line 11) and the new value is written into the memory (line 12); otherwise, the transaction aborts (line 15). When a transaction aborts (TxAbort()), it goes through all nodes of its read-set and write-set to restore the state of the lock table (lines 20-21). In addition, all new values written to memory by TxStore() should be reverted (line 22). When a transaction commits (TxCommit()), all read bits of lock entries corresponding to read memory locations (line 26) and all lock bits corresponding to written memory locations should be cleared (line 27). However, contrary to TxAbort(), there is no need to revert the changes to the memory. Appendix A has the source code for TRT.

### 3.2.1 Proof of Correctness:

In this section, we prove that TRT algorithm maintains the atomicity and correctness of programs. The values resulting from any serial execution of transactions are assumed to be consistent. A parallel program is considered consistent, if a serial execution of transactions exists, and that generates the same result as the parallel program. Two concurrent transactions are defined as conflicting when they access the same memory location and at least one of them

writes to that location (Read-After-Write, Write-After-Read, and Write-After-Write hazard). Since TRT allows a thread to write to a memory location only if the location has not been read or written by any other thread, any of the aforementioned hazards will not happen. For transactional read operations, any number of threads can read a location as long as it has not been written by another transaction.

In term of atomicity, the key difference between GV4 and TRT is that TRT uses the first transactional read or write operation as the linearization point while GV4 uses the start of a transactional section as the linearization point. Hence, TRT, in contrast to GV4, does not generate unnecessary aborts as discussed in section 2.5.1.

```

1

TxLoad(addr) {

2

if ( lock(addr) is free ) //if lock entry corresponding to addr is free

3

set read bit in lock(addr);

4

return (Mem[addr]);

5

} else

6

TxAbort();

7

}

8

9

TxStore (addr, value) {

10

If (all read bits of lock(addr) are zero and lock(addr) is free ) {

11

Acquire( lock(addr) );

12

Write value in to addr:

13

14

else {

15

TxAbort();

16

}

17

18

19

TxAbort() {

20

RevertReadSetChanges();

21

DropLocks();

22

RevertMemoryChanges();

23

}

24

25

TxCommit() {

26

RevertReadSetChanges();

27

DropLocks();

28 }

Figure 3.2 Pseudo code for TRT.

```

#### 3.3 Performance of TRT

In this section, we report performance of TRT. All tests were carried out on two Intel Xeon E5660 processors running at 2.8 GHz. Each processor has six cores and is capable of running up to 12 threads simultaneously. Each processor has a 12MB shared L3 cache with 64B cache lines. Each core has a 32KB instruction cache and a 32KB data cache. TABLE 3.1 presents the input arguments used for STAMP benchmarks.

TABLE 3.1 Input arguments for STAMP benchmarks

| Benchmarks | Input Parameters                                  |

|------------|---------------------------------------------------|

| Bayes      | -v32 -r4096 -n10 -p40 -i2 -e8 -s1                 |

| Kmeans     | -m15 -n15 -t0.00001 -i inputs/random-n65536- d32- |

|            | c16.txt                                           |

| Labyrinth  | -i inputs/random-x512-y512-z7-n512.txt            |

| Ssca2      | -s20 -i1.0 -u1.0 -l3 -p3                          |

| Vacation   | -n4 -q60 -u90 -r1048576 -t4194304                 |

| Genome     | -g16384 -s64 -n16777216                           |

Figure 3.3 presents performance of TRT relative to GV4 in STAMP v0.9.10 benchmarks. The results were normalized to the execution time of GV4; hence bars less than 1 show performance improvement. For each benchmark, the number of threads varies between two and 16. While in some benchmarks, TRT is faster than GV4 on average, i.e. Labyrinth, GV4 works better than TRT in some others, i.e. Kmeans. The main reason that TRT falls behind GV4 in some benchmarks is associated with overhead of abort. In TRT, when a transaction aborts it traverses both *read-set* and *write-set* and reverts all the changes made to the lock table. Depending on the application's data access patterns, *read-set* or *write-set* might grow largely. However, GV4 has to check only its *write-set*. This causes extra overhead in some benchmarks and degrades performance.

To provide better insight into the overhead of abort in TRT, part of a code region taken from Genome is shown in Figure 3.4. TRT degrades performance of Genome by 83% when the number of threads is 16. This is the maximum slowdown across STAMP benchmarks. More than 79% of total aborts happen in the transaction shown in Figure 3.4. In previous parts of the code (not shown in the Figure), the algorithm removes duplicate segments using hash-set and in this specific part, it iterates over unique segments and computes hashes. Hashes are implemented as

Figure 3.3 Speedup in TRT relative to GV4.

linked-lists and in function TMTABLE\_INSERT(), all threads compete to insert nodes into the hashes. Hence, transactions create large *read-sets* and they try to write in one of them. This results in dramatic increase in read-write conflicts and the "for loop" in the program exacerbates this situation.

In the next section, we introduce RGVT which alleviates the overhead of abort and improves performance of TRT.

```

for (j = 1; j < segmentLength; j++) {

...

TM_BEGIN();

status = TMTABLE_INSERT(startHashTables[j], ...);

TM_END();

...

}</pre>

```

Figure 3.4 Part of Genome program from STAMP v0.9.10 benchmark suite.

# 3.4 rwConflict Based GV4-TRT (RGVT)

TRT and GV4 have conflicting effects. While GV4 reduces overhead of abort, it unnecessarily serializes transactions and increases contention over the central global clock even if transactions do not conflict. On the other side, TRT eliminates cost of global clock but increases overhead of abort and introduces read-write conflicts. Hence, none of the two validation policies works well

across all applications. Depending on access pattern of shared data structures in a benchmark, one method may work better than the other.

#### 3.4.1 Read-Write Conflict

One way to combine the best of TRT and GV4 is selecting one of the two techniques based on number of read-write conflicts. We count the number of read-write conflicts and store it in a local variable: rwConflict. If rwConflict is more than a pre-determined threshold, GV4 is the preferred scheme since TRT increases execution time due to overhead of abort. If rwConflict is less than the threshold, then the preferred validation scheme is TRT since GV4 unnecessarily serializes the committing transactions.

The reason for switching between GV4 and TRT based on read-write conflicts is that the number of read-write conflicts greatly affects the performance of TRT. If this number grows, it results in a large read-set and the likelihood of conflict is high. Aborting a transaction with a large read-set is a costly operation which degrades performance. It is worthwhile to mention that if the read-set size grows without creating conflict, TRT will provide acceptable speedup with respect to GV4.

To prevent change of validation scheme at the middle of a transaction, we use read-write lock [8] to synchronize transactions. Only one thread is allowed to change the validation scheme (i.e. thread zero). When a transaction in thread zero decides to change the validation scheme, it acquires the lock in write-mode, changes the granularity, and releases the lock. All the other transactions acquire the lock in read-mode at the start of transactional sections and release the lock when they commit or abort. Using the read-write lock, we guarantee that the validation scheme changes only when there is no running transaction.

### 3.4.2 Performance of RGVT

Figure 3.5 presents the performance of RGVT relative to GV4. The value of threshold is set to 10 and is used across all applications. We examined different values for threshold and found that threshold of 10 results in maximum speed-up. On average, RGVT improves performance across all benchmarks. Performance of Genome is considerably improved. Genome has a mixed structure: read-write conflicts are frequent in parts of the benchmark and in the other parts, they occur rarely. RGVT manages to utilize GV4 for the conflicting parts and TRT for the non-

conflicting parts. As such, RGVT improves performance of Genome for all variations of number of threads. For Labyrinth and Ssca2, TRT and RGVT are similar. In these two benchmarks, readwrite conflicts occur rarely and so, RGVT quite often chooses TRT as the validation scheme. Kmeans and Vacation are not sensitive to the validation policies and so speedup of both TRT and RGVT are marginal. Bayes, similar to Genome, has a mixture of high and low read-write conflict transactions. RGVT adjusts validation policy dynamically and improves performance of Bayes over all variations of number of threads.

Figure 3.5 Performance of RGVT using rwConflict.

To provide better insight into RGVT, in Figure 3.6, we report how often transactions execute in GV4 and TRT modes. For each benchmark, the number of threads varies from two to 16. In Bayes, Labyrinth and Ssca2, virtually all transactions execute in TRT mode, which confirms the results presented in Figure 3.5, since speedup in these benchmarks is significant. In Genome, TRT is chosen as the initial validation method. When the size of the *read-set* and *write-set* grows the rate of read-write conflict increases. As such, *rwConflict* exceeds the threshold and RGVT selects GV4 for validation to avoid costly aborts. In Kmeans, quite often, GV4 is selected for validation. Therefore, sometimes there is performance degradation in this benchmark. This shows that *rwConflict* is not very accurate in predicting applications' behaviour. In the next section, we discuss a different technique to switch between GV4 and TRT.

Figure 3.6 Frequency of GV4 and TRT in RGVT.

# 3.5 Perceptron GV4-TRT (PGVT)